没有合适的资源?快使用搜索试试~ 我知道了~

在本设计的软件流程详见系统框图由于模块很多所以在此(完整版).doc

1 下载量 125 浏览量

2022-12-03

11:39:29

上传

评论

收藏 2.1MB DOC 举报

温馨提示

试读

12页

在本设计的软件流程详见系统框图由于模块很多所以在此(完整版).doc

资源推荐

资源详情

资源评论

在本设计的软件流程详见系统

框图由于模块很多所以在此(完

整版)

(文档可以直接使用,也可根据实际需要修改使用,可编辑 欢迎下载)

1. 在本设计的软件流程详见系统框图。由于模块很多所以在此不再一一介绍。

下面是设计中的几个主要模块。其中分频模块,串并/并串模块比较简单,所以不再介绍。

信道估计模块的算法采用自己的 LS 算法。上变频 DDC 由于边频很高,所以拟采用 AD 公

司的 ad9857,如果板子上没有专用器件的话,则改成基于 FPGA 的 DDC。下边频在 FPGA

中作。

串并

变换

差分

相位

编码

LPF

LPF

放大器

码流

m

,I k

m

,Q k

m

k

I

k

Q

cos( )

c

w t

sin( )

c

w t�

( )s t

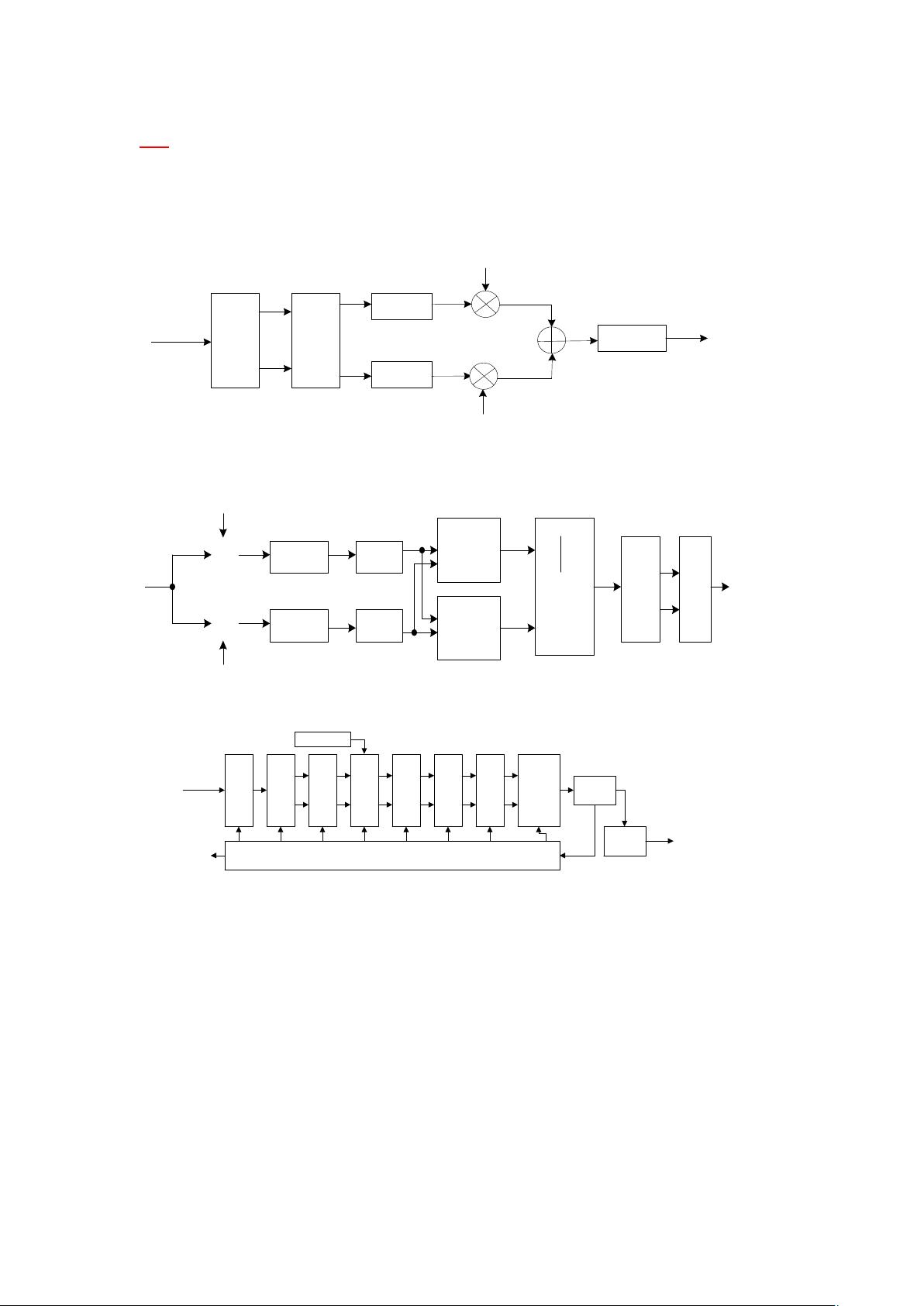

图 1 π/4-DQPSK 调制框图

�

�

coswt

sinwt

LPF

LPF

抽样

抽样

差分

相位

解码

并

串

变

换

W(t)

Z(t)

1

1

k k

k k

WW

Z Z

�

�

�

1

1

k k

k k

Z W

W Z

�

�

�

k

W

k

Z

1

( )

k

k

e

c t g

f

�

k

e

k

f

k

�

�

图 2 π/4-DQPSK 解调框图

数据

存储

模块

内插

模块

N=8

成形

滤波

模块

FPGA

与

AD9857

接口电路

基带信号

数据

截短

模块

AD9857

运放

MAX4103

时钟分频模块

系统时钟

同步

帧头

模块

差分

编码

模块

串并

变换

模块

巴克码发生器

8PSK中频信号

图 3 8PSK 调制框图和顶层原理图

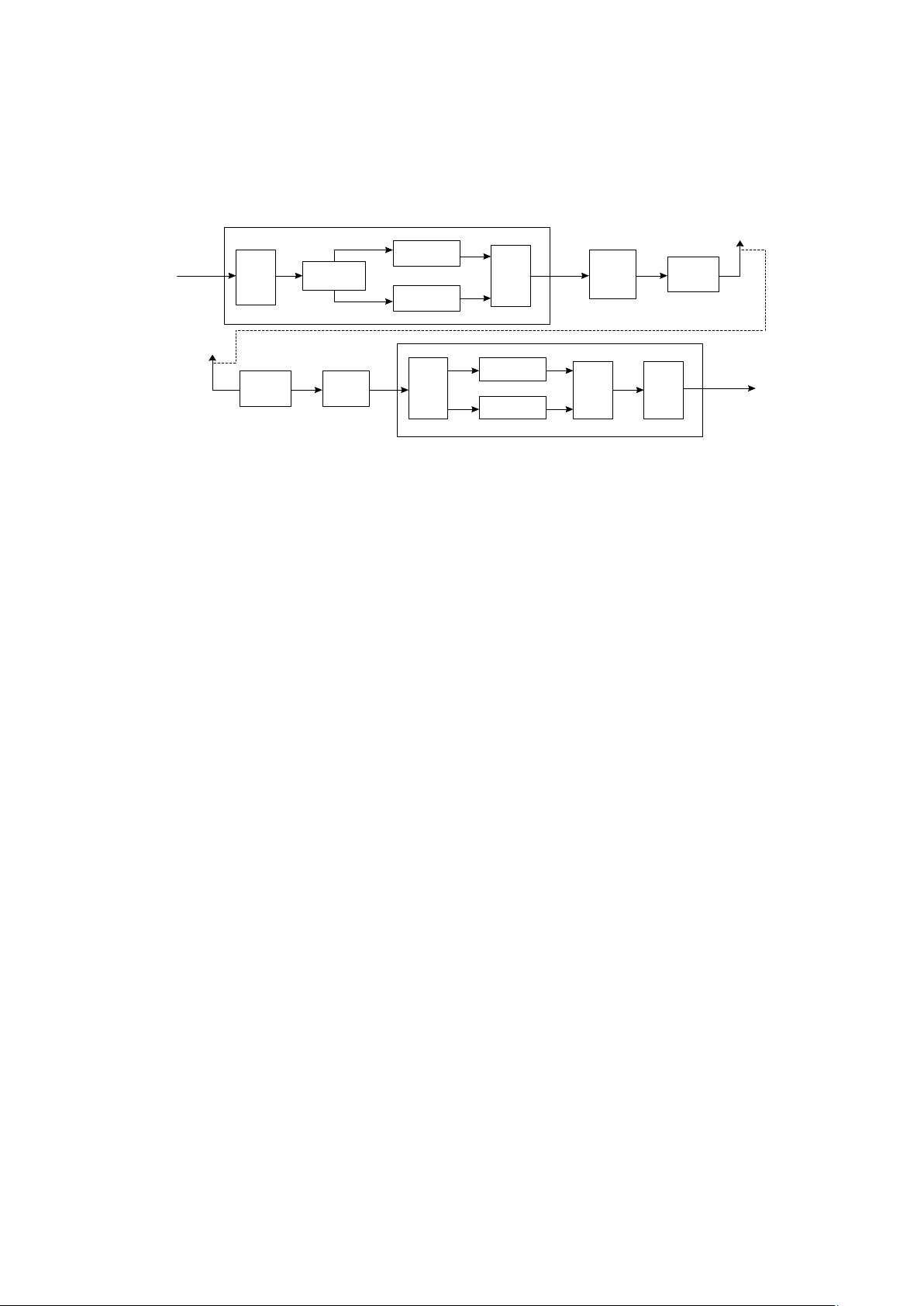

2 调制解调器的系统实现

在现代数字通信系统中,FPGA 的应用相当广泛。尤其是在对基带信号的处

理和整个系统的控制中,FPGA 不但能大大缩减电路的体积,提高电路的稳定性,

而且先进的开发工具使整个系统的设计调试周期大大缩短。本系统的核心算法也

都是在 FPGA 中实现的。

在调制端,数据首先在 FPGA 中完成信道编码(本系统中此工作也可在 DSP

中完成),然后有数据调制,分路,内插和成形滤波,信号在 AD9857 中完成直

接数字上变频和数模转换,经过运放得到带宽为 200kHz 的中频信号。

信道

编码

数据调制

成形滤波

成形滤波

并串

变换

串行数据

发FPGA

DDS

(D/A)

运算放

大器

IF

同相跟

随器

A/D

IF

DDC

匹配相关

匹配相关

数据

解调

信道

解码

收FPGA

输出数据

图 4 系统实现结构示意图

在解调端,模拟信号通过 A/D 采样器被搬移到低中频,并转化为数字信号,

再由 FPGA 中设计的 DDC 将其下变频至基带。除此以外,收端 FPGA 还需要完

成同步捕获,数据解调和信道解码,如果是相干解调还需要完成相干载波的恢复,

最后输出解调数据。

2.1 成形滤波器设计

信号的相位跳变是瞬时变化的,瞬时变化的相位会使信号频谱发生扩散,导

致需要非常大的信道带宽才能无失真地传输信号。为了把信号频谱限制在一个比

较合理的范围内,对基带信号进行滤波是必不可少的。但是基带滤波会使信号在

时域上扩展,如果设计不好将在接收端引起严重的码间干扰(ISI)。

奈奎斯特第一准则(第一无失真条件)告诉我们:如果信号经传输后整个波

形发生了变化,但只要其特定点的抽样值保持不变,那么用再次抽样的方法

仍然可以准确无误的恢复原始信号。也就是说,只要把通信系统包括发射机、

信道和接收机的整个响应设计成在接收机端每个抽样时刻只对当前的符号

有响应,而对其他符号的响应全等于 0,那么 ISI 的影响便可消除。这是对

奈奎斯特准则的时域描述。

满足奈奎斯特准则的滤波器有许多种,最简单的是理想低通滤波器。但

是这种理想的滤波器是物理不可实现的,因为实际的滤波器不可能做到垂直

截止,而且时域拖尾过长,运算时要求很高的精度且容易产生偏差。在实际

通信系统中广泛应用的成形滤波器是升余弦滤波器,这是因为它具有以下的

优点:

剩余11页未读,继续阅读

资源评论

Mmnnnbb123

- 粉丝: 679

- 资源: 8万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功