MT9V115

CONFIDENTIAL AND PROPRIETARY

NOT FOR PUBLIC RELEASE

www.onsemi.com

5

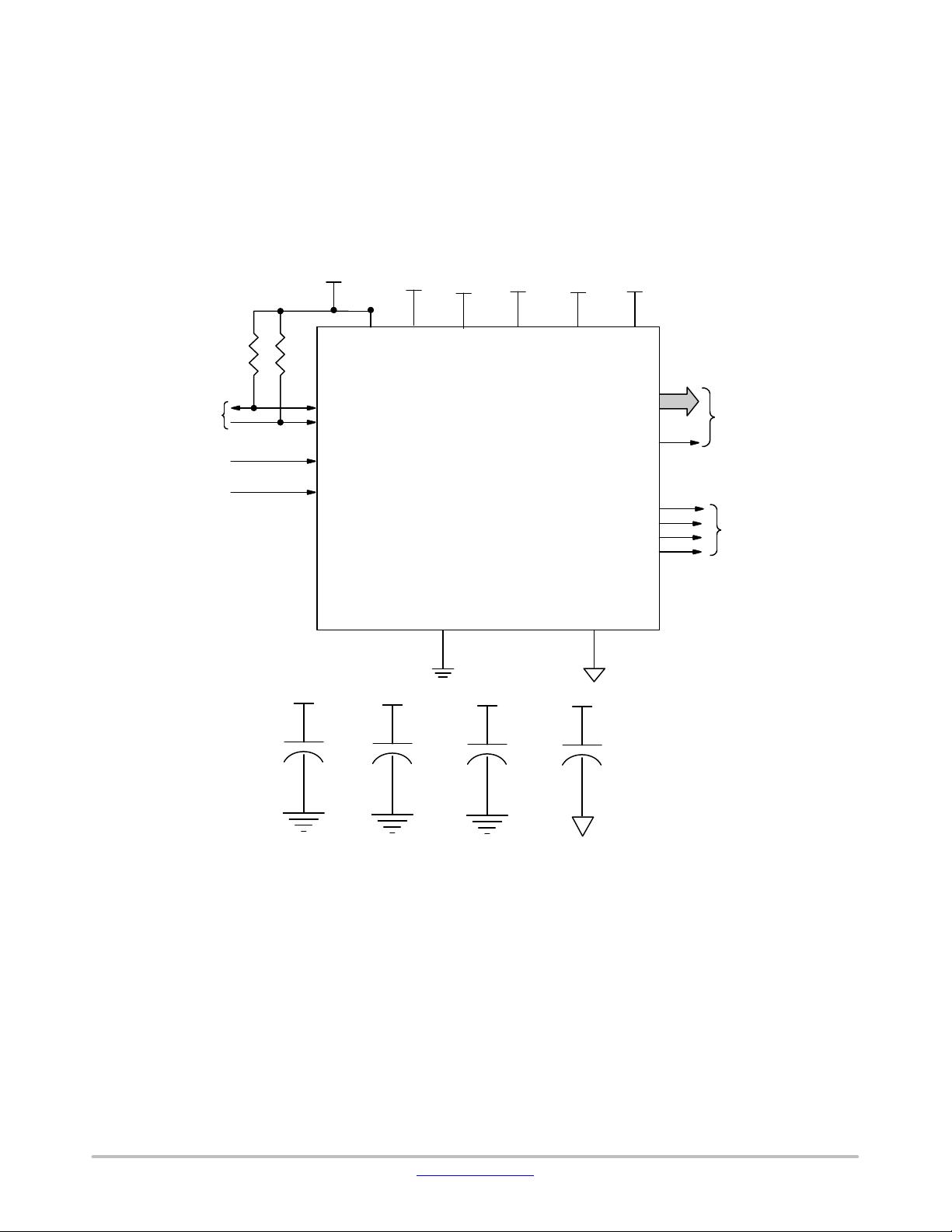

Decoupling Capacitor Recommendations

The minimum recommended decoupling capacitor

recommendation is 0.1 μF per supply in the module.

It is important to provide clean, well regulated power to

each power supply. The ON Semiconductor recommendati

on for capacitor placement and values are based on our

internal demo camera design and verified in hardware.

NOTE: Since hardware design is influenced by many

factors, such as layout, operating conditions,and

component selection, the customer is ultimately

responsible to ensure that clean power is

provided for their own designs.

In order of preference, ON Semiconductor recommends:

1. Mount 0.1 μF and 1 μF decoupling capacitors for

each power supply as close as possible to the pad

and place a 10 μF capacitor nearby off-module.

2. If module limitations allow for only six decoupling

capacitors for a three-regulator design (V

DD_PLL

tied to V

AA), use a 0.1 μF and 1 μF capacitor for

each of the three regulated supplies.

ON Semiconductor also recommends placing

a 10 μF capacitor for each supply off-module, but

close to each supply.

3. If module limitations allow for only three

decoupling capacitors, a 1 μF capacitor for each of

the three regulated supplies is preferred.

ON Semiconductor recommends placing a 10 μF

capacitor for each supply off-module but closed to

each supply.

4. If module limitations allow for only three

decoupling capacitors, a 0.1 μF capacitor for each

of the three regulated supplies is preferred.

ON Semiconductor recommends placing a 10 μF

capacitor for each supply off-module but close to

each supply.

5. Priority should be given to the V

AA supply for

additional decoupling capacitors.

6. Inductive filtering components are not

recommended.

7. Follow best practices when performing physical

layout.

Signal Descriptions

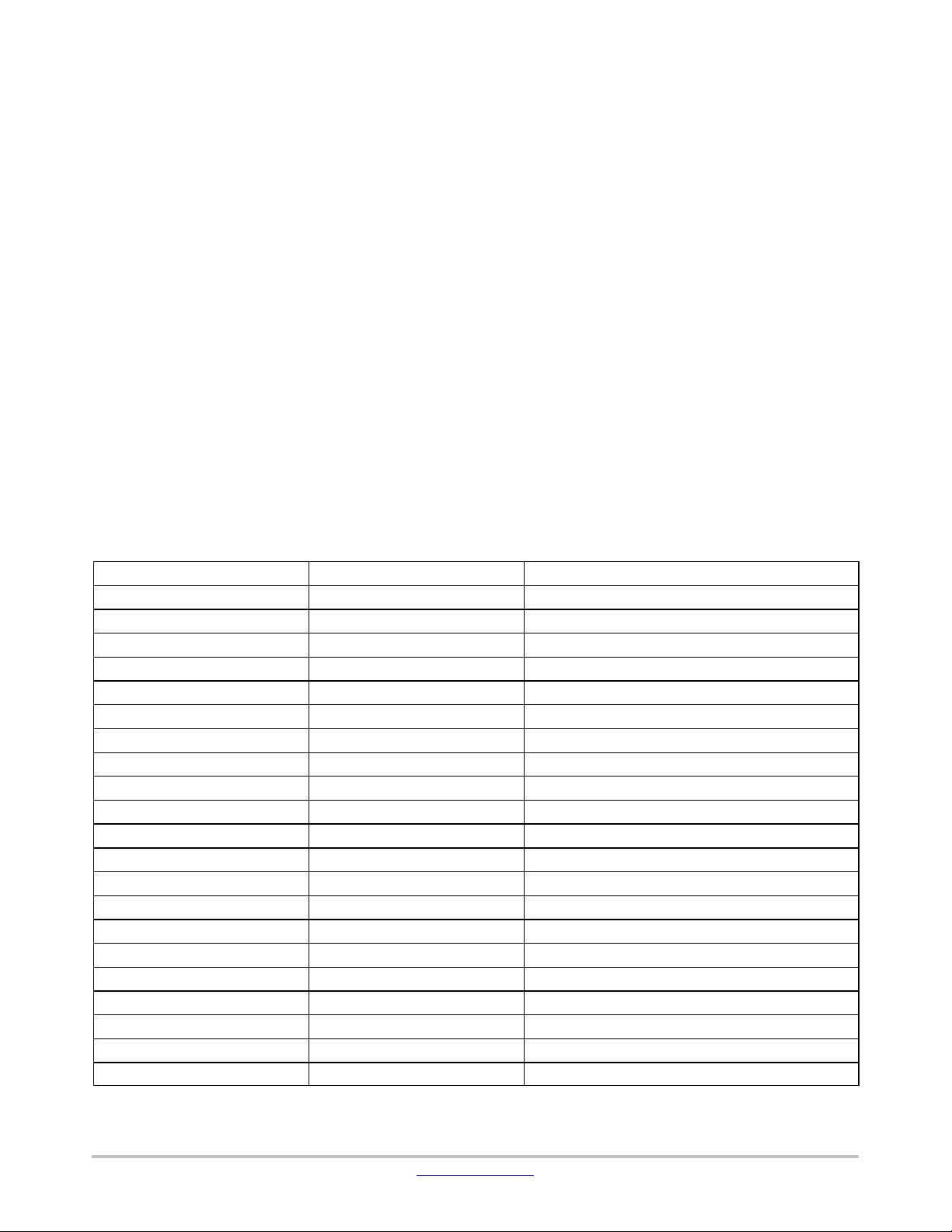

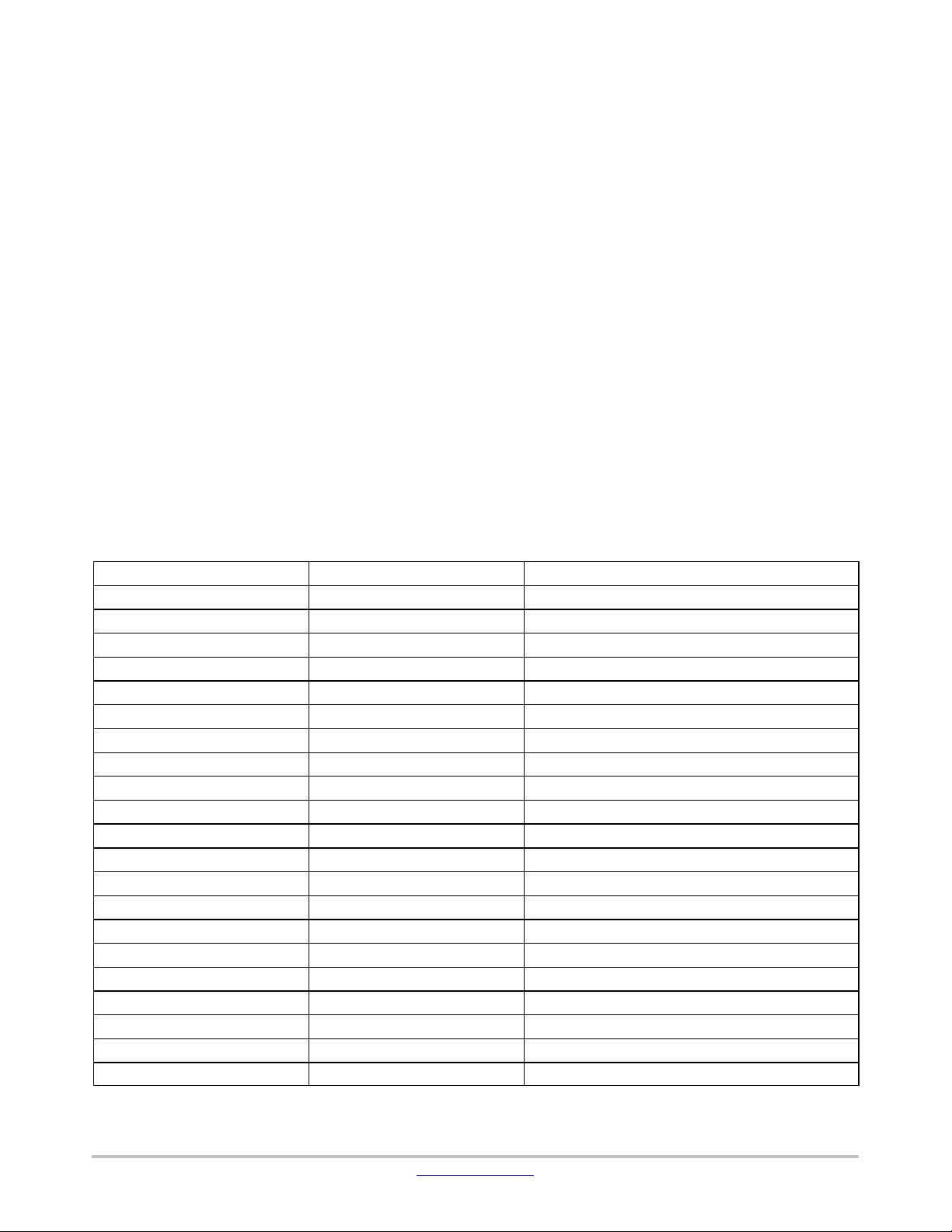

Table 3. SIGNAL DESCRIPTIONS

Name Type Description

EXTCLK Input Input clock signal

STANDBY Input Controls sensor’s standby mode, active HIGH

SCLK Input Two-wire serial interface clock

SDATA I/O Two-wire serial interface data

FRAME_VALID (FV) Output Identifies rows in the active image

LINE_VALID (LV) Output Identifies pixels in the active line

PIXCLK Output Pixel clock

DOUT[7:0] Output DOUT[7:0] for 8-bit image data output

CLK_N Output Differential MIPI clock

CLK_P Output Differential MIPI clock

DATA_N Output DATA_N Output Differential MIPI data

DATA_P Output DATA_P Output Differential MIPI data

VDD Supply Digital power

DGND Supply Digital ground

VDD_IO Supply I/O power supply

VPP Supply OTPM power supply

VDD_PLL Supply PLL power

VDD_PHY Supply MIPI power supply

GND_PLL Supply PLL ground

VAA Supply Analog power

AGND Supply Analog ground

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功