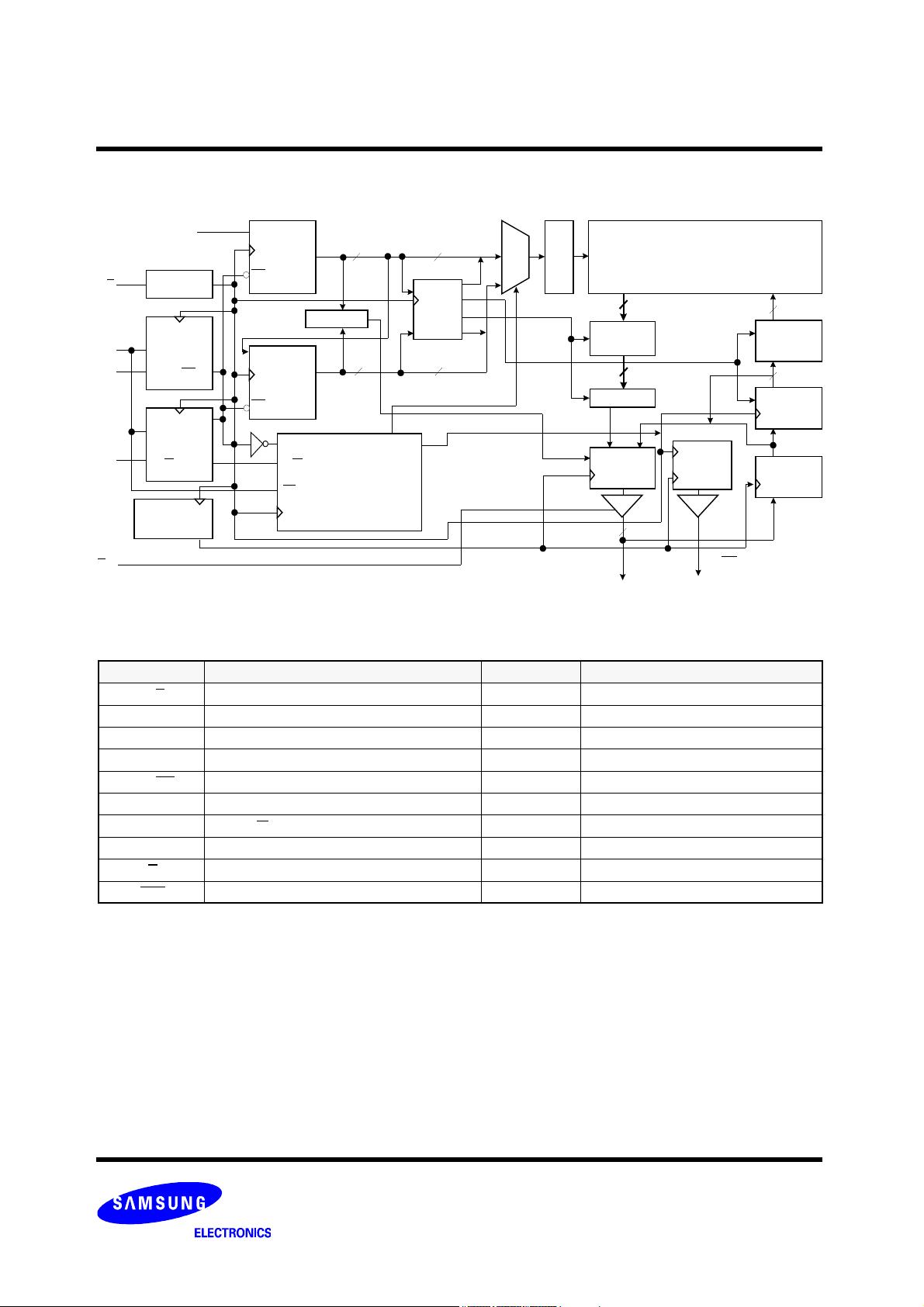

《SAMSUNG-K7D161874B.pdf》文档主要介绍了三星电子生产的两款同步双倍速率SRAM芯片——K7D161874B和K7D163674B。这两款芯片是高性能的存储解决方案,采用先进的CMOS工艺制造。 1. **产品概述** K7D163674B和K7D161874B是18,874,368位的同步管道突发模式SRAM器件。它们分别以524,288字×36位(K7D163674B)和1,048,576字×18位(K7D161874B)的组织形式提供。这种设计适用于需要高速数据处理和高存储容量的应用场景。 2. **技术规格** - **工作电压**:支持1.8V到2.5V的VDD工作电压范围。 - **电流特性**:在Rev 1.1版本中,对于x36配置,操作电流增加了40mA;对于x18配置,操作电流增加了60mA。此外,Stop Clock Standby电流ISB1从100mA增加到150mA。 - **JTAG接口**:Rev 1.1更新了JTAG指令编码,对预留的JTAG指令进行了调整。 - **输入定义**:文档新增了VIN-CLK、VDIF-CLK和VCM-CLK的直流特性,并添加了交流输入特性。 3. **操作频率** K7D163674B和K7D161874B有不同的操作频率选项,如HC375对应375MHz、HC333对应333MHz、HC303对应300MHz和HC27对应275MHz,这允许用户根据系统需求选择合适的速度等级。 4. **时序特性** 两款芯片都使用单差分HSTL(High-Speed Transceiver Logic)级别时钟K和K',在时钟K的上升沿,地址和突发控制输入被注册,所有内部操作都是自定时的,确保了高效的同步操作。 5. **订购信息** 芯片的订购型号与最大工作频率相关,例如,K7D163674B-HC375表示12Kx36配置,最大工作频率为375MHz。 6. **兼容性与应用** 这些SRAM芯片适用于需要高速数据传输和低延迟的系统,如高性能计算、网络设备、图形处理器和通信基础设施等。 7. **技术支持** 三星电子提供了详细的数据表,并承诺对关于该设备参数的问题进行评估和回应。用户可以通过联系三星的当地分支机构或总部获取技术支持。 总结,K7D161874B和K7D163674B是高性能的同步SRAM,具备灵活的工作电压和频率选择,适用于对速度和容量有高要求的现代电子系统。三星电子通过持续的技术更新和优化,确保了这些产品的先进性和可靠性。

剩余15页未读,继续阅读

- 粉丝: 1

- 资源: 261

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于C语言的嵌入式软件定时器详细文档+全部资料+高分项目+源码.zip

- 基于ffmpeg的直播推流器,超级稳定,经过长时间稳定性测试,超低延时,可用于手机,电视,嵌入式等直播App及设备。详细文档+全部资料+高分项目+源码.zip

- 基于DCT算法的水印嵌入和提取的移动智能终端数字图像证据系统详细文档+全部资料+高分项目+源码.zip

- 基于FPGA的DDR1控制器,为低端FPGA嵌入式系统提供廉价、大容量的存储详细文档+全部资料+高分项目+源码.zip

- 基于FreeRTOS开发的嵌入式开发框架详细文档+全部资料+高分项目+源码.zip

- 基于FMCW雷达的多天线定位系统详细文档+全部资料+高分项目+源码.zip

- 基于FriendlyARM6410平台的嵌入式Qt程序:实时天气信息,远程vnc控制,远程监视摄像头,语音控制,语音输出TTS详细文档+全部资料+高分项目+源码.zip

- 基于FSMPSTem32的嵌入式音乐播放器、实训作业详细文档+全部资料+高分项目+源码.zip

- 基于GEC6818嵌入式大作业详细文档+全部资料+高分项目+源码.zip

- 基于jetty嵌入式容器的java性能分析工具,内嵌H2 database,以图表形式直观展现应用当前性能数据详细文档+全部资料+高分项目+源码.zip

- 基于jq开发的数学公式插件,可随意嵌入web中详细文档+全部资料+高分项目+源码.zip

- 基于Linux系统的应用程序,旨在搭建一套完整的多进程多线程通讯的消息框架. 支持多SOC的嵌入式APP详细文档+全部资料+高分项目+源码.zip

- 基于mplayer的嵌入式音视频播放器详细文档+全部资料+高分项目+源码.zip

- 基于LSM-Tree的嵌入式数据库详细文档+全部资料+高分项目+源码.zip

- 基于liunx下的一个QT程序,KTV点歌系统嵌入式设备详细文档+全部资料+高分项目+源码.zip

- 基于MySQL的嵌入式Linux智慧农业采集控制系统详细文档+全部资料+高分项目+源码.zip

信息提交成功

信息提交成功