CMOS SRAMKM681000E Family

Revision 1.01

December 1999

2

128Kx8 bit Low Power CMOS Static RAM

GENERAL DESCRIPTION

The KM681000E families are fabricated by SAMSUNG′s

advanced CMOS process technology. The families support

various operating temperature ranges and have various pack-

age types for user flexibility of system design. The families

also support low data retention voltage for battery back-up

operation with low data retention current.

FEATURES

• Process Technology: TFT

• Organization: 128Kx8

• Power Supply Voltage: 4.5~5.5V

• Low Data Retention Voltage: 2V(Min)

• Three state output and TTL Compatible

• Package Type: 32-DIP-600, 32-SOP-525,

32-TSOP1-0820F

PIN DESCRIPTION

Name Function

CS1, CS2 Chip Select Input

OE Output Enable Input

WE Write Enable Input

I/O1~I/O8 Data Inputs/Outputs

A0~A16 Address Inputs

Vcc Power

Vss Ground

N.C. No Connection

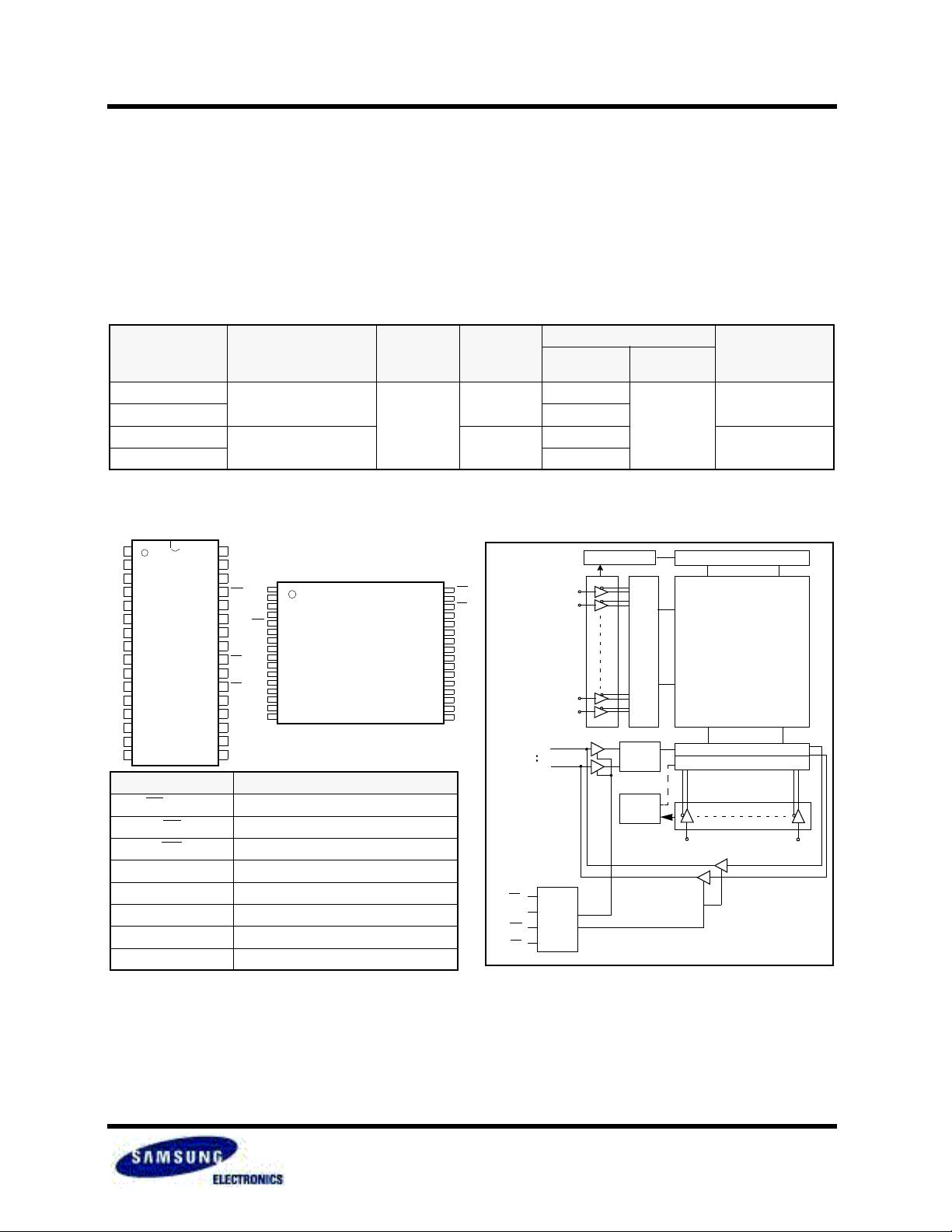

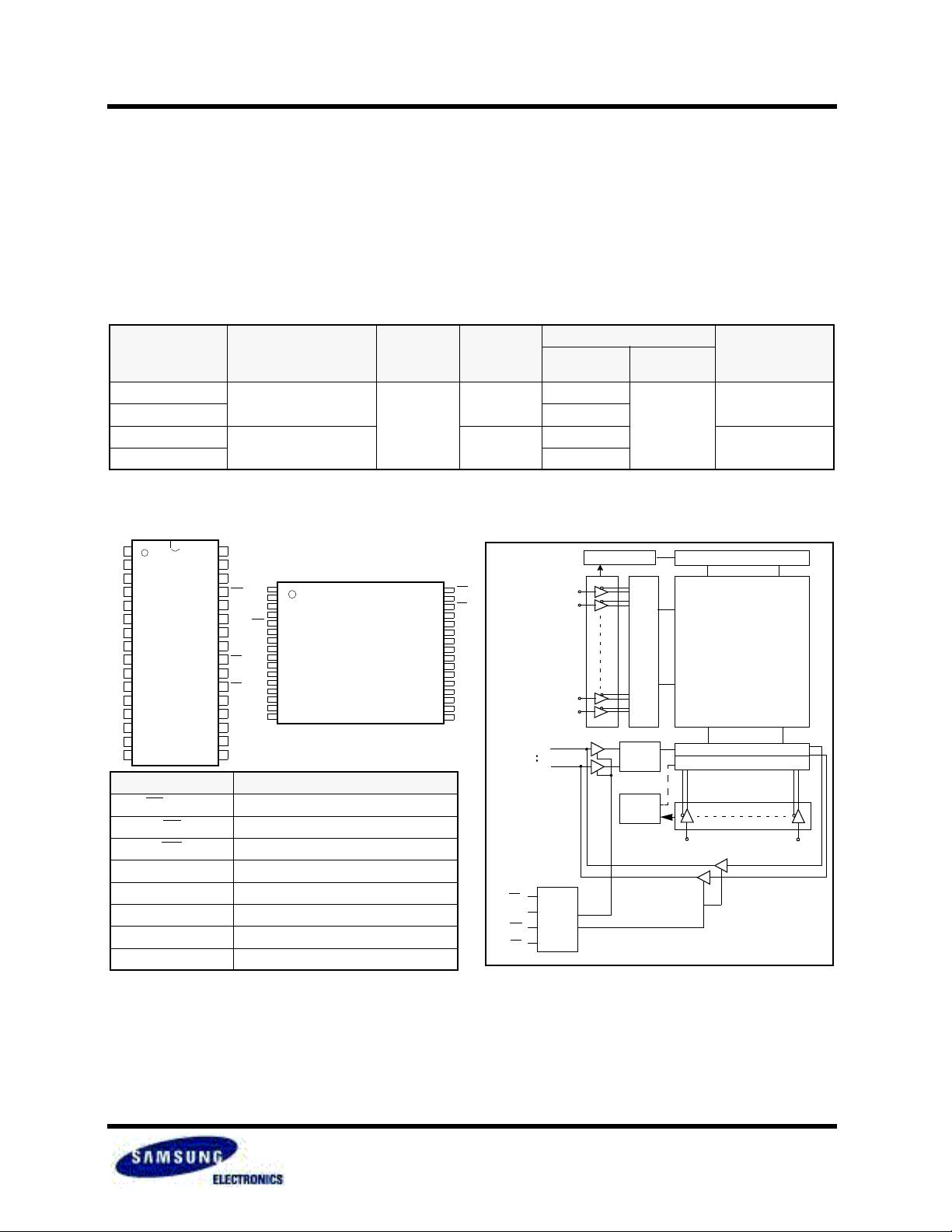

PRODUCT FAMILY

1. The parameters are tested with 50pF test load

Product Family Operating Temperature Vcc Range Speed

Power Dissipation

PKG Type

Standby

(ISB1, Max)

Operating

(ICC2, Max)

KM681000EL

Commercial(0~70°C)

4.5~5.5V

55

1)

/70ns

50µA

50mA

32-DIP, 32-SOP

32-TSOP1-0820F

KM681000EL-L 10µA

KM681000ELI

Industrial(-40~85°C) 70ns

50µA

32-SOP -525

32-TSOP1-0820F

KM681000ELI-L 15µA

FUNCTIONAL BLOCK DIAGRAM

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

Precharge circuit.

Memory array

1024 rows

128×8 columns

I/O Circuit

Column select

Clk gen.

Row

select

I/O1

Data

cont

Data

cont

I/O8

CS1

WE

OE

CS2

Control

logic

A11

A9

A8

A13

WE

CS2

A15

VCC

NC

A16

A14

A12

A7

A6

A5

A4

OE

A10

CS1

I/O8

I/O7

I/O6

I/O5

I/O4

VSS

I/O3

I/O2

I/O1

A0

A1

A2

A3

Type1-Forward

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

N.C

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

VSS

VCC

A15

CS2

WE

A13

A8

A9

A11

OE

A10

CS1

I/O8

I/O7

I/O6

I/O5

I/O4

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32-DIP

32-TSOP

32-SOP

Column Address

Raw

Address