Xilinx FPGA设计基础(VHDL版).pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

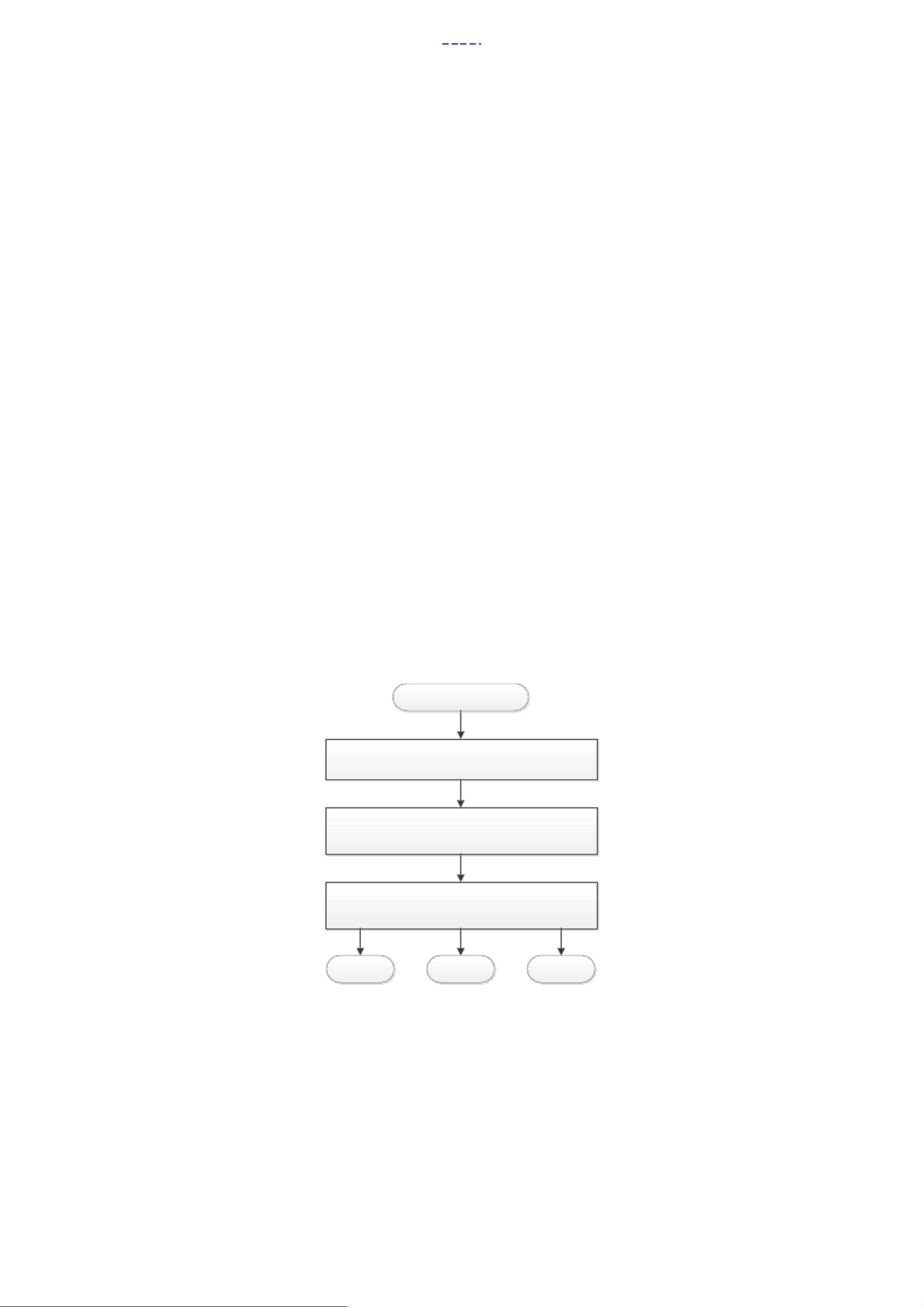

【Xilinx FPGA设计基础(VHDL版)】的章节涵盖了FPGA开发的多个核心环节,主要涉及了设计输入、设计综合、功能仿真、工程实现、时序仿真以及器件配置等步骤,使用的工具主要包括ISE(Integrated Software Environment)以及相关的约束文件(UCF)、综合工具(XST)和仿真软件。 设计输入阶段,开发人员可以采用文本或图形化方式来输入设计。通过Design Utilities创建原理图符号,方便添加和管理元件。用户约束文件(UCF)的编写至关重要,它用来指定信号的管脚位置(NET “<Signal Name>〞 LOC = <Pin Name>;)以及设置时钟约束(如NET “<Net Name>〞 PERIOD = period {HIGH/LOW}[high or low time])。 设计综合(Synthesize)是将HDL(硬件描述语言)代码转化为实际逻辑电路的过程。XST工具将VHDL代码转换为Xilinx特有的NGC网表文件,该文件包含了逻辑数据和约束信息。综合器会进行一系列优化,例如状态机的独立分析、资源共享和时序优化。综合完成后,会根据XST约束文件(XCF)对结果进行进一步优化。 功能仿真(Simulation->behavioral)用于初步验证设计的功能正确性。在这个阶段,仿真软件将HDL代码转换为逻辑电路模型,忽略信号延迟,通过Test Bench文件对各种输入条件进行测试,以确保设计满足预期的输出。 工程实现包括Translate、Map、Place and Route和Generate Programming File四个步骤。Translate将NGC和UCF合并到PCF文件中,Map将设计映射到FPGA的特定资源,Place and Route进行布局布线以满足时序约束,最后Generate Programming File生成用于器件编程的比特流文件。 时序仿真(Simulation->PostRoute)考虑了实际电路中的延迟,提供更精确的性能预测。关键参数包括时钟周期、端口到建立时间、时钟到端口时间和端口到端口时间,这些参数在约束文件中设定以确保设计满足实时性要求。 在了解了基本流程后,VHDL作为硬件描述语言,被用于描述FPGA设计的四个层次:行为层次、存放器传输层次、逻辑门层次和布图层次。行为层次关注功能描述和仿真,存放器传输层次关注综合电路实现,逻辑门层次处理门级电路设计,而布图层次则关注如何在FPGA资源中布局布线。 理解和掌握这些知识点对于进行Xilinx FPGA的开发至关重要,从设计输入、综合、仿真到实现和配置,每个环节都影响着最终设计的性能和可靠性。熟练使用VHDL语言和相应的工具链是成为一名成功的FPGA开发者的基础。

- 粉丝: 6871

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- HTML-CSS-JS学习-01百度登录界面练习.zip

- 毕业设计:基于SpringBoot的网上订餐系统,前后端分离,含支付功能-1.zip

- selective-scan-cuda.cp310-win-amd64.pyd

- 计算机二级 NCRE2 Python 练习题 .zip

- 基于springboot+vue的物业管理系统,采用前后端分离模式实现.zip

- springboot教学资源库(代码+数据库+LW)

- java课程设计作业:基于Java的打地鼠小游戏.zip

- causal-conv1d-cuda.cp310-win-amd64.pyd

- 全国计算机等级考试二级python的学习笔记(适用2020年).zip

- 机器学习(大模型):GPT大型语言模型辅助训练数据集

信息提交成功

信息提交成功