没有合适的资源?快使用搜索试试~ 我知道了~

定时器VHDL设计.pdf

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 186 浏览量

2023-04-03

15:38:40

上传

评论 1

收藏 1.06MB PDF 举报

温馨提示

试读

26页

定时器VHDL设计.pdf定时器VHDL设计.pdf定时器VHDL设计.pdf定时器VHDL设计.pdf定时器VHDL设计.pdf定时器VHDL设计.pdf

资源推荐

资源详情

资源评论

定时器 VHDL 设计

定时器

1、实验任务

设计要求:整体清零;可以定时最高到 99min;以秒速度递增至预定时间,以分速度递减至

零。

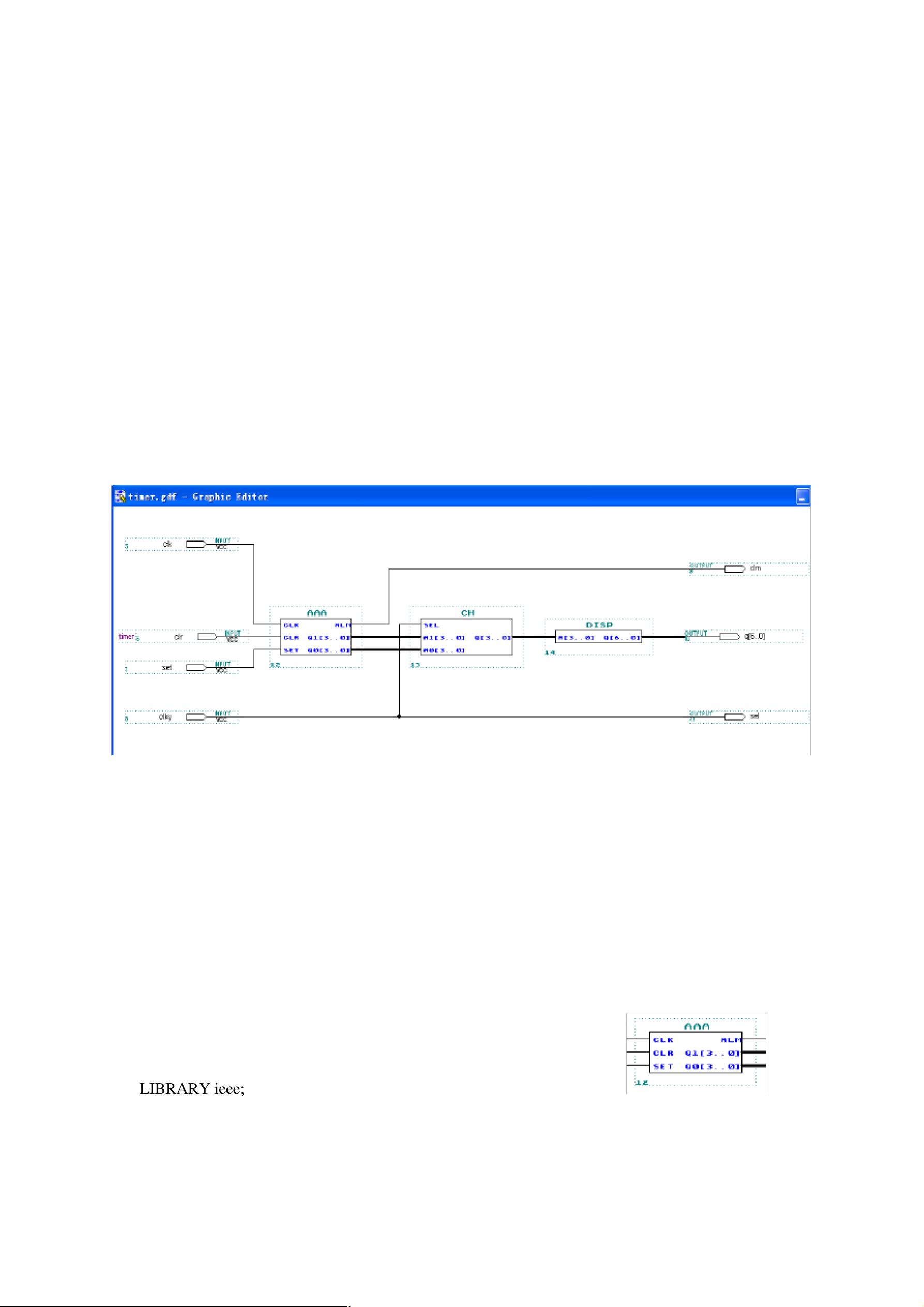

总体框图如下图所示:

clr 用来整体复位清零;clk 提供了秒信号,频率为 1HZ(在仿真中取 10MHZ);clky 就是用

来扫描输出的,选用频率大于 50HZ 的方波(为便于观察结果,在仿真中取 10MHZ);set 就是用

来置位的,低电平时有效,将以秒的速度,从零递增到所需定时的时间,为高电平时以分的速度

递减,实现定时,直到零,定时结束;alm 输出高电平,可启动各种电路或发出警报。时间的变化

都将在数码管上显示出来。

2、模块及模块功能

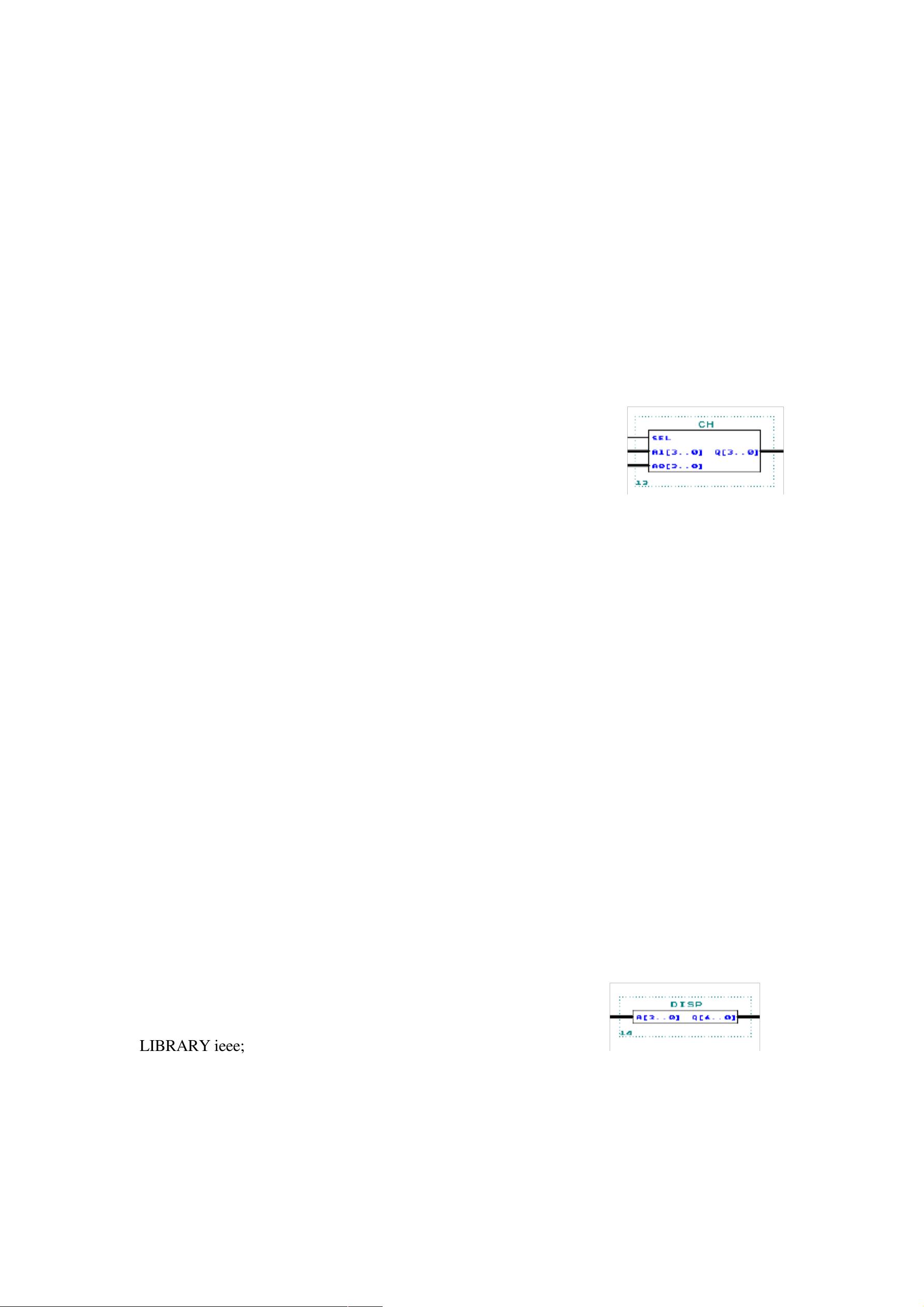

模块 AAA 见下图示。它就是核心模块,用来实现定时器的逻辑功能,计数结果用十进制

数输出。

LIBRARY ieee;

USE ieee、std_logic_1164、all;

USE ieee、std_logic_unsigned、all;

ENTITY aaa IS

定时器 VHDL 设计

PORT(clk, clr, set: in std_logic;

alm: out std_logic;

q1,q0: out std_logic_vector(3 downto 0));

END aaa;

ARCHITECTURE aaa_arc OF aaa IS

BEGIN

PROCESS (clk,clr)

variable cnt1,cnt0:std_logic_vector(3 downto 0);

variable cnt: integer range 0 to 59;

BEGIN

IF clr='0' THEN --整体复位

alm<='0';

cnt:=0;

cnt1:="0000";

cnt0:="0000";

ELSIF clk'EVENT AND clk='1' THEN --设计数初值

IF set='0' THEN

cnt:=0;

IF cnt0<"1001" THEN

cnt0:=cnt0+1;

ELSE

cnt0:="0000";

IF cnt1<"1001" THEN

cnt1:=cnt1+1;

ELSE

cnt1:="0000";

END IF;

END IF;

ELSE

IF cnt<59 THEN --60 分频

cnt:=cnt+1;

ELSE

cnt:=0;

IF cnt0>"0000" THEN

cnt0:=cnt0-1;

IF cnt1="0000" AND cnt0="0000" THEN --判断计时就是否结束

alm<='1';

END IF;

ELSE

cnt0:="1001";

IF cnt1>"0000" THEN

cnt1:=cnt1-1;

ELSE

cnt1:="1001";

定时器 VHDL 设计

END IF;

END IF;

END IF;

END IF;

END IF;

q0<=cnt0;

q1<=cnt1;

END PROCESS;

END aaa_arc;

模块 CH 如下图示。由于只用了两个数码管,所以片选信号直接接一个较快的时钟。此

模块的功能就是对应片选信号,送出要显示的数据。

LIBRARY ieee;

USE ieee、std_logic_1164、all;

ENTITY ch IS

PORT(sel:in std_logic;

a1,a0:in std_logic_vector(3 downto 0);

q:out std_logic_vector(3 downto 0));

END ch;

ARCHITECTURE ch_arc OF ch IS

BEGIN

PROCESS(sel,a0,a1)

BEGIN

IF sel='0' THEN

q<=a0;

ELSE

q<=a1;

END IF;

END PROCESS;

END ch_arc;

模块 DISP 如下图示。该模块为七段译码器。

LIBRARY ieee;

USE ieee、std_logic_1164、all;

ENTITY disp IS

PORT(a:in std_logic_vector(3 downto 0);

q:out std_logic_vector(6 downto 0));

END disp;

定时器 VHDL 设计

ARCHITECTURE disp_arc OF disp IS

BEGIN

PROCESS(a)

BEGIN

CASE a IS

WHEN "0000"=>q<="0111111";

WHEN "0001"=>q<="0000110";

WHEN "0010"=>q<="1011011";

WHEN "0011"=>q<="1001111";

WHEN "0100"=>q<="1100110";

WHEN "0101"=>q<="1101101";

WHEN "0110"=>q<="1111101";

WHEN "0111"=>q<="0000111";

WHEN "1000"=>q<="1111111";

WHEN "1001"=>q<="1101111";

WHEN others=>q<="0000000";

END CASE;

END PROCESS;

END disp_arc;

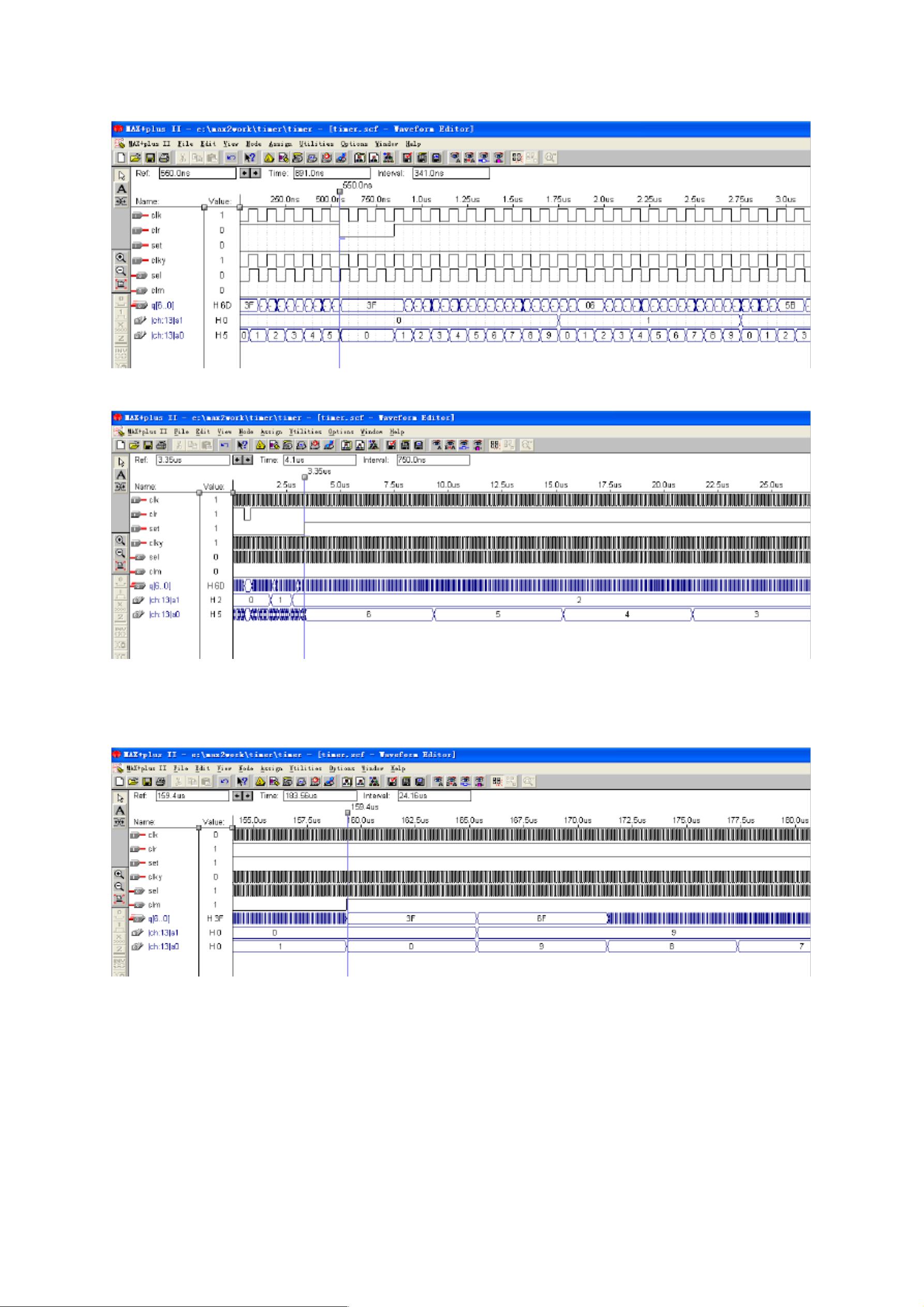

3、仿真结果分析

总体仿真结果如下:

定时器 VHDL 设计

由图可见,clr =’0’可实现整体复位功能。set =’0’,输出以秒的速度从零递增。

本图中当递增到 26 后,set =’1’,输出经 60 分频后以分的速度递减,实现定时,直到零,定时

结束。

定时结束后,clm =’1’,此时可启动各种电路或发出报警,定时结束。

剩余25页未读,继续阅读

资源评论

hhappy0123456789

- 粉丝: 59

- 资源: 5万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功