没有合适的资源?快使用搜索试试~ 我知道了~

数字电路仿真实验使用Multisim软件仿真基础逻辑门电路.docx

需积分: 5 0 下载量 193 浏览量

2024-11-05

19:21:26

上传

评论

收藏 1.36MB DOCX 举报

温馨提示

D触发器能在触发脉冲边沿到来瞬间,将输入端D的信号存入触发器,由Q端输出。触发脉冲消失,输出能保持不变。所以D触发器又名D锁存器 CD4013是常用的D触发器,内含两个上升沿触发的D触发器。图4-17给出了其中一个D触发器的原理图符号。4013的每个D触发器除了具有输入端D,脉冲控制端CP,输出端O、~O以外,还有直接置位端SD,直接复位端CD。直接置位端与直接复位端都是高电平有效。

资源推荐

资源详情

资源评论

数字电路仿真实验【使用 Multisim 软件仿真】

基本逻辑门电路功能测试

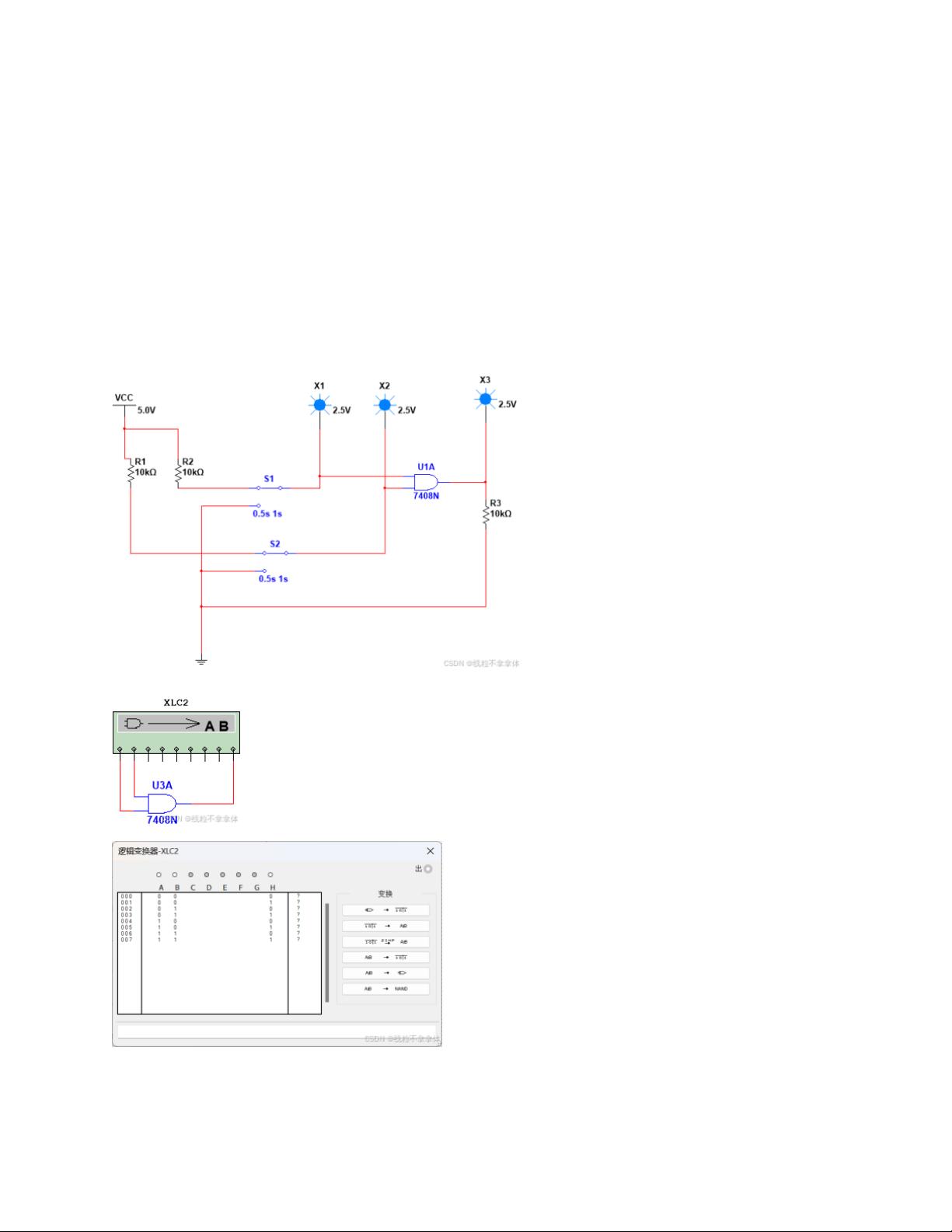

与门仿真

7408 TTL 2 输入端四与门

与门逻辑功能测试仿真电路及逻辑转换仪面板图

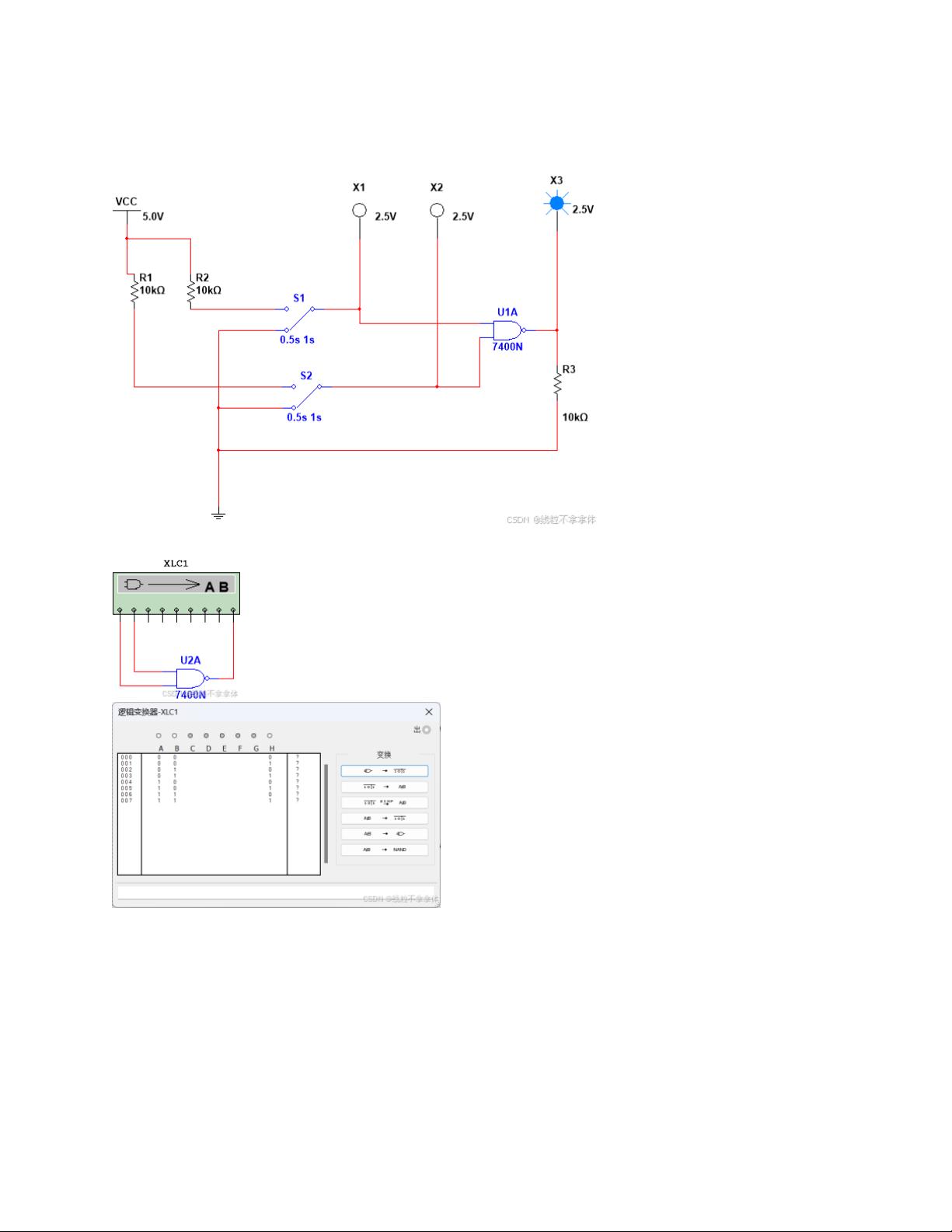

与非门仿真

7400 TTL 2 输入端四与非门

与非门逻辑功能测试仿真电

路及逻辑转换仪面板图

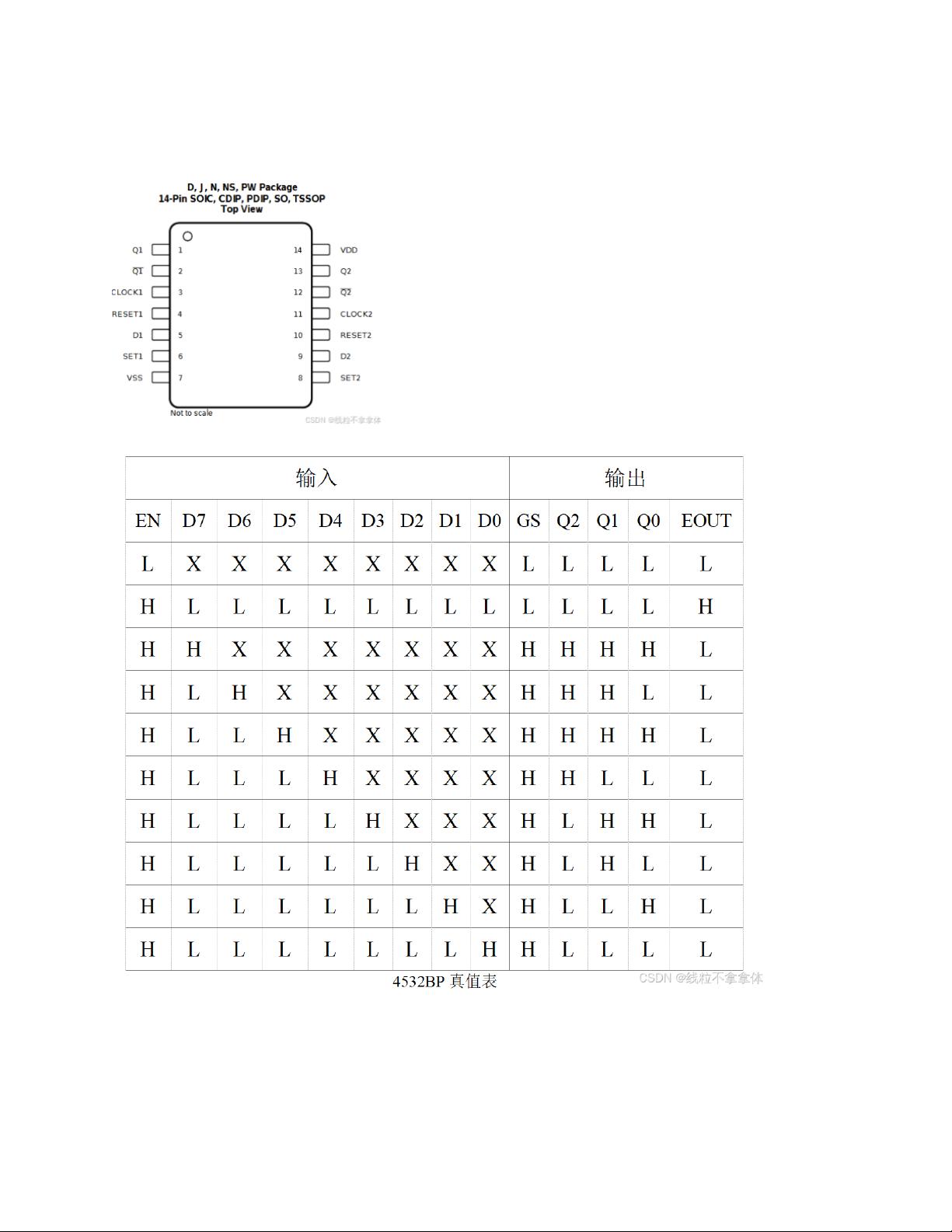

编码器电路功能测试

通过 4532BP 优先编码器(8-3 线编码器)功能表测试其逻辑功能

4532BP 引脚图

仿真图及功能分析

高位具有优先级,当高位导通时低位无法控制,指示灯 “亮”即表示为 1 状态,“灭”表示

为 0 状态。

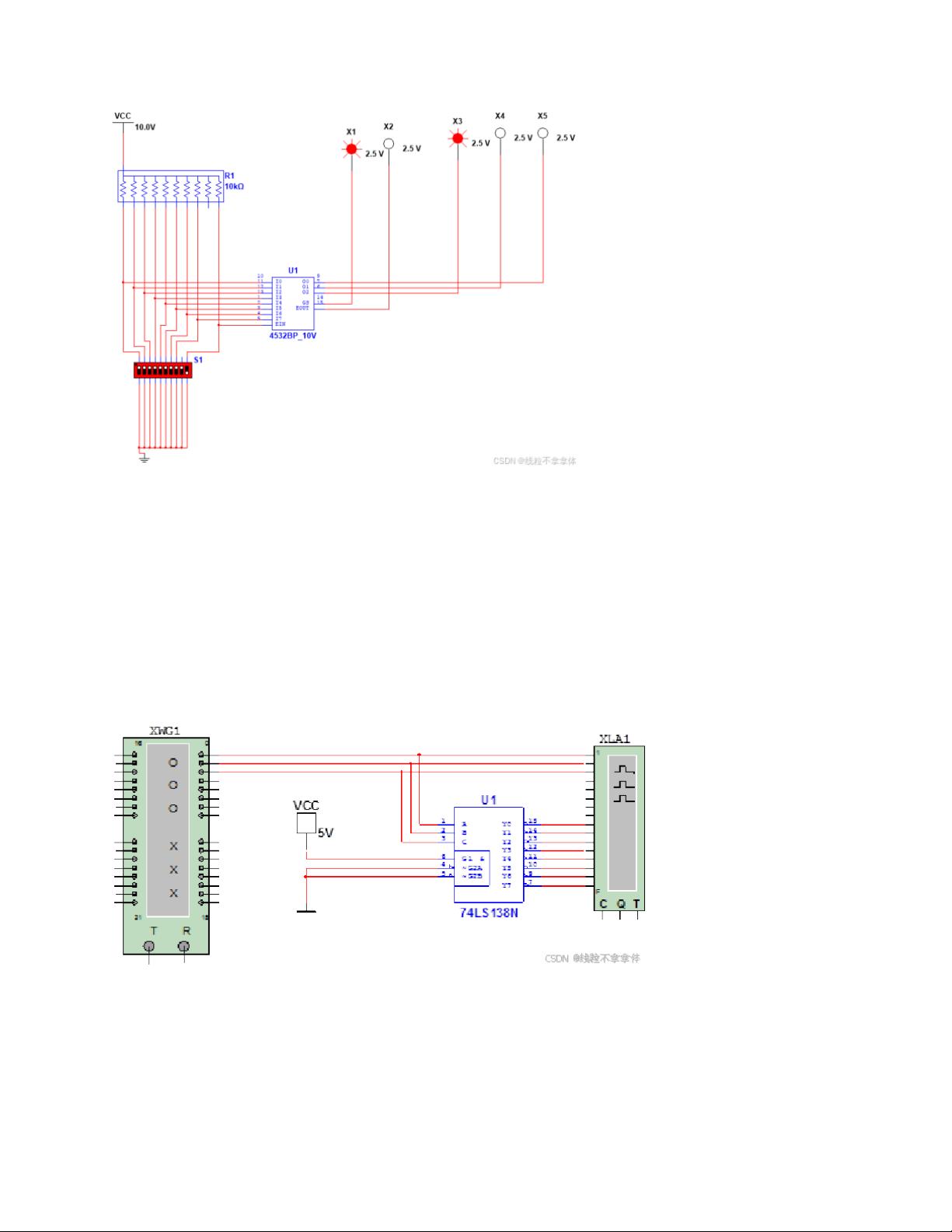

译码器功能测试

译码是编码的那过程,密码器是将输入的二进制代码转换成与代码对应的输出信号。

如果译码器输入的是 n 位二进制代码,则输出的端子数 N≤2n。N=2n 称为完全译码,

N<2n 称为部分译码。

74LS138 译码器电路功能仿真电路图

将逻辑分析仪的时钟设置为时钟 500Hz,每格时钟设置为每格 2 个时钟。观察 138 的 8

个输出引脚状态,并记录于表 4-4 中,若输出高电平即表示为 1 状态,输出低电平表示

为 0 状态。逻辑分析仪显示的仿真结果如图

剩余15页未读,继续阅读

资源评论

生活家小毛.

- 粉丝: 6037

- 资源: 7290

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功