C语言设计前端开发模块开源文档

需积分: 0 37 浏览量

更新于2024-07-13

收藏 8KB DOCX 举报

### C语言设计前端开发模块开源文档

#### 一、引言

本文档旨在详细介绍一个名为“Pkt Issue”模块的设计与实现过程。该模块主要应用于前端开发领域中的数据包管理和调度,通过有效的逻辑设计和算法优化,实现了对数据包的高效处理。本文将围绕模块的功能特性、信号说明以及具体的Verilog代码实现等方面进行详细阐述。

#### 二、Pkt Issue模块功能概述

Pkt Issue模块被设计用于处理和管理前端系统中的数据包,其核心功能包括:

1. **移位寄存器**: 存储延时和位置信息。

2. **依赖关系检查**: 检查当前数据包是否需要依赖其他数据包,若有依赖,则进一步检查依赖的数据包是否已完成转发。

3. **延时关系检查**: 确保数据包之间不存在延时冲突。

4. **数据包传输到前端(FE)**: 当满足特定条件时,将数据包发送到前端,并同时记录其延时和位置信息。

5. **前端输出保持顺序**: 确保从前端输出的数据包能够按照正确的顺序进行存储。

6. **生成issue_rdy信号**: 用于控制Squeeze FIFO的读取信号。

#### 三、信号说明

为了更清晰地理解Pkt Issue模块的工作原理,下面列出了该模块中涉及到的主要信号及其含义:

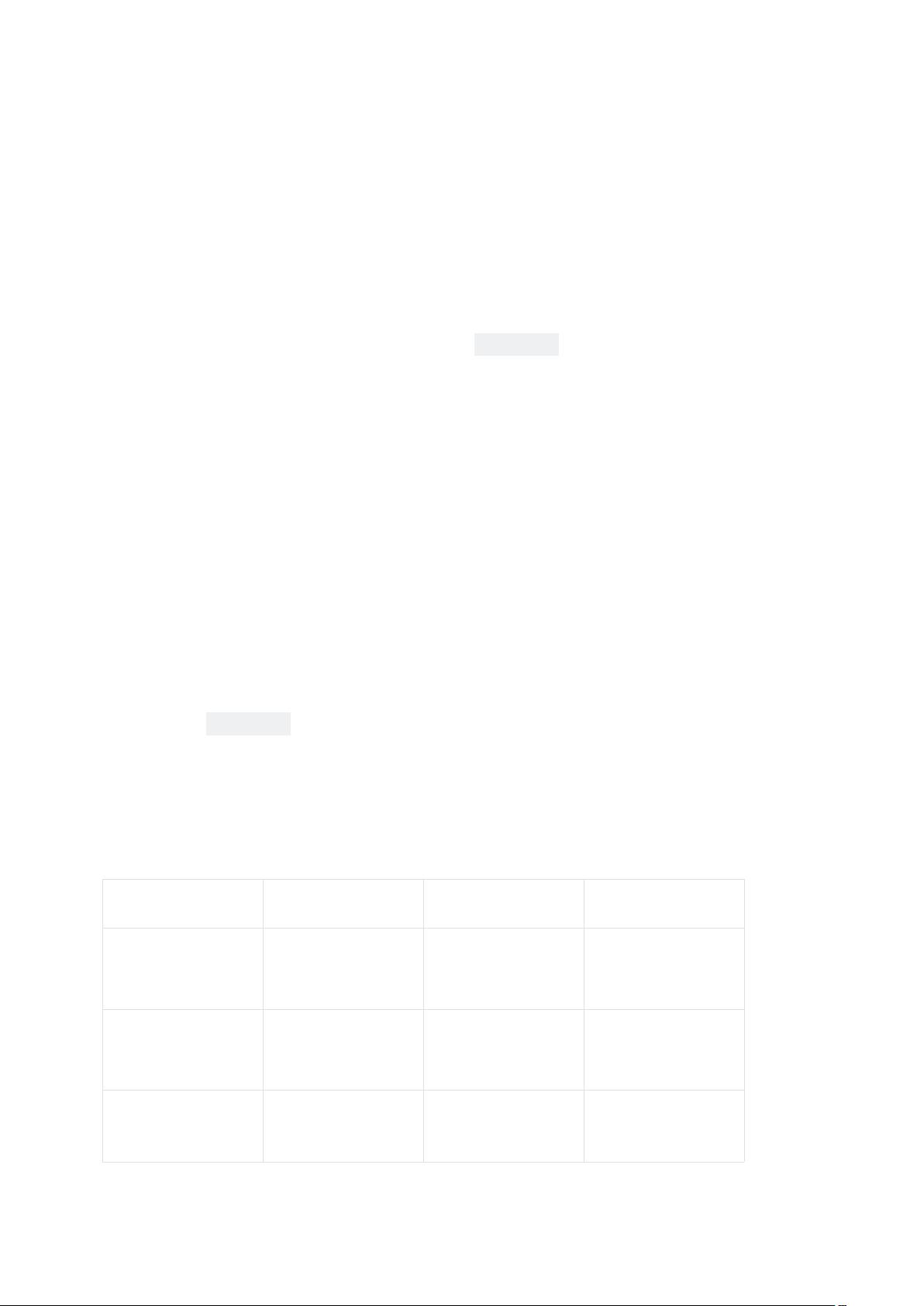

| 信号名称 | I/O | 宽度 | 描述 |

| --- | --- | --- | --- |

| sqz_pkt_vld | 输入 | 1 | FIFO输出数据包的valid信号,高电平有效 |

| sqz_pkt_data | 输入 | 128 | FIFO输出数据包的数据 |

| sqz_pkt_ctrl | 输入 | 5 | FIFO输出数据包的随路信息,包括延时与依赖关系 |

| sqz_pkt_idx | 输入 | 3 | FIFO中数据包的存储位置的最低三位 |

| postfe_pkt_dp_vld | 输入 | 1 | PostFE中存储的依赖数据包的valid信号,高电平有效 |

| issue_pkt_data | 输出 | 128 | 发送到前端中的数据包 |

| pkt_dp_num | 输出 | 3 | 依赖数据包与当前数据包之间的数据包数量 |

| fwd_pkt_data_vld | 输出 | 1 | 发送到前端的数据包valid信号,高电平有效 |

| fwd_pkt_lat | 输出 | 2 | 发送到前端的数据包延时信息 |

| issue_pkt_vld | 输出 | 1 | 数据包可发送到前端的valid信号,高电平有效 |

| issue_rdy | 输出 | 1 | Pkt Issue对下一个数据包的ready信号,高电平有效 |

| fwd_pkt_dp | 输出 | 1 | 当前FIFO输出数据包存在依赖关系,高电平有效 |

| issue_pkt_idx | 输出 | 3 | 从前端中转发完成的数据包的存储位置 |

#### 四、Verilog代码实现

下面是Pkt Issue模块的部分Verilog代码实现细节:

```verilog

module PktIssue (

input wire clk,

input wire reset,

input wire sqz_pkt_vld,

input wire [127:0] sqz_pkt_data,

input wire [4:0] sqz_pkt_ctrl,

input wire [2:0] sqz_pkt_idx,

input wire postfe_pkt_dp_vld,

input wire [2:0] postfe_pkt_dp_num,

output reg [127:0] issue_pkt_data,

output reg [2:0] pkt_dp_num,

output reg fwd_pkt_data_vld,

output reg [1:0] fwd_pkt_lat,

output reg issue_pkt_vld,

output reg issue_rdy,

output reg fwd_pkt_dp,

output reg [2:0] issue_pkt_idx);

reg [2:0] latency_sr [0:3]; // 延时寄存器,3位(最高位为有效信号,低2位为延时信息)

reg [2:0] pos_sr [0:3]; // 位置寄存器,3位位置信息

reg [1:0] write_ptr; // 写指针

reg [1:0] read_ptr; // 读指针

reg fe_busy; // 表示FE是否正在处理数据包

always @(posedge clk or posedge reset) begin

if (reset) begin

issue_pkt_data <= 0;

pkt_dp_num <= 0;

fwd_pkt_data_vld <= 0;

fwd_pkt_lat <= 0;

issue_pkt_vld <= 0;

issue_rdy <= 0;

fwd_pkt_dp <= 0;

issue_pkt_idx <= 0;

write_ptr <= 0;

read_ptr <= 0;

fe_busy <= 0;

latency_sr[0] <= 3'b000;

latency_sr[1] <= 3'b000;

```

以上代码定义了Pkt Issue模块的基本结构和初始化过程。通过这些信号和状态机的配合工作,Pkt Issue模块能够有效地管理前端系统的数据包传输流程,保证数据包在传输过程中的正确性和及时性。

#### 五、总结

Pkt Issue模块是前端开发中一个重要的组成部分,通过对数据包的有效管理和调度,它能够显著提升前端系统的整体性能和稳定性。通过本篇文档的介绍,我们不仅了解了Pkt Issue模块的核心功能,还深入探讨了其实现的具体方法和技术细节,这对于理解和应用该模块具有重要的参考价值。