4

MSP432P401R, MSP432P401M

ZHCSET7H –MARCH 2015–REVISED JUNE 2019

www.ti.com.cn

内容

版权 © 2015–2019, Texas Instruments Incorporated

内内容容

1 器器件件概概述述 .................................................... 1

1.1 特性 ................................................... 1

1.2 应用 ................................................... 2

1.3 说明 ................................................... 2

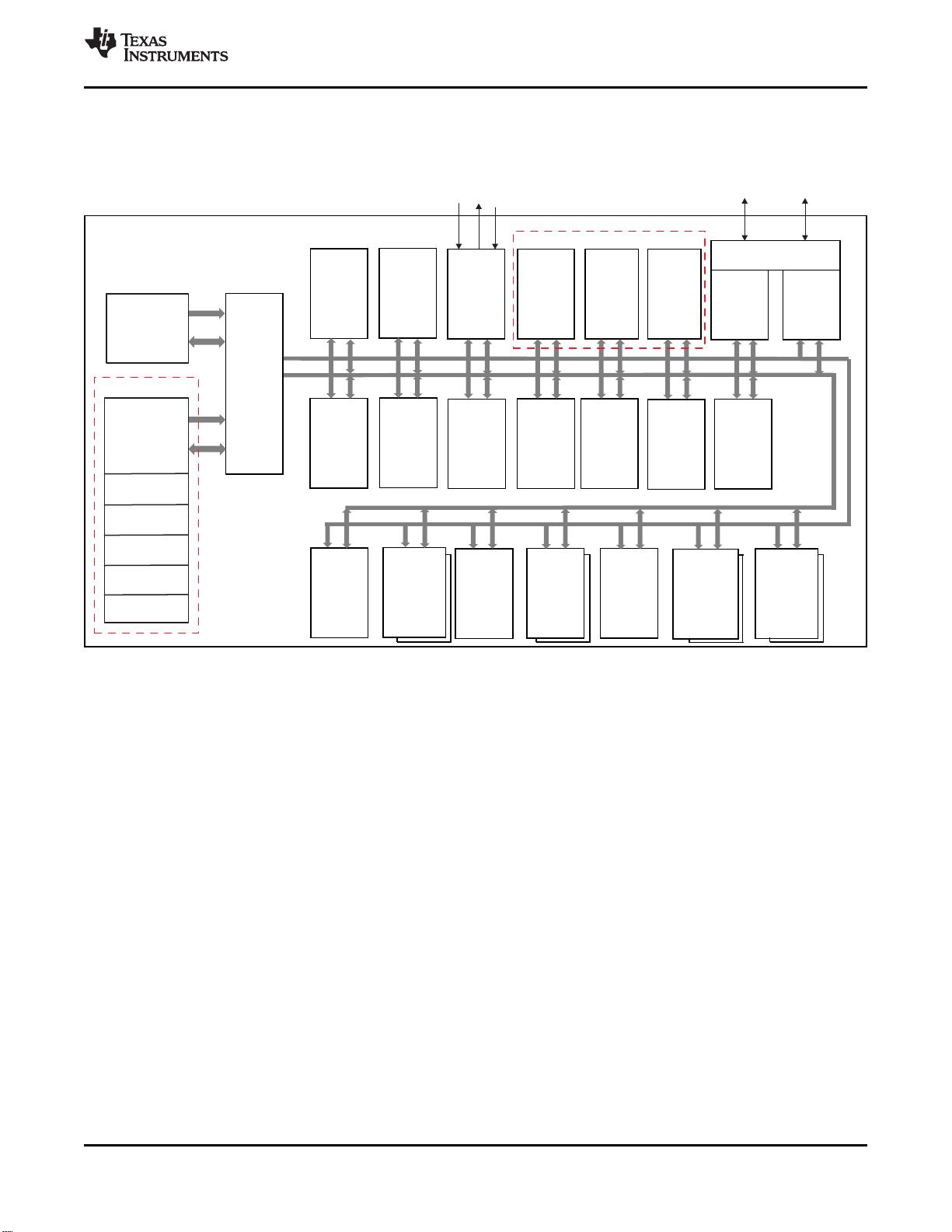

1.4 功能方框图............................................ 3

2 修修订订历历史史记记录录............................................... 5

3 Device Comparison ..................................... 6

3.1 Related Products ..................................... 6

4 Terminal Configuration and Functions.............. 7

4.1 Pin Diagrams ......................................... 7

4.2 Pin Attributes ........................................ 10

4.3 Signal Descriptions.................................. 16

4.4 Pin Multiplexing ..................................... 26

4.5 Buffer Types......................................... 26

4.6 Connection for Unused Pins ........................ 26

5 Specifications........................................... 27

5.1 Absolute Maximum Ratings ........................ 27

5.2 ESD Ratings ........................................ 27

5.3 Recommended Operating Conditions............... 27

5.4 Recommended External Components ............. 28

5.5 Operating Mode V

CC

Ranges ....................... 28

5.6 Operating Mode CPU Frequency Ranges ......... 29

5.7 Operating Mode Peripheral Frequency Ranges .... 29

5.8 Operating Mode Execution Frequency vs Flash

Wait-State Requirements ........................... 30

5.9 Current Consumption During Device Reset of the

100-pin LQFP Package ............................. 30

5.10 Current Consumption in LDO-Based Active

Modes – Dhrystone 2.1 Program ................... 30

5.11 Current Consumption in DC-DC-Based Active

Modes – Dhrystone 2.1 Program ................... 31

5.12 Current Consumption in Low-Frequency Active

Modes – Dhrystone 2.1 Program ................... 31

5.13 Typical Characteristics of Active Mode Currents for

CoreMark Program.................................. 32

5.14 Typical Characteristics of Active Mode Currents for

Prime Number Program............................. 33

5.15 Typical Characteristics of Active Mode Currents for

Fibonacci Program .................................. 34

5.16 Typical Characteristics of Active Mode Currents for

While(1) Program ................................... 35

5.17 Typical Characteristics of Low-Frequency Active

Mode Currents for CoreMark Program.............. 36

5.18 Current Consumption in LDO-Based LPM0 Modes. 37

5.19 Current Consumption in DC-DC-Based LPM0

Modes ............................................... 37

5.20 Current Consumption in Low-Frequency LPM0

Modes ............................................... 37

5.21 Current Consumption in LPM3, LPM4 Modes ...... 38

5.22 Current Consumption in LPM3.5, LPM4.5 Modes .. 38

5.23 Current Consumption of Digital Peripherals ........ 39

5.24 Thermal Resistance Characteristics ................ 39

5.25 Timing and Switching Characteristics ............... 40

6 Detailed Description ................................... 89

6.1 Overview ............................................ 89

6.2 Processor and Execution Features ................. 89

6.3 Memory Map ........................................ 90

6.4 Memories on the MSP432P401x .................. 110

6.5 DMA................................................ 113

6.6 Memory Map Access Details ...................... 114

6.7 Interrupts........................................... 116

6.8 System Control..................................... 118

6.9 Peripherals......................................... 123

6.10 Code Development and Debug .................... 133

6.11 Performance Benchmarks ......................... 135

6.12 Input/Output Diagrams ............................. 137

6.13 Device Descriptors (TLV) .......................... 175

6.14 Identification........................................ 177

7 Applications, Implementation, and Layout ...... 179

7.1 Device Connection and Layout Fundamentals .... 179

7.2 Peripheral and Interface-Specific Design

Information ......................................... 180

8 器器件件和和文文档档支支持持......................................... 182

8.1 入门和下一步....................................... 182

8.2 器件命名规则....................................... 182

8.3 工具和软件 ......................................... 183

8.4 文档支持 ........................................... 185

8.5 相关链接 ........................................... 186

8.6 社区资源 ........................................... 187

8.7 商标 ................................................ 187

8.8 静电放电警告....................................... 187

8.9 Export Control Notice .............................. 187

8.10 Glossary............................................ 187

9 机机械械、、封封装装和和可可订订购购信信息息 .............................. 188

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功