没有合适的资源?快使用搜索试试~ 我知道了~

546835_Purley Platform Design Guide Rev 1.6.pdf

需积分: 9 3 下载量 173 浏览量

2022-01-10

16:23:02

上传

评论 1

收藏 127.37MB PDF 举报

温馨提示

试读

1168页

546835_Purley Platform Design Guide Rev 1.6.pdf

资源详情

资源评论

资源推荐

Purley

Platform Design Guide

Rev. 1.6

October 2016

Intel Confidential

Doc. No.: 546835, Rev.: 1.6

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described

herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed

herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and

roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit http://

www.intel.com/design/literature.htm.

I2C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips

Corporation.

No computer system can provide absolute security under all conditions. Intel

®

Trusted Execution Technology (Intel

®

TXT) requires a computer with

Intel

®

Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured

launched environment (MLE). Intel TXT also requires the system to contain a TPM v1.s. For more information, visit http://www.intel.com/technology/

security.

BlueMoon, BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Cilk, Core Inside, E-GOLD, i960, Intel, the Intel logo, Intel AppUp, Intel

Atom, Intel Atom Inside, Intel Core, Intel Inside, Intel Insider, the Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel

SingleDriver, Intel SpeedStep, Intel Sponsors of Tomorrow., the Intel Sponsors of Tomorrow. logo, Intel StrataFlash, Intel vPro, Intel XScale, InTru,

the InTru logo, the InTru Inside logo, InTru soundmark, Itanium, Itanium Inside, MCS, MMX, Moblin, Pentium, Pentium Inside, Puma, skoool, the

skoool logo, SMARTi, Sound Mark, The Creators Project, The Journey Inside, Thunderbolt, Ultrabook, vPro Inside, VTune, Xeon, Xeon Inside, X-GOLD,

XMM, X-PMU and XPOSYS are trademarks of Intel Corporation in the U.S. and/or other countries.

*Other names and brands may be claimed as the property of others.

Copyright

©

2014–2016, Intel Corporation. All rights reserved.

Purley

Platform Design Guide October 2016

2 Intel Confidential Doc. No.: 546835, Rev.: 1.6

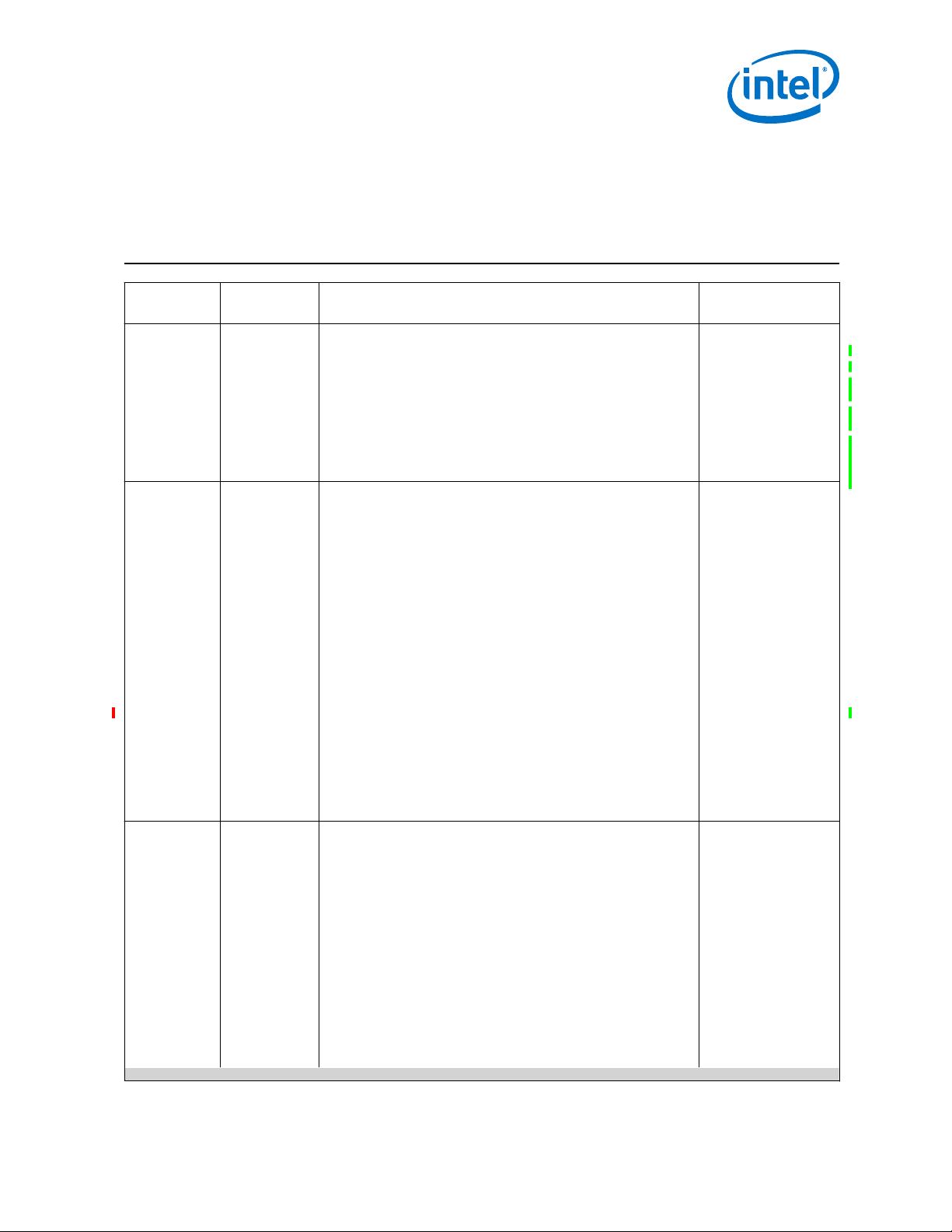

Revision History

Document

Number

Revision

Number

Description Date

546835 1.6 Chapter 1: Added more options in the Mixing Guidelines.

Chapter 8: Removed Length Matching within a bundle for TX.

Chapter 12: Added 2 Topologies for down devices on eSPI section.

Added minimum length changes on SPI section.

Chapter 14: Fixed Typo's. Added single 100 ohm pull up options,

for BMP_N unconnected signals.

Chapter 15: Added the power parameters for new POR SKU 205

Watts. Updated and separated Pmax.app and Iccmax.app

numbers for Skylake and Icelake SKUs.

Chapter 18: Fixed Typos and clarified statements.

September 2016

546835 1.5 • Introduced Icelake name as Purley Refresh Processor.

• Chapter 1: Added Processor Mixing Guidelines.

• Chapter 4: Added Breakout Spacing Exceptions to the 100 MHz

Clock LCT tables,Restructured Crystal Section.

• Chapter 5: Updated tables for corresponding topology 1,3 and

4. Removed topology 7 as it was similar to topology 8.

• Chapter 6: Updated PMSYNC and PMSYNC_CLK length

matching rules and tables.

• Chapter 7: Added Support for 3DS RDIMM, Added Support for

2DPC 2666, Added Barlow Pass DIMM Support for Icelake,

Added Purley Validated RAS Memory Configuration.

• Chapter 12: Footnote included for SPI and eSPI IO and CLK

signals reading overshoots and undershoots. Fixed typos on

figures values.

• Chapter 14: Added need for pull ups to VCCIO for BMP_N

signals when they are not being used, instead of leaving them

floating.

• Chapter 15: Added IccMax.app for 165w and 145w in table

PVCCIN_CPUx VR13.0 (for Skylake Server with Skt P0)

Guidelines. Updated the note for on-Package Pmax Detector in

section: CPU VccIN Dynamic Load Characteristic. Updated

Purely fresh to Icelake Server.

• Chapter 19: Fixed some Typos.

August 2016

546835 1.0 • Chapter 3: changed applicable interfaces for dual stripline

routing from UPI to all HSD; added thieving rule for dual

stripline routing; added note in Bundle Length Matching section

that port length matching is pin-to-pin

• Chapter 4: Clarified the trade-off tables for via count for the

CPU and PCIe clocks; Clarified the Transport Delay table

examples and provided reference to PCI Express* Common

Clock Routing Considerations documentation for risk

assessment; Clarified that SSC must be enabled to 0.4% from

the CK420BQ source clock for USB3 compliance in External

Clocking architecture designs

• Chapter 5: updated Trade-Off tables for UPI topologies 1, 2

and 4;

• Chapter 6: updated terminologies in PROC_ID and PKG_ID

tables

• Chapter 7: Added Supported/Not Supported Configurations to

DDR4 (1LM)

March 2016

continued...

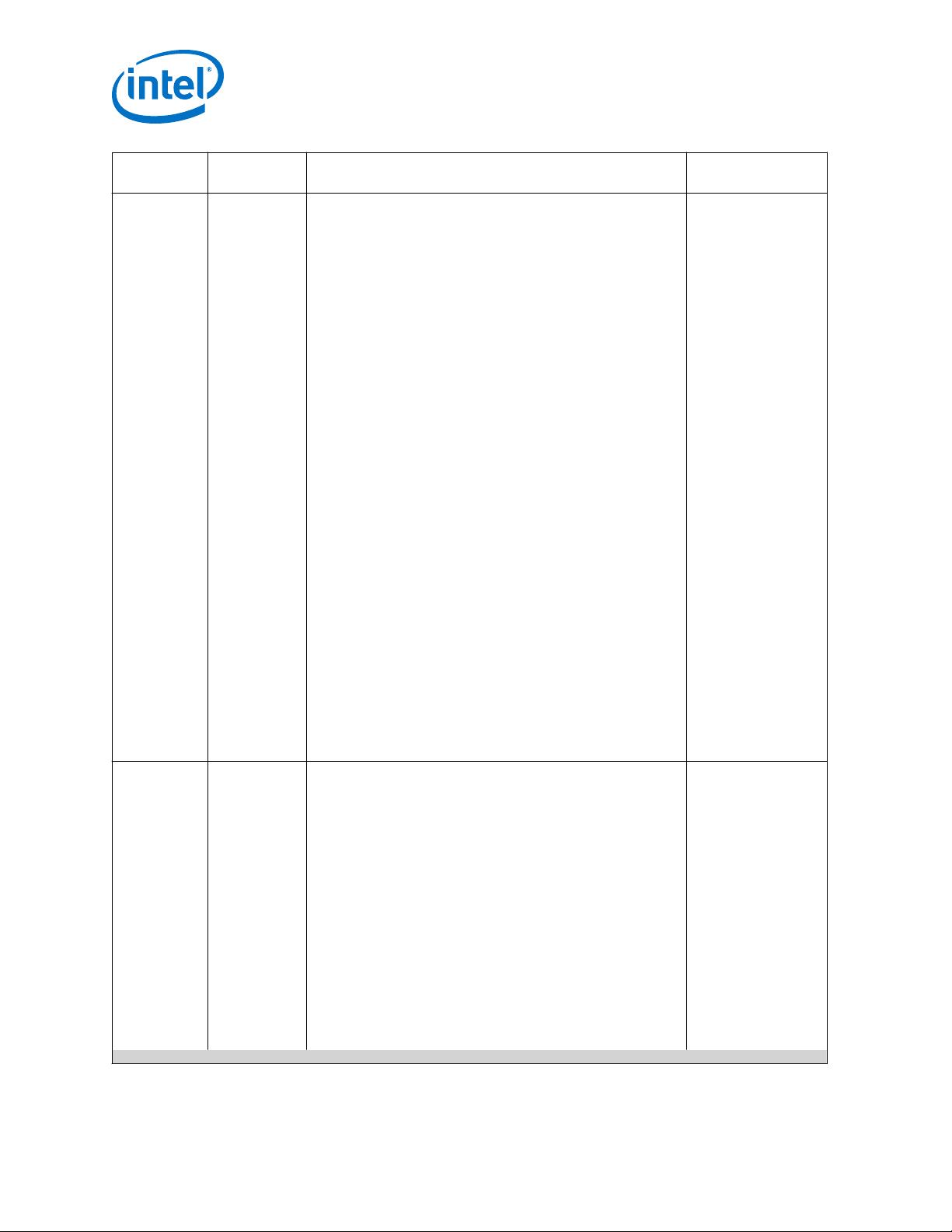

Revision History—Purley

Purley

October 2016 Platform Design Guide

Doc. No.: 546835, Rev.: 1.6 Intel Confidential 3

Document

Number

Revision

Number

Description Date

,AEP

and DDR4

/AEP 2LM

Socket Level Population Requirements;

removed in the General Population Requirements Section the

statement of " Mixing of NVDIMMs and AEP DIMMs within the

same channel or within iMC is not allowed", since NVDIMM is

not Purley POR;

Updated via count for all signal group to consider SMT

connector coverage; included VPP referencing as far

referencing on all DDR tables to clarify options as noted at the

beginning of the chapter; updated bottom layer DQ length to

2700 mils.

• Chapter 8: added note for SSD topologies loss requirement;

removed SSD CEM note in section 8.5.8; added cable

requirement section; updated PCIe SSD and standard topology

lengths and via stub requirements

• Chapter 10: Updated EndPoint Only (EPO) PCH Signal

Connectivity Requirements

• Chapter 11: added note for SSD topologies loss requirement;

removed SSD CEM note in section 8.5.8; added cable

requirement section

• Chapter 13: corrected SPI flash size requirements for ME

support

• Chapter 14: minor updates to JTAG and MBP guidelines for 8-

socket configuration

• Chapter 15: Updated Pmax.app numbers for both 165w and

145w in Table 209; Updated VDDQ total allowable tolerance at

CPU VCCD cavity caps and Max load step @ CPU side for select

SKUs on Purley refresh in Table 228; Updated VPP Max step

load and slew rate @ CPU side for select SKUs on Purley

refresh in Table 233; Updated max load TDC/Iccmax current,

max step load size for some Lewisburg SKUs in Table 244;

Conductivity Equation added to General Motherboard

guidelines section 15.3.1.8; Updated the Auto Detect PMax

correction Factor section 15.3.16

• Chapter 16: updated NCSI routing guidelines

• Chapter 17: Updated reset timing diagrams for power up and

power down reset sequences.

•

546835

0.97 • Chapter 3: clarified intra-pair length matching guideline;

adjusted several rules for 10GbE including Serpentine routing

rule, Routing over split power plane, Trace corner guideline,

via placement, Microstrip via routing, DC blocking cap pad

ground voiding and broadside coupled stripline guideline;

clarified PCIe lane reversal guideline

• Chapter 4: clarification on how SRC, PLAT and ITPXDP clocks

can be used; minor updates to the Integrated Ethernet

Controller 25MHz Crystal Layout guidelines

• Chapter 5: updated routing guideline tables for each topology;

added Trade Off table for topology 6

• Chapter 7: Made correction to the LFend and LFinner values for

break-out and open field region for Figure 188 (DDR4/DDR-T

Source-Synchronous Signal Group Routing Guidelines,

DQ[63:00], DQS_{DP/DN}[17:00], ECC[7:0], 2SPC;Up to 93

mils Stackup, Part4 - Optional Interdigital Tab)

• Chapter 8: added note about lane reversal implementation;

added AC cap values for DMI3

• Chapter 10: clarification on EPO PCH WoL (Wake-On-Line)

power sequencing considerations

December 2015

continued...

Purley—Revision History

Purley

Platform Design Guide October 2016

4 Intel Confidential Doc. No.: 546835, Rev.: 1.6

Document

Number

Revision

Number

Description Date

• Chapter 12: added timing requirements for SPI slave devices;

clarified SPI operational frequency

• Chapter 15: updated voltage regulator related values including

I

max

, I

TDC

, I

step

, Slew rate, etc. for processor voltage rails;

added clarification that Pmax and Pmax.app values include

multi-chip package SKUs; removed typos for P1v0 VR

indicating that this rail needs to be on SVID bus; added

voltage tolerance spec for Select SKUs on Purley Refresh for

Vccd interface

• Chapter 16: corrected 10GbE NCSI Tx and Rx mismatch

guideline

• Chapter 17: updated timing diagrams to separate out extCLK

and Fabric Clock which require clock gating; updated G3 to S0

block diagram Wake-On-Lane to reflect SLP_LAN_N de-

assertion

• Chapter 20: updated 8SG pinwheel topology 1; updated larger

system clocking considerations; updated 88R Product Concept

high level architecture and MISC architecture

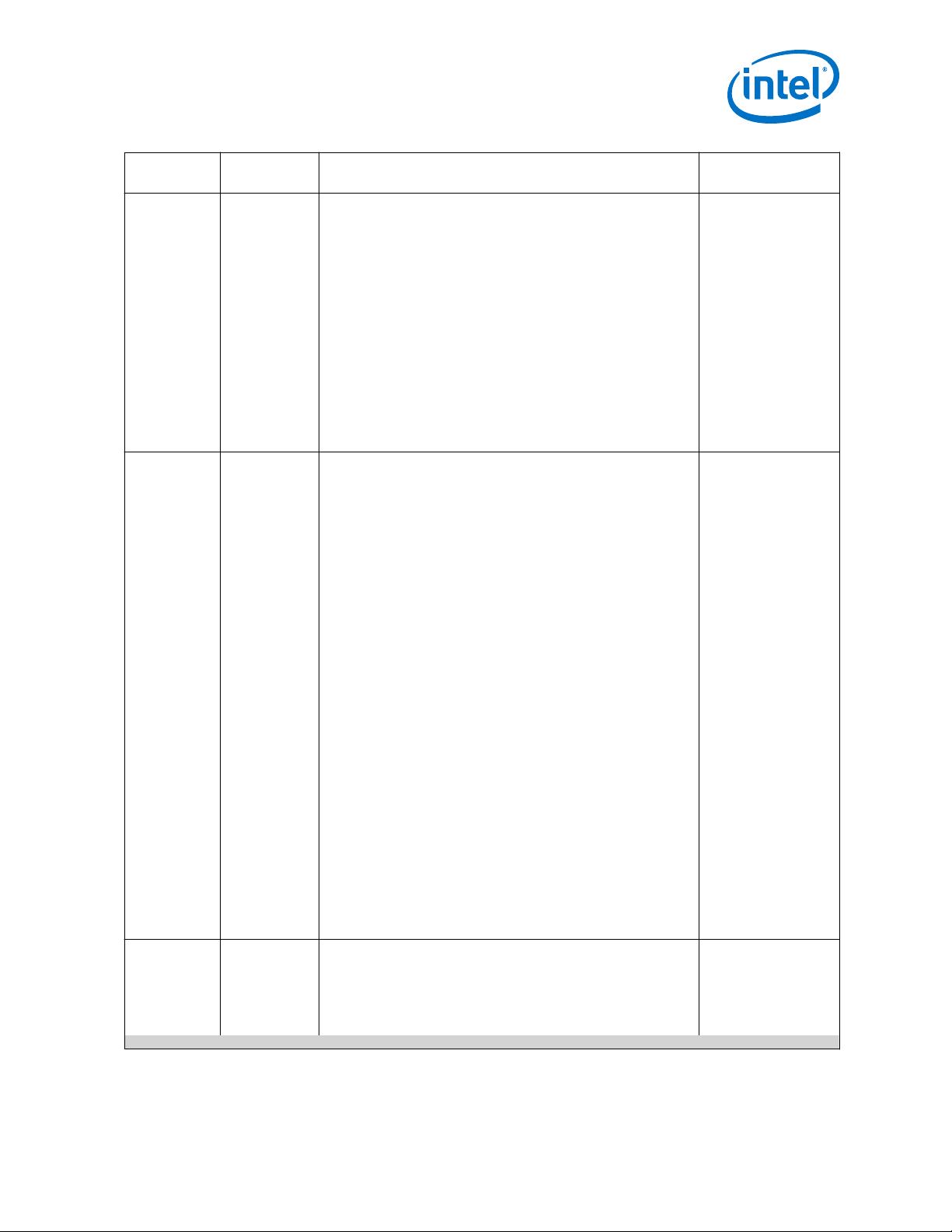

546835 0.96 • Chapter 3: added a rule about power supply noise coupling to

signal; added clarification to the edge rate recommendations

for routing clearance from vertical features; added clarification

on routing angle in length matching requirements; updated via

pitch requirements; added clarification on connector antipad

size; added back port length matching rule.

• Chapter 4: added a standing wave effect note to CPU clock

topologies for Native isCLK and Platform Hybrid Mode;

clarification on EXTCLK routing rule: can be left as NC when

used; recommendations on which DB device to source

EXTCLK .

• Chapter 6: added clarification on "intra trace spacing" rule for

single-ended MISC IO signals

• Chapter 7: Rcomp2 and Rcomp0 value change; relax Ptab in

pinfield routing region to cover 21mils min, 65mils max and

one time 100mils max in pinfield/breakout area; relaxed TS

and S_track as minimum requirement, and allow S_track

reduced down to 4mils in 100mils; added option 2 interdigital

tabbed routing picture and removed Ltab_end definition in PDG

(Ltab=Ltab_end), and indicated option 2 interdigital tabbed

routing is preferred; updated CAC interdigital tabbed routing

picture (change Ltab_end to be Ltab); added all 2SPC CAC

exceptional rules into 1SPC CAC section.

• Chapter 11: added PCH PCIe SSD routing topologies; removed

SATA Express topologies

• Chapter 12: updated eSPI routing length requirements

• Chapter 13: clarified PE_RST# connectivity guidance

• Chapter 14: added USB3 port implementation requirements for

DCI

• Chapter 15: added processor and memory RAPL guidelines

• Chapter 16: added guidance on the optional LAN JTAG

firmware debug header

• Chapter 17: added Wolf River timing diagram; added note on

USB Vbus S0 to S5 power down sequence.

September 2015

546835 0.95 • Chapter 1: added a new section of Routing Topology Table

terminology definition.

• Chapter 2: added routing scaling guidance for higher-loss

materials than previous spec.

• Chapter 3: added via drill diameter guidance; clarified layer

transition and via stub guidance.

June 2015

continued...

Revision History—Purley

Purley

October 2016 Platform Design Guide

Doc. No.: 546835, Rev.: 1.6 Intel Confidential 5

剩余1167页未读,继续阅读

Ari0409es

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Screenshot_20240427_031602.jpg

- 网页PDF_2024年04月26日 23-46-14_QQ浏览器网页保存_QQ浏览器转格式(6).docx

- 直接插入排序,冒泡排序,直接选择排序.zip

- 在排序2的基础上,再次对快排进行优化,其次增加快排非递归,归并排序,归并排序非递归版.zip

- 实现了7种排序算法.三种复杂度排序.三种nlogn复杂度排序(堆排序,归并排序,快速排序)一种线性复杂度的排序.zip

- 冒泡排序 直接选择排序 直接插入排序 随机快速排序 归并排序 堆排序.zip

- 课设-内部排序算法比较 包括冒泡排序、直接插入排序、简单选择排序、快速排序、希尔排序、归并排序和堆排序.zip

- Python排序算法.zip

- C语言实现直接插入排序、希尔排序、选择排序、冒泡排序、堆排序、快速排序、归并排序、计数排序,并带图详解.zip

- 常用工具集参考用于图像等数据处理

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0