实验目的

应用 Verilog 进行编写四种波形发生的程序,并用 modelsim 进行

仿真。加深了解 Verilog 的编程以及掌握使用 modelsim,加强对

其的实际应用操作能力。

实验内容

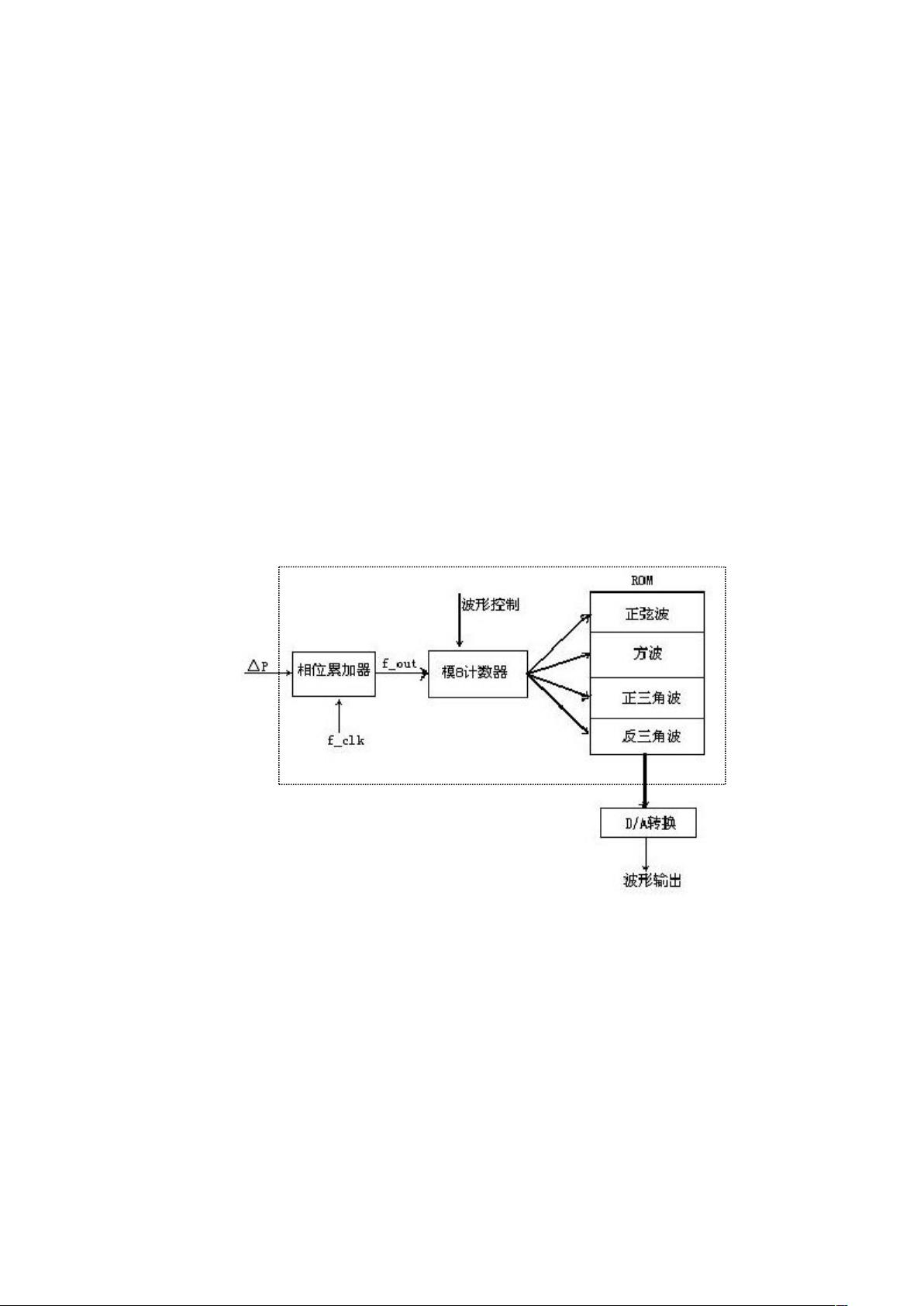

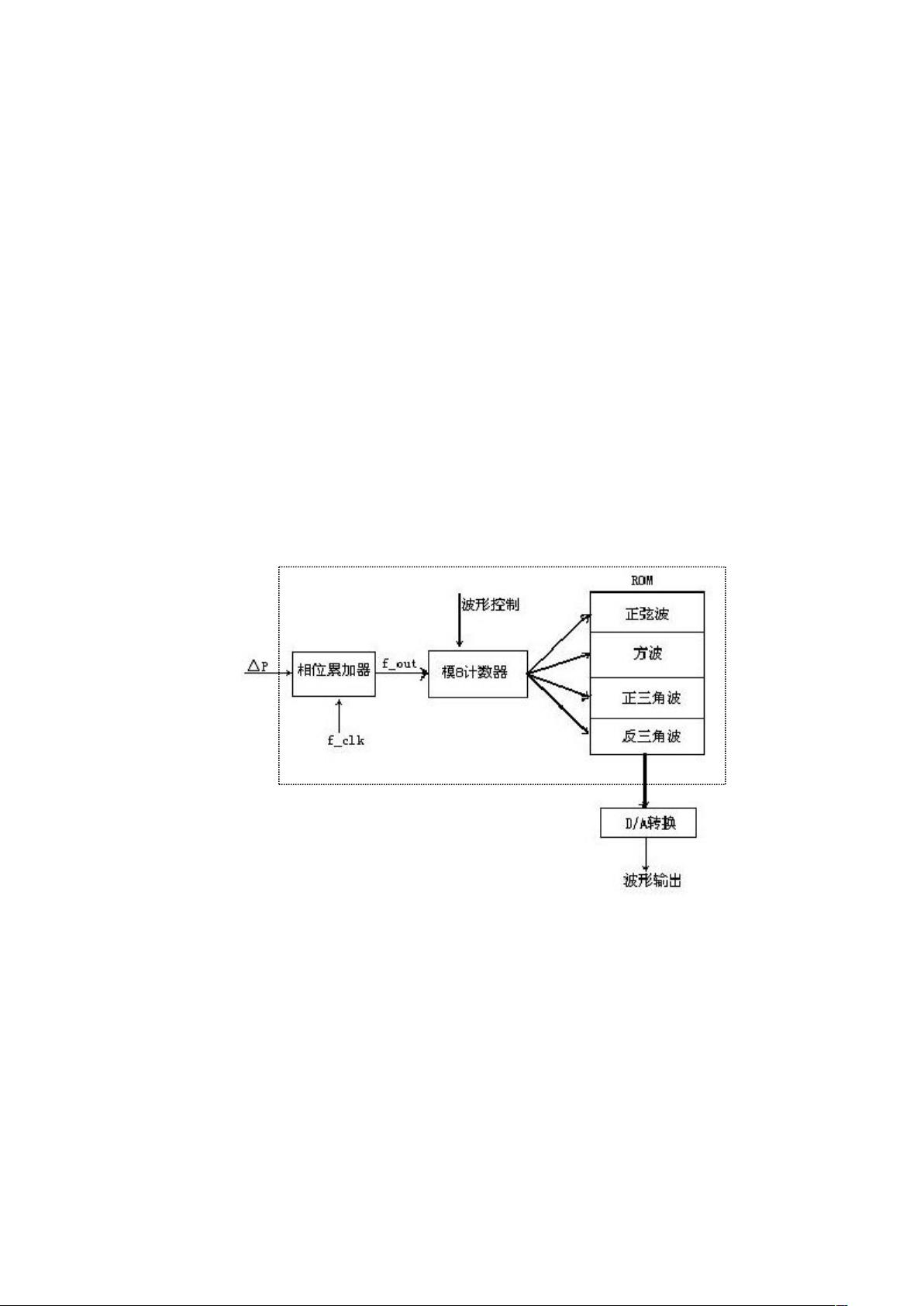

总体设计方案及其原理说明:

图 1-1 系统总体设计方案

DDS 是一种把数字信号通过数/模转换器转换成模拟信号的合成

技术。它由相位累加器、相幅转换函数表、D/A 转换器以及内部时

FPGA

波形发生器.zip (27个子文件)

波形发生器.zip (27个子文件)  波形发生器

波形发生器  verilog期末 - 副本.docx 279KB

verilog期末 - 副本.docx 279KB wave

wave  wave.cr.mti 493B

wave.cr.mti 493B wave_tp.v.bak 360B

wave_tp.v.bak 360B wave.v 1KB

wave.v 1KB wave.mpf 20KB

wave.mpf 20KB wave_tp.v 320B

wave_tp.v 320B vsim.wlf 72KB

vsim.wlf 72KB work

work  wave

wave  _primary.dbs 979B

_primary.dbs 979B verilog.psm 8KB

verilog.psm 8KB verilog.prw 331B

verilog.prw 331B _primary.vhd 314B

_primary.vhd 314B _primary.dat 2KB

_primary.dat 2KB _info 677B

_info 677B wave_tp

wave_tp  _primary.dbs 641B

_primary.dbs 641B verilog.psm 8KB

verilog.psm 8KB verilog.prw 546B

verilog.prw 546B _primary.vhd 238B

_primary.vhd 238B _primary.dat 576B

_primary.dat 576B _temp

_temp  vlog6m7mat 448B

vlog6m7mat 448B vlogmv0jvf 373B

vlogmv0jvf 373B vlogmj01gk 2KB

vlogmj01gk 2KB vlog3zd5i0 510B

vlog3zd5i0 510B vlogrgf00e 2KB

vlogrgf00e 2KB vlognfcwzv 2KB

vlognfcwzv 2KB vlogkd3h1t 2KB

vlogkd3h1t 2KB _vmake 26B

_vmake 26B wave.v.bak 1KB

wave.v.bak 1KB

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益

我的收益  我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功