没有合适的资源?快使用搜索试试~ 我知道了~

SOPC_EDA实验讲义_GW48-PK2.pdf

温馨提示

试读

82页

SOPC_EDA实验讲义_GW48-PK2.pdf EDA使用手册 潘松第二版

资源推荐

资源详情

资源评论

SOPC_EDA 实验讲义_GW48-PK212/6/2006

目 录

第一章 VHDL 文本输入设计方法

1.1 编辑输入并存盘 VHDL 原文件 1.2 将当前设计设定为工程

1.3 选择 VHDL 文本编译版本号和排错 1.4 时序仿真

1.5 硬件测试 1.6 部分实验

第二章 全国大学生电子设计竞赛赛题练习

2.1 等精度频率计设计 2.2 数字移相正弦信号发生器设计

2.3 测相仪设计 2.4 逻辑分析相仪设计

2.5 存储示波器设计

第三章 Quartus II 设计正弦信号发生器

3.1 顶层 VHDL 文件设计

3.1.1 创建工程和编辑设计文件 3.1.2 创建工程

3.1.3 编译前设置 3.1.4 编译及了解编译结果

3.2 正弦信号数据 ROM 定制

3.2.1 设计 ROM 初始化数据文件 3.2.2 定制 ROM 元件(DATAROM.VHD)

3.2.3 仿真 3.2.4 引脚锁定、下载和硬件测试 3.2.5 使用嵌入式逻辑分析仪进行实时测试

3.2.6 对配置器件 EPCS4/EPCS1 编程 3.2.7 了解此工程的 RTL 电路图

第四章 MATLAB/DSP Builder DSP 硬件模块设计

4.1 可控正弦信号发生器设计

4.1.1 建立设计模型 4.1.2 Simulink模型仿真

4.1.3 SignalCompiler 使用方法 4.1.4 使用 QuartusII 实现时序仿真

4.1.5 使用 QuartusII 硬件测试与硬件实现

4.2 MATLAB 窗口使用嵌入式逻辑分析仪 SignalTapII(自动设计流程)

4.2.1 安装 SignalTapII Node 模块 4.2.2系统仿真和硬件测试 首先进行系统仿真

4.4 DDS 与数字相移信号发生器设计

第五章 Nios 嵌入式系统开发向导

5.1 Nios 软硬件开发流程; 5.2 Nios 软硬件开发流程

5.3 SOPC 整体系统生成 5.4 Nios硬件系统生成

第六章 模拟 EDA 实验及其设计软件使用向导

第1 节 PAC _Designer 使用向导 第 2 节 设计直流增益为 9 的放大器 第3 节ispPAC10/20/80 简介

第七章 GW48-SOPC/DSP(Cyclone 器件)适配板使用说明

第八章 单片机与 GW48-PK2 实验系统接口说明

第九章 GWDVP-B 电子设计竞赛应用板使用说明

第十章 现代计算机组成原理实验适配板、GWAK100A 适配板使用说明

第十一章 Nios 软件开发

第1 节 调试软件 第 2 节 烧写 Flash 第 3 节 从新定位复位执行程序

第十二章 基于直接 VHDL 模块的 Nios 自定义指令设计

第十三章 基于 DSP Builder 生成模块的 Nios 自定义指令设计

附录 GW48 系列 EDA/SOPC 主系统使用说明

1

SOPC_EDA 实验讲义_GW48-PK212/6/2006

第一章 VHDL 文本输入设计方法

1.1 编辑输入并存盘 VHDL 原文件

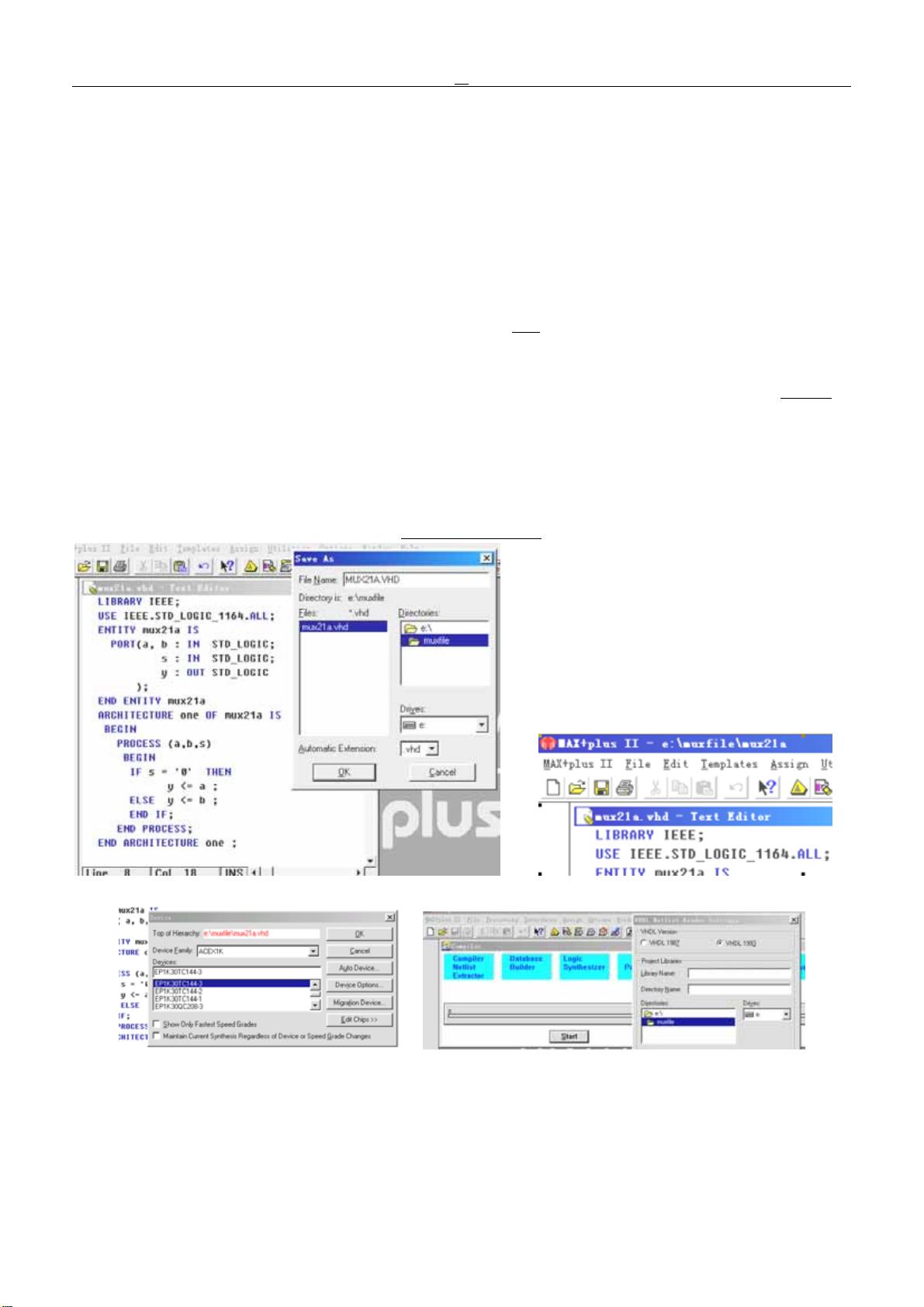

首先应该建立好工作库目录,以作设计工程项目的工作库。例如设文件夹为:E:\muxfile ,以便将设计过程中的相关文

件存储在此。任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关文件的文件夹,此文件

夹将被 EDA 软件默认为工作库(Work Library)。注意,文件夹不能用中文。

然后打开MAX+plusII,选择菜单“File”Æ“New…”,出现对话框,在框中选中“Text Editor file”,按“OK”

按钮,即选中了文本编辑方式。在出现的“Untitled-Text Editor” 文本编辑窗(图1-1)中键入图 1-1 所示的VHDL

程序

(2 选1 多路选择器),毕后,选择菜单“FileÆSave”,即出现如图 1-1 所示的“Save As”对话框。首先在“Directories”

目录框中选择自己已建立好的存放本文件的目录E:\MUXFILE(用鼠标

双击此目录,使其打开),然后在“File Name”框中

键入文件名“MUX21A.VHD”,按“OK”按钮,即把输入的文件放在目录E:\MUXFILE中了。

注意, 1 、VHDL程序文本存盘的文件名必须与文件的实体名一致,如MUX21A.VHD;2、文件的后缀将决定使用的语言形式,在MAX+plusII

中,后缀为.VHD表示VHDL文件;后缀为.TDF表示AHDL文件等。如果后缀正确,存盘后对应该语言的文件中的主要关键词都会

改变颜色。

1.2 将当前设计设定为工程

为了使Max+plusII能对输入的设计项目进行处理,在编译/综合MUX21A.VHD之前,需要设置此文件为顶层文件,或

称工程文件:Project,或者说将此项设计设置成工程:选择菜单“File”ÆProjectÆ“Set Project to Current

File”,当前的设计工程即被指定为MUX21A 。也可以通过选“File”Æ“Project”Æ“Name”,在跳出的“Project

Name”窗中指定E:\MUXFILE下的MUX21A.VHD为当前的工程。设定后可以看见MAX+plusII主窗左上方(图 1-2)的

工程项目路径指向为:“e:\muxfile\mux21a”。

这个路径指向很重要!

图1-1 在文本编辑窗中输入 VHDL 文件并存盘 图1-2 设定当前文件为工程

图1-3 选择目标器件 图1-4 设定 VHDL 编译版本号

如果设计项目由多个设计文件组成,则应该将它们的主文件,即顶层文件设置成 Project。如果要对其中某一底层文

件进行单独编译、仿真和测试,也必须首先将其设置成 Projcet。为了获得与目标器件对应的,精确的时序仿真文件,在

对文件编译前必须选定最后实现本设计项目的目标器件,在Max+plusII 环境中主要选 Altera 公司的 FPGA 或CPLD。

在设定工程文件后,应该选择用于编程的目标芯片:选择菜单“Assign”Æ“Device…”,在弹出的对话框中的“Device

Family”下拉栏中,例如选择 ACEX1K,此窗口(

图4-3)的Device Family 是器件序列栏,应该首先在此拦中选定

目标器件对应的序列名。为了选择 EP1K30TC144-3 器件,应将此栏下方标有 Show only Fastest Speed Grades

2

SOPC_EDA 实验讲义_GW48-PK212/6/2006

的勾消去,以便显示出所有速度级别的器件。完成器件选择后,按 OK 键。

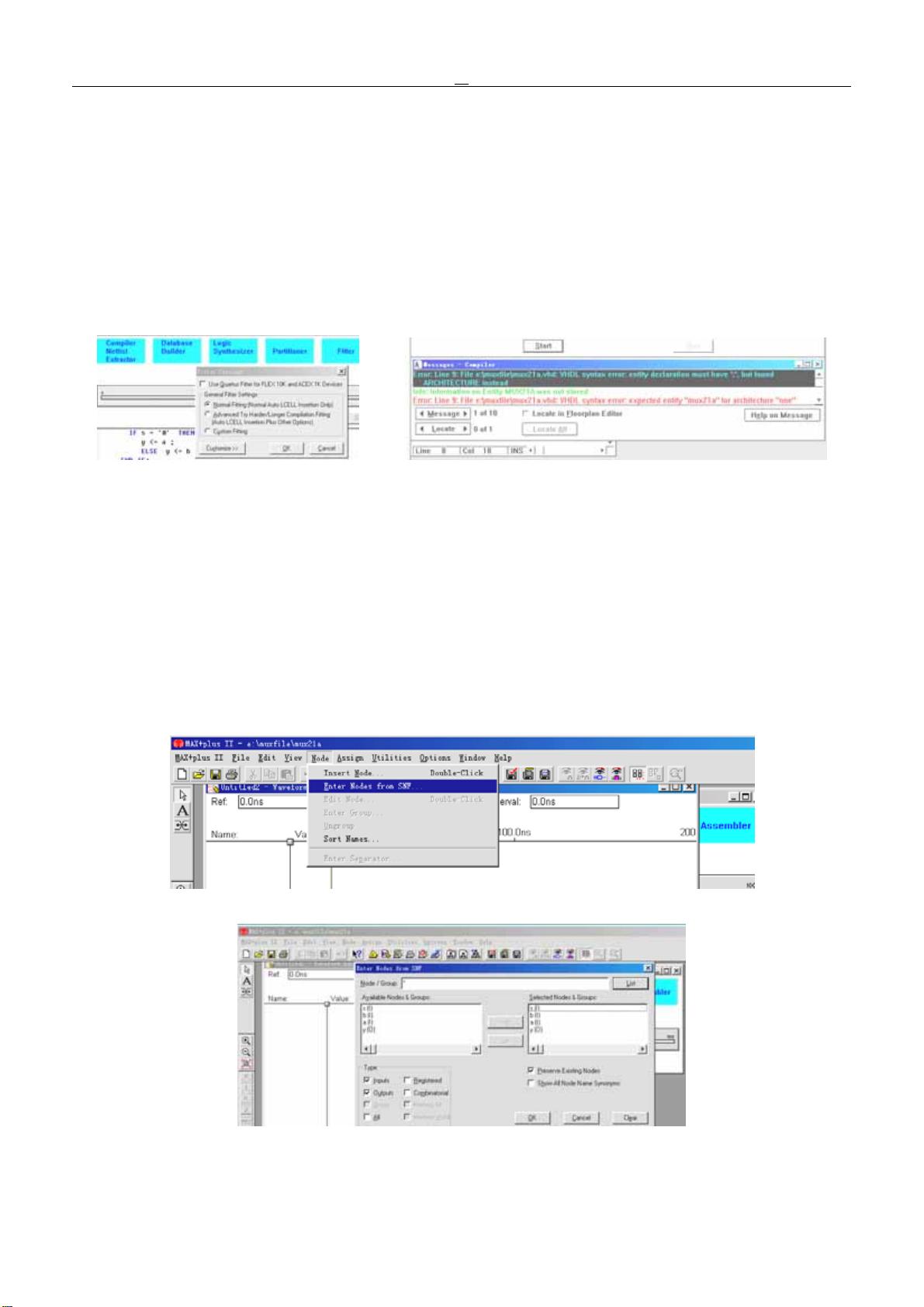

1.3 选择 VHDL 文本编译版本号和排错

选菜单“MAX+plus II”Æ“Compiler”菜单,选择如图 1-4 所示界面上方的“Interfaces”Æ“VHDL Netlist

Reader Settings”,在弹出的窗口中选“VHDL’1993”。

在按“START”键运行编译前,还需要作一件事,即在进入编辑窗(图 1-4),选择 Processing 项,选“Fitter

Setting”,进入如图 1-5 的窗口,消去最上的“

Use Quartus Fitter…”的勾。最后按“START”键,运行编译器。

注意,如图 1-1 所示,MUX21A.VHD 文件中的实体结束语句没有加分号“;”,在编译时出现了如图 1-6 所示的出错信息指示。有时尽管

只有 1、2 个小错,但却会出现大量的出错信息,确定错误所在的最好办法是找到最上一排错误信息指示,用鼠标点成黑色,然后点击如图 1-6

所示窗口左下方的“Locate”错误定位钮,就能发现在出现文本编译窗中闪动的光标附近找到错误所在。纠正后再次编译,直至排除所有错误。

注意闪动的光标指示错误所在只是相对的,错误一般在上方。

VHDL 文本编辑中还可能出现许多其它错误,如:

图1-5 消去“Use Quartus Fitter…”项 图1-6 确定设计文件中的错误

1、错将设计文件存入了根目录,并将其设定成工程,由于没有了工作库,报错信息如下: Error :Can't open VHDL "WORK"

2、错将设计文件的后缀写成.tdf 而非.vhd,报错信息如下:Error :Line1,File e:\muxfile\mux21a.tdf: TDF syntax error: ...

3、未将设计文件名存为其实体名,如错写为 muxa.vhd,报错信息如下:Error :Line1,...VHDL Design File "muxa.vhd" must contain ...

1.4 时序仿真

接下来应该测试设计项目的正确性,即逻辑仿真,具体步骤如下:

1、建立波形文件。为此设计建立一个波形测试文件。选择菜单“File”项及其“New”,再选择 New 窗中的 Waveform

Editer..项,打开波形编辑窗。

2、输入信号节点。在图 1-7 所示的波形编辑窗的上方选择 Node 项,在下拉菜单中选择输入信号节点项 Enter

Nodes from SNF。在弹出的窗口(图 1-8)中首先点击 List 键,这时左窗口将列出该项设计所以信号节点。由于

有时只需要观察其中部分信号的波形,因此要利用中间的“=>”键将需要观察的信号选到右栏中,然后点击 OK 键即可

将测试信号 s(I)、b(I)、a(I)和 y(O)输入仿真波形编辑窗。

图1-7 从SNF 文件中输入设计文件的信号节点

图1-8 列出并选择需要观察的信号节点

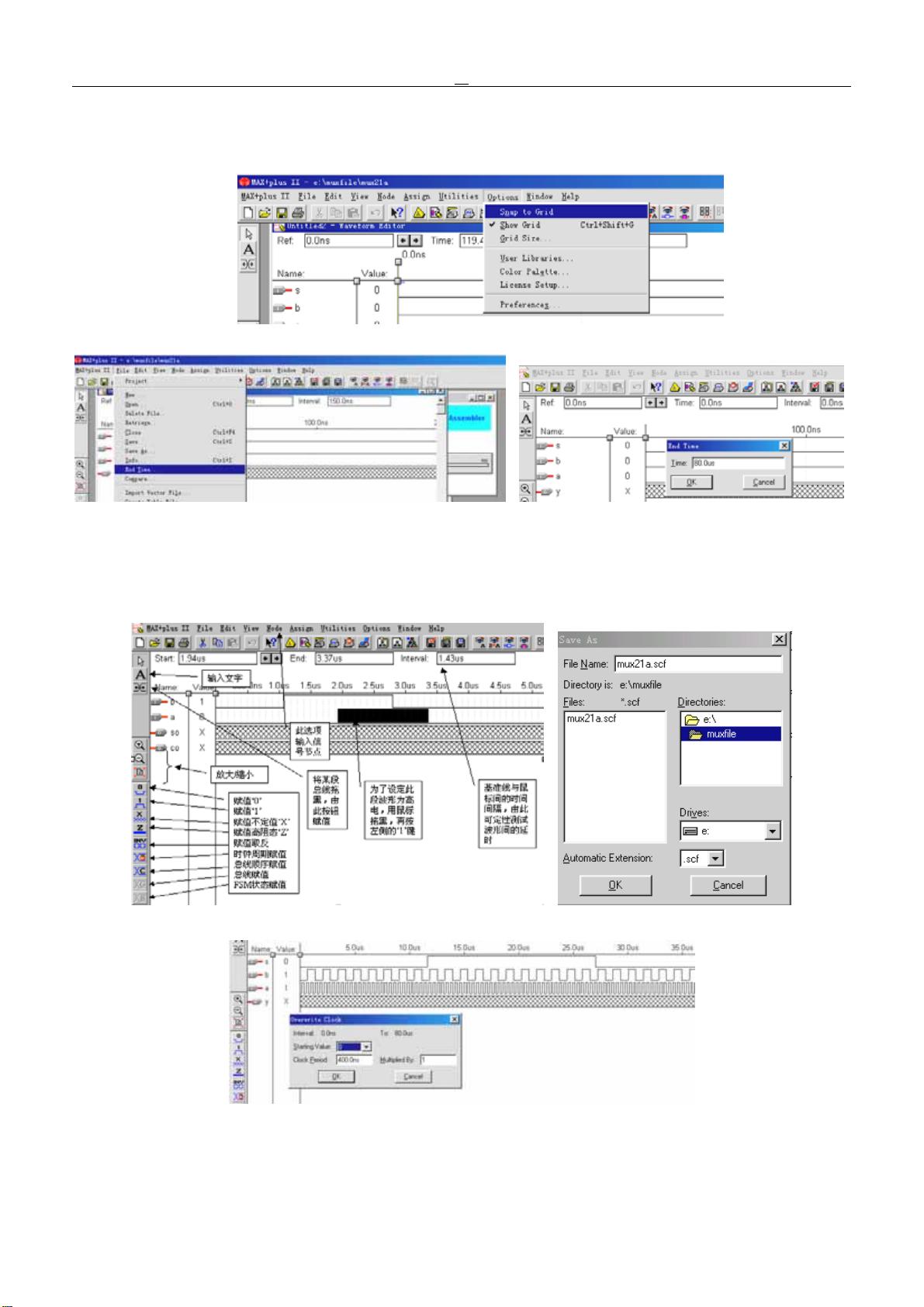

3、设置波形参量。首先设定相关的仿真参数。如图 1-9 所示, 在Options 选项中消去网格对齐 Snap to Grid

的选择(消去勾),以便能够任意设置输入电平位置,或设置输入时钟信号的周期。

3

SOPC_EDA 实验讲义_GW48-PK212/6/2006

4、如图 1-10,1-11 所示,设定仿真时间宽度。选择 File 项及其 End time 选项,在 End time 选择窗中选

择适当的仿真时间域,如可选 50us(50 微秒),以便有足够长的观察时间。

5、加上输入信号。图 1-12 显示了波形编辑窗各按钮的功能。

图1-9 在Options 选项中消去网格对齐 Snap to Grid 的选择(消去勾)

图1-10 设定仿真时间宽度 图1-11 设定仿真时间宽度

在图 1-13 仿真波形中,多路选择器 mux21a 的输入端口 a 和b 分别输入时钟周期为 400ns 和1.2us 的时变信号。由

图可见,当控制端 s 为高电平时,y 的输出为 b 的低频率信号,而当 s 为低电平时,y的输出为 a的高频率信号。

注意,仿真波形文件的建立,一定要十分注意仿真时间区域的设定,以及时钟信号的周期设置,否则即使设计正确也无法获得正确的仿真结果。

如图 1-14 所示,设定了比较合理的仿真时间区域和信号频率,即仿真时间区域不能太小,仿真频率不能太高,即信号周期不能小到与器件的延时相比拟。

图1-12 为输入信号设定必要的测试电平或数据 图1-15 仿真波形文件存盘

图1-13 为输入信号设定必要的输入信号

6、波形文件存盘。选择 File 项及其 Save as 选项,按 OK 键即可。存盘窗(图 1-15)中的波形文件名是默认

的(这里是 mux21a.scf),所以直接存盘即可。

7、运行仿真器。选择 MAX+plusII 项及其中的仿真器 Simulator 选项,点击跳出的仿真器窗口(图 1-16)中

4

SOPC_EDA 实验讲义_GW48-PK212/6/2006

的Start 键。图 1-14 是仿真运算完成后的时序波形。注意,刚进入图 1-14 窗时,应该将最下方的滑标拖向最左侧,

以便可观察到初始波形。

8、观察分析波形。还可以进一步了解信号的延时情况。图 1-14 右侧的竖线是测试参考线,它与鼠标箭头间的时

间差显示在窗口上方的 Interval 小窗中。由图可见输入与输出波形间有一个小的延时量。

图1-14 mux21a 仿真波形 图1-16 运行仿真器

图1-17 打开延时时序分析窗 图1-18 引脚锁定

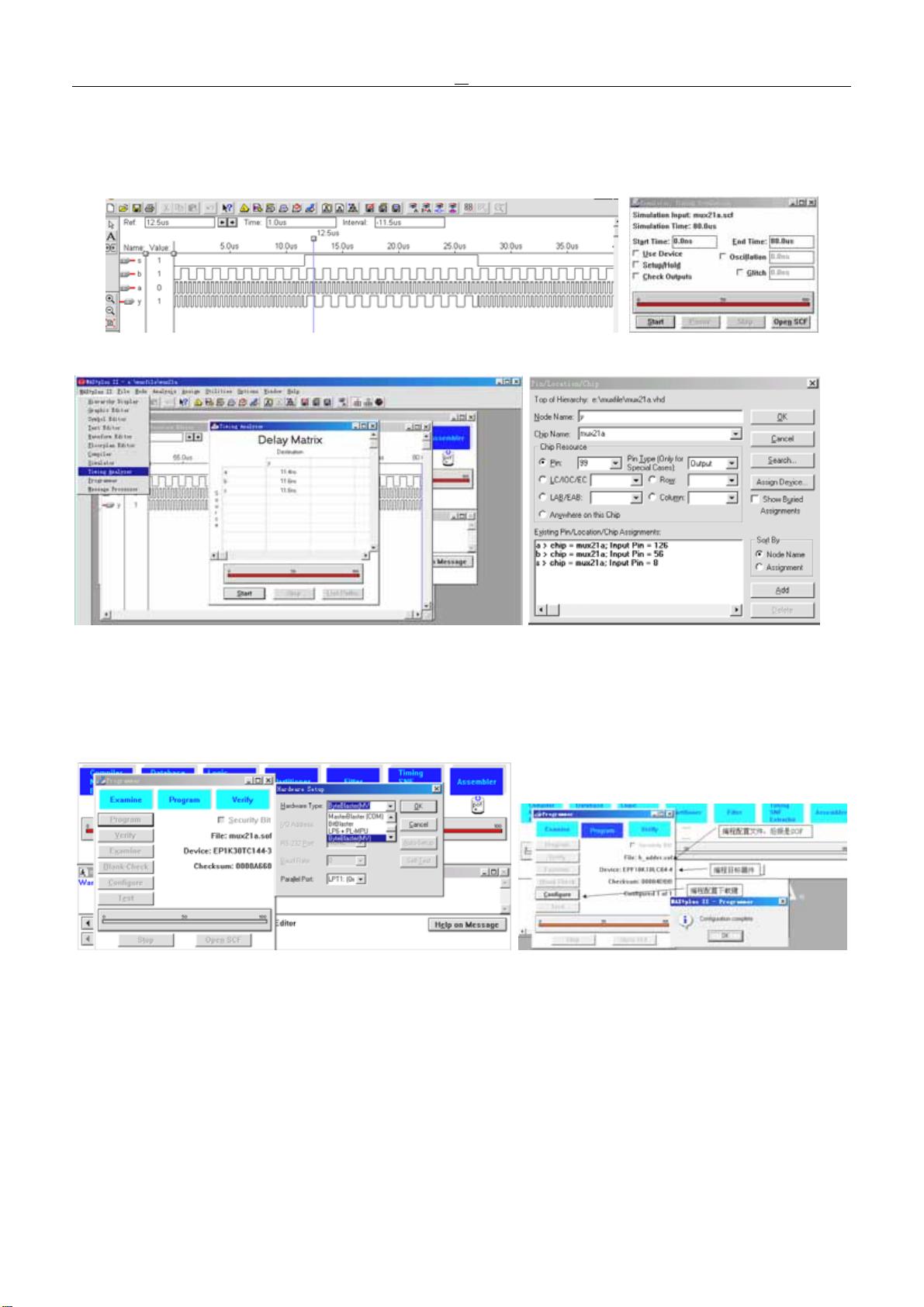

1.5 硬件测试

为在实验系统上验证设计的正确性,完成硬件测试。如果目标器件是 EP1K30,建议选择实验电路模式 5(参考附图

7),用键 1(PIO0)控制信号 s ;a 和 b 分别接 clock5 和 clock0;输出信号 y 接扬声器 spker。通过短路帽选择 clock0 接

256Hz 信号,clock5 接 1024Hz 信号。现在根据以上确定的实验模式锁定多路选择器在目标芯片中的具体引脚。

图1-19 设置编程下载方式 图1-20 向目标器件下载配置文件

首先通过选择“MAX+plus II”Æ“Compiler”菜单,进入编辑窗,然后在“Assign”项中选“Pin / Location / Chip”

选项,在跳出的窗口中的 Node Name 项中输入引脚 a ,这时“Pin Type”项会出现“Input”指示字,表明 a 的引脚性

质是输入,否则将不出现此字。此时在“PIN”项内输入“126”引脚名,再点击右下方的 Add 项,此引脚即设定好了;

以同样方法分别锁定引脚 b、s、y(图 1-18),再点击上方的 OK。此4 个引脚的选择方法是根据附录实验电路模式“NO.5”

设定的。关闭“Pin / Location / Chip”窗后,应点击编辑窗的“Start”,将引脚信息编辑进去。编程和测试的步骤如下:

(1)选 " MAX+PLUSΠ " 项中的“Programmer”项,跳出 Programmer 窗后,选Options 项中的硬件设置项“Hardware

Setup”,在此窗的下拉窗中选“ByteBlaster (MV)”项,点击 OK 即可。(下载方式设定:选择 MAX+plusII 项及其中的

编程器 Programmer 选项,跳出如图 1-19 左侧所示的编程器窗口,然后选择 Options 项的

Hardware Setup 硬件设

置选项,其窗口如图 1-19 左侧所示。在其下拉菜单中选 ByteBlaster(MV)编程方式。此编程方式对应计算机的并

行口下载通道,“MV”是混合电压的意思。将实验板连接好,接好电源,点“Configure”,即进行编程下载。

5

剩余81页未读,继续阅读

资源评论

xxx-xxxx2015-05-01很好,实验箱又可以用了。

xxx-xxxx2015-05-01很好,实验箱又可以用了。

陆沉

- 粉丝: 3

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功