2007 年 C 题 数字存储示波器

本题设计一个数字存储示波器,以 Xilinx 公司 20 万门 FPGA 芯片为核心,

辅以必要的外围电路(包括信号调理、采样保持、内部触发、A/D 转换、D/A

转换和 I/O 模块),利用 VHDL 语言编程,实现了任意波形

数字存储示波器

海军航空工程学院(烟台) 史继炎 何高健 刘恒涛

摘要

本题设计一个数字存储示波器,以 Xilinx 公司 20 万门 FPGA 芯片为核心,

辅以必要的外围电路(包括信号调理、采样保持、内部触发、A/D 转换、D/A

转换和 I/O 模块),利用 VHDL 语言编程,实现了任意波形的单次触发、连续

触发和存储回放功能,并按要求进行了垂直灵敏度和扫描速度的挡位设置。信

号采集时,将外部输入信号经信号调理模块调节到 A/D 电路输入范围,经 A/D

转换后送入 FPGA 内部的双口 RAM 进行高速缓存,并将结果通过 D/A 转换送

给通用示波器进行显示,完成了对中、低频信号的实时采样和高频信号的等效

采样和数据存储回放。经测试,系统整体指标良好,垂直灵敏度和扫描速度等

各项指标均达到设计要求。

关键词:FPGA 实时采样 等效采样

一、方案选择与论证

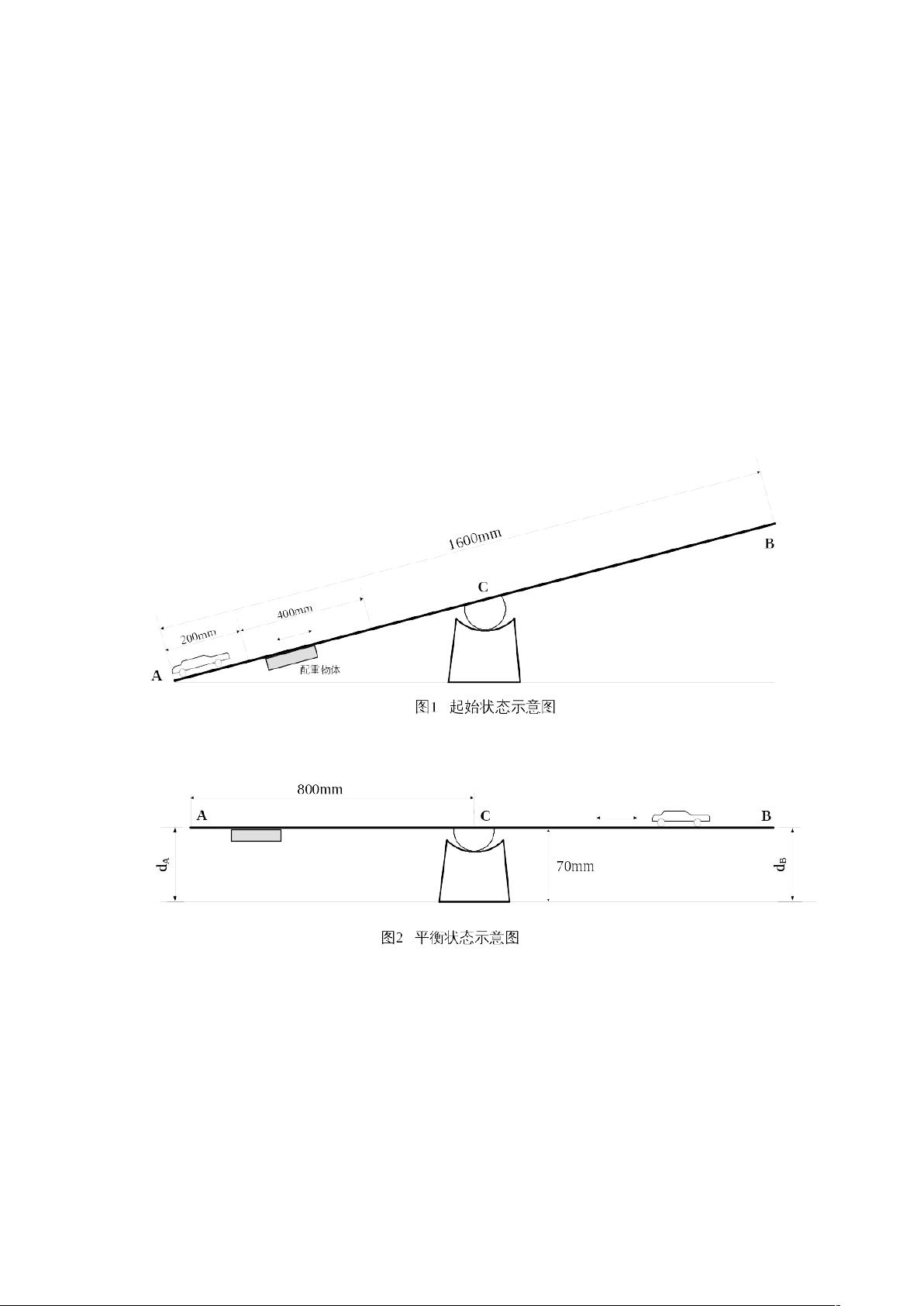

数字存储示波器系统由信号调理电路、采样保持电路、触发电路、

A/D、D/A、X 输出电路、Y 输出电路、控制处理器等组成。

方案一:采用 80C51 单片机为控制核心,其系统框图如图 1。对输入信号

进行放大或衰减后,用外接触发电路产生触发信号,通过 A/D 转换将模拟信号

转换成数字信号,再通过单片机将数据锁存至外部 RAM,然后由单片机控制将

数据送至 D/A 输出。

图 1 方案一系统框图

这种方案结构较为简洁,但在满足题目的实时采样频率的要求下,A/D 的

最高采样速度达 1MHz,由普通单片机直接处理这样速率的数据难以胜任,采