没有合适的资源?快使用搜索试试~ 我知道了~

EC芯片WPC8763L的datasheet

需积分: 14 10 下载量 27 浏览量

2018-06-08

09:37:20

上传

评论 1

收藏 2.37MB PDF 举报

温馨提示

试读

316页

EC芯片WPC8763L的datasheet,WPC8763L Notebook Embedded Controller with SPI Flash Interface

资源推荐

资源详情

资源评论

WPC8763L Notebook Embedded Controller with SPI

TM

Flash Interface

© 2007 Winbond Electronics Corporation www.winbond.com

March 2007

Revision 1.0

WPC8763L Notebook Embedded Controller with SPI

TM

Flash Interface

General Description

The Winbond WPC8763L is a highly integrated embedded

controller (EC) with an embedded RISC core and integrated

advanced functions. It is targeted for a wide range of porta-

ble applications.

The WPC8763L incorporates the CompactRISC

®

CR16CPlus

core (a high-performance 16-bit RISC processor), on-chip

ROM and RAM memories, system support functions and a

Flash Interface Unit (FIU) that interfaces directly with exter-

nal SPI flash memory devices.

System support functions include: watchdog, PWM, timers,

interrupt control, General-Purpose I/O (GPIO) with internal

keyboard matrix scanning, PS/2

®

interface, SMBus

®

inter-

face, UART, high-accuracy analog-to-digital (ADC) and dig-

ital-to-analog (DAC) converters for battery charging, system

control, system health monitoring and analog controls.

The WPC8763L interfaces with the host via an LPC inter-

face.

The WPC8763L is PC01 and ACPI compliant, and offers a

single-chip solution for the most commonly used notebook

PC I/O peripherals.

Outstanding Features

■ Shared BIOS flash memory

■ Support for SPI flash memories

■ Flash page programing support

■ High-accuracy, high-speed ADC

■ Up to 88 GPIO ports (including keyboard scanning)

with a variety of wake-up events

■ 16-bit RISC core, with up to 4 Mbytes of external ad-

dress space, running at up to 25 MHz

■ 128-pin LQFP package

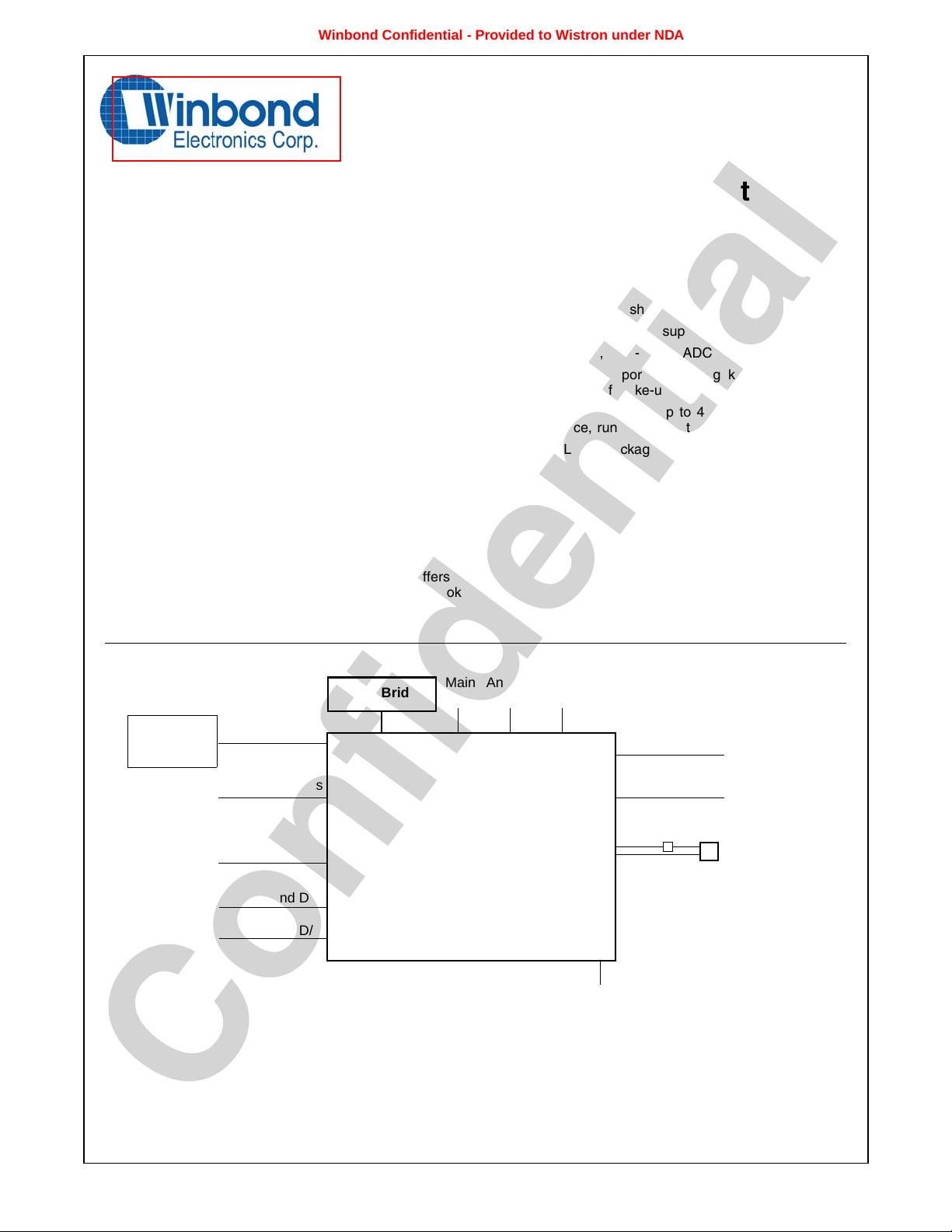

Charger

A/D and D/A

D/A

Brightness

Contrast

South Bridge

Keyboard Matrix

Keyboard

Touch Pad

Mouse

Shared Flash

3 x Fan

PWM

Tacho

12 x 8 - 18 x 8

JTAG

Switch Pad

and LEDs

SPI

WPC8763L

Main

V

DD

Standby

V

CC

System Block Diagram

Analog

V

CC

2x SMBus

3 x PS2

Battery

Panel

Winbond Confidential - Provided to Wistron under NDA

www.winbond.com 2 Revision 1.0

WPC8763L

Features

Embedded Controller Features

■ Processing Unit

— CompactRISC CR16CPlus 16-bit embedded RISC

processor core (the “core”)

— Up to 4 Mbytes of external address space

■ Internal Memory

— 1 Kbyte of ROM

— 4 Kbytes of on-chip RAM

— All memory types can hold both code and data

■ Flash Interface Unit (FIU)

— Up to 4 Mbytes of code and data

— Hardware-protected boot zone block protection

— SPI External Memory

❏ Up to 32 Mbits

❏ Fast Read mode

❏ Page programing support

❏ Configurable clock rate

— Field upgradeable

■ Shared Memory Controller (SHM)

— Supports BIOS (flash) memory sharing with PC host

— Supports host-controlled code download and update

— Memory access protection

LPC System Interface

■ Based on Intel’s LPC Interface Specification Revision

1.1, August 2002

■ I/O, Memory and 8-bit Firmware Memory read and write

cycles, Firmware Memory writes may insert wait cycles

■ Bootable Memory Support

■ Base Address (BADDR1-0) straps to determine the

base address of the index-data register pair

— Alternate base address configurable by the core

■ LPCPD

and CLKRUN support

Embedded Controller System Features

■ Host Interface

— Comprises host interface channels, typically used

for KBC and ACPI Private or Shared EC channels

— 8042 KBC-standard interface (legacy 60h, 64h)

— Two PM interface ports (legacy 62h, 66h; 68h, 6Ch)

— ACPI EC with either Shared or Private interface

through the PM interface

— Two Mailbox areas for host-core communication, up

to 4 Kbytes each; maximum 4 Kbytes total

— Generates IRQ, SMI and SCI

— Provides IRQ1 and IRQ12 support

— Provides Fast Gate A20 and Fast Host reset via firmware

■ Interrupt Control Unit (ICU)

— 31 maskable vectored interrupts (of which eight are

external)

— General-purpose external interrupt inputs through

MIWU

— Enable and pending indication for each interrupt

— Non-maskable interrupt input

■ Multi-Input Wake-Up (MIWU)

— Up to 40 wake-up or interrupt inputs

— Generates wake-up event to PMC (Power Manage-

ment Controller)

— Generates interrupts to ICU

— User-selectable trigger conditions

■ Internal Keyboard Matrix Scanning

— Up to 18 open-collector outputs (at least 12)

— Eight Schmitt inputs with internal pull-ups

■ General-Purpose I/O (GPIO) Ports

— 64 port pins

— I/O pins individually configured as input or output

— Configurable internal pull-up / pull-down resistors

— Outputs individually configured as push-pull or

open-drain

— Two echo inputs with wake-enabled interrupts

— Additional 12 GPIOs with wake-enabled interrupts

— Four GPIOs capable of 12 mA sink current

— Seven GPIOs are accessible to the host

— Optional low-cost external GPIO expansion through

the SensorPath interface

■ PS/2 Interface

— Three external ports: can be used for keyboard,

mouse and an additional pointing device

— Byte-level handling via hardware accelerator

■ Two SMBus (SMB) Interface Modules; each module:

— Is Intel SMBus, Philips I

2

C

®

and ACCESS.bus

compatible

— Is SMBus master and slave

— Supports up to two simultaneous slave addresses

— Supports polling- and interrupt-controlled operations

— Generates a wake-up signal on detection of a Start

condition while in Idle mode

— Supports an optional internal pull-up on SDA and

SCL pins

■ Core Universal Asynchronous Receiver-Transmitter

(CR_UART) Module

— A full-duplex UART channel

— Programmable baud rate

— Data transfer via interrupt or polling

■ Two 16-bit Multi-Function Timer (MFT16) Modules;

each module has:

— Two 16-bit timers with a 5-bit prescaler

— Pulse Width Modulation (PWM), Capture and

Timer/Counter modes

— Capture inputs with programmable edge detection

— An interrupt on compare match

Winbond Confidential - Provided to Wistron under NDA

Revision 1.0 3 www.winbond.com

WPC8763L

Features (Continued)

■ Two Pulse Width Modulation (PWM) Modules

— Group A_PWM: two outputs

— Group B_PWM: one output

■ Timer and Watchdog (TWD)

— 16-bit periodic interrupt timer with 30 µs resolution

and 5-bit prescaler for system tick and periodic

wake-up tasks

— 8-bit watchdog timer with enable/disable

— “Watchdog occurred” flag

— Two watchdog reset options: warm or cold

■ SensorPath

™

Bus Interface

— Single Wire bus master

— Supports up to seven slave devices

— x1, x4 SensorPath clock rate support

■ Analog-to-Digital Converter (ADC)

— Four channels, with 8-bit resolution

— 125 µs conversion time

— External voltage reference

■ Digital-to-Analog Converter (DAC)

— Two channels, 8-bit resolution

— 1 µs conversion time for 50 pF load

— Full output range from AGND to AVCC

■ Development Support

— Interface to debugger via Nexus 5001 interface

❏ Physical connection using JTAG

❏ On-board Debug mode with eight hardware

breakpoints

❏ Embedded memory programing via JTAG with

content read protection

■ Core Access to Host Modules

— Enabled via lock mechanism

Host Function Features

■ Mobile System Wake-Up Control (MSWC)

— Software-controlled off events

— Event routing to IRQ, SMI

or PWUREQ

■ Supports Microsoft

®

Advanced Power Management

(APM) Specifications Revision 1.2, February 1996

— Generates the System Management Interrupt (SMI)

■ PC01 Rev 1.0 and ACPI 3.0 Compliant

— PnP configuration register structure

— Flexible resource allocation for all logical devices

❏ Relocatable base address

❏ 15 IRQ routing options

Clocking, Supply and Package Information

■ Strap Input-Controlled Operating Modes:

— Shared BIOS memory mode

— TRI-STATE

®

mode

— Development mode

■ Clocks

— Single 32.768 KHz crystal oscillator

— On-chip high-frequency clock generator

— Either 32.768 KHz or CR16CPlus clock out

■ Testability

— XOR-tree structure includes all device pins (except

supply, A/D, D/A, and crystal oscillator pins), select-

ed at power-up by strap inputs

— TRI-STATE device pins, selected at power-up by

strap input (TRIS

)

■ Power Supply

— 3.3V supply operation

— 5V tolerance and back-drive protection on all pins

(except crystal oscillator, A/D, D/A, LPC bus, and

SPI flash pins)

— Separate supply for host I/F (V

DD

) and EC functions

(V

CC

)

— Reduced power consumption capability

— Software- or hardware-switched power modes:

❏ Active mode

❏ Active mode executing WAIT

❏ Idle

❏ Deep Idle

— Automatic wake-up on system events

■ Package Options

— 128-pin LQFP package

Winbond Confidential - Provided to Wistron under NDA

www.winbond.com 4 Revision 1.0

WPC8763L

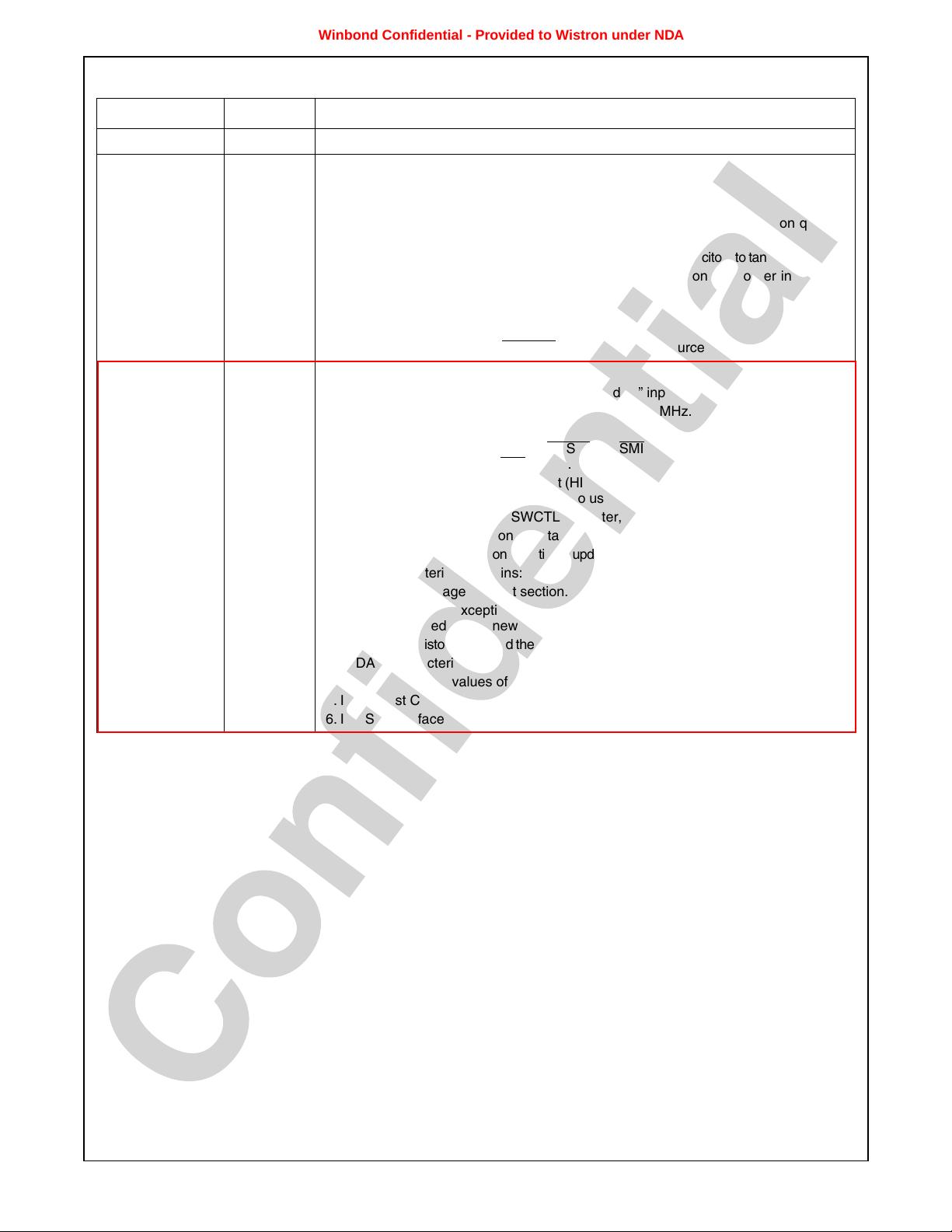

Datasheet Revision Record

Revision Date Status Comments

October 4, 2006

Revision 0.96 First Preliminary Datasheet.

March 12, 2007

Revision 1.0 Datasheet revision. List of changes:

1. In cover page and Features:

1.1 Changed the order of the Host Function Features.

2. In Detailed Signal/Pin Descriptions, PS/2 Interface, added clarification on quasi-bi-

directional buffers.

3. In Decoupling and Filter Capacitors, changed the 10-47

µ

F capacitors to tantalum/ceramic.

4. In SPI Flash Interface, UMA section, added clarification on byte order in UMA Ex-

tended Write transactions.

5. In MIWU, Input Assignments table:

5.1 Improved readability of footnote #3.

5.2 Added footnote #4 to LRESET

Active Wake-Up source

March 12, 2007

(cont.)

Revision 1.0

(cont.)

Datasheet revision. List of changes (cont.):

6. In PWM Block Diagram, reversed the “R” and “S” inputs of the flip-flops.

7. In SPI, Features, changed the data clock rate to 10 MHz.

8. In PM Channels:

8.1 In Enhanced PM Mode, IRQ, ECSCI

and SMI Control figure, changed the signal

names related to the SMI

output.

8.2 To the description of SCIPOL bit (HIPMnCTL register) and SMIPOL bit (HIPMnIC

register), added recommendation to use active low polarity setting.

9. In MSWC Core registers, MSWCTL1 register, added clarification to LPCRSTA bit.

10. In Booter Data, Header Contents table, updated footnote #2.

11. In Power Supply Current Consumption... updated the I

DD

, I

DDLP

, I

CC

and I

CCW

parameters.

12. In DC Characteristics of Pins:

12.1Added Leakage Current section.

12.2In Notes and Exceptions, updated item #1 and removed items #4 and #5 (they

are replaced by the new Leakage Current section).

13. In Internal Resistors, changed the Min. Max. values for the R

PU80

and R

PD80

parameters.

14. In DAC Characteristics:

14.1Changed the values of output resistance (R

S

).

15. In AC Test Conditions, added C

L

= 15 pF for CLKOUT.

16. In PS/2 Interface Timing, changed the “guaranteed by” for t

PSCLKL

and t

PSCLKH

.

Winbond Confidential - Provided to Wistron under NDA

Revision 1.0 5 www.winbond.com

WPC8763L

Table of Contents

Features.............................................................................................................................................................. 2

Datasheet Revision Record ............................................................................................................................... 4

1.0

Introduction

1.1 GENERAL DESCRIPTION ........................................................................................................ 18

1.1.1 System Connections .................................................................................................... 18

1.1.2 Power Management .................................................................................................... 18

1.2 INTERNAL ARCHITECTURE .................................................................................................... 18

1.3 OPERATING ENVIRONMENTS ................................................................................................ 19

1.3.1 IRE Environment ......................................................................................................... 19

1.3.2 OBD Environment ........................................................................................................ 19

1.4 MEMORY MAP .......................................................................................................................... 19

1.4.1 Core Address Domain Memory Map ........................................................................... 19

1.4.2 Host Address Domain Memory Map ............................................................................ 20

1.4.3 Core Access to Host Modules ..................................................................................... 20

2.0

Signal/Pin Description and Configuration

2.1 CONNECTION DIAGRAM ......................................................................................................... 22

2.2 BUFFER TYPES ........................................................................................................................ 23

2.3 PIN MULTIPLEXING ................................................................................................................. 23

2.4 DETAILED SIGNAL/PIN DESCRIPTIONS ................................................................................ 25

2.4.1 Host Interface .............................................................................................................. 25

2.4.2 SPI Flash Interface ...................................................................................................... 26

2.4.3 Internal Keyboard Scan ............................................................................................... 26

2.4.4 General-Purpose I/O (GPIO) ....................................................................................... 27

2.4.5 Host General-Purpose I/O (HGPIO) ............................................................................ 28

2.4.6 Analog Interface ..........................................................................................................28

2.4.7 PS/2 Interface .............................................................................................................. 28

2.4.8 SMBus Interface .......................................................................................................... 29

2.4.9 Timers and PWM ......................................................................................................... 29

2.4.10 SensorPath Interface ................................................................................................... 29

2.4.11 CR_UART .................................................................................................................... 29

2.4.12 JTAG ........................................................................................................................... 29

2.4.13 Miscellaneous .............................................................................................................. 30

2.4.14 Clocks .......................................................................................................................... 30

2.4.15 Strap Configuration and Testing .................................................................................. 30

2.4.16 Power and Ground ...................................................................................................... 31

2.5 INTERNAL PULL-UP AND PULL-DOWN RESISTORS ............................................................ 32

2.5.1 Internal Keyboard Scan ............................................................................................... 32

2.5.2 General-Purpose I/O (GPIO) ....................................................................................... 32

2.5.3 Host General-Purpose I/O (HGPIO) ............................................................................ 33

2.5.4 PS/2 Interface .............................................................................................................. 33

2.5.5 SMBus Interface .......................................................................................................... 33

2.5.6 Timers .......................................................................................................................... 34

2.5.7 SensorPath Interface ................................................................................................... 34

Winbond Confidential - Provided to Wistron under NDA

剩余315页未读,继续阅读

资源评论

pingcong

- 粉丝: 8

- 资源: 33

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- mmqrcode1714153659780.png

- Screenshot_2024-04-27-06-08-58-486_com.baidu.xin.aiqicha.jpg

- 基于Javaweb+Tomcat+MySQL的大学生公寓管理系统+sql文件.zip

- 实训作业基于javaweb的订单管理系统源码+数据库+实训报告.zip

- 多机调度问题贪心算法基于最小堆和贪心算法求解多机调度问题.zip

- 基于同态加密技术的匿名电子投票系统源码.zip

- Pyqt5项目框架-PyQt项目开发实践

- 基于C通过MQTT的智能农业大棚管理系统(本科毕业设计)

- python+CNN的网络入侵检测算法源码.zip

- js 实现记住密码功能 js.cookie.min.js

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功