1

PhoenixBIOS 4.0 Release 6.0

POST Tasks and Beep Codes

When you turn on or reset an IBM-compatible PC, the BIOS first performs a

number of tasks, called the Power-On-Self-Test (POST). These tasks test

and initialize the hardware and then boot the Operating System from the hard

disk.

At the beginning of each POST task, the BIOS outputs the test-point error

code to I/O port 80h. Programmers and technicians use this code during

trouble shooting to establish at what point the system failed and what routine

was being performed. Some motherboards are equipped with a seven-

segment LED display that displays the current value of port 80h. For

production boards which do not contain the LED display, you can purchase

an installable "Port 80h" card that performs the same function. If the BIOS

detects a terminal error condition, it issues a terminal-error beep code (See

following), attempts to display the error code on upper left corner of the

screen and on the port 80h LED display, and halts POST. It attempts

repeatedly to write the error to the screen. This attempt may "hash" some

CGA displays.

If the system hangs before the BIOS can process the error, the value

displayed at the port 80h is the last test performed. In this case, the screen

does not display the error code.

Copyright © 1997 by Phoenix Technologies Ltd.

All Rights Reserved

Phoenix Technologies Ltd.

Desktop Division

135 Technology Drive

Irvine, CA 92618

http://www.phoenix.com

Terminal POST Errors

There are several POST routines that require success to finish POST. If they

fail, they issue a POST Terminal Error and shut down the system. Before

shutting down the system, the error handler issues a beep code signifying the

test point error, writes the error to port 80h, attempts to initialize the video,

and writes the error in the upper left corner of the screen (using both mono

and color adapters).

The routine derives the beep code from the test point error as follows:

1. The 8-bit error code is broken down to four 2-bit groups.

2. Each group is made one-based (1 through 4) by adding 1.

3. Short beeps are generated for the number in each group.

Example:

Testpoint 16h = 00 01 01 10 = 1-2-2-3 beeps

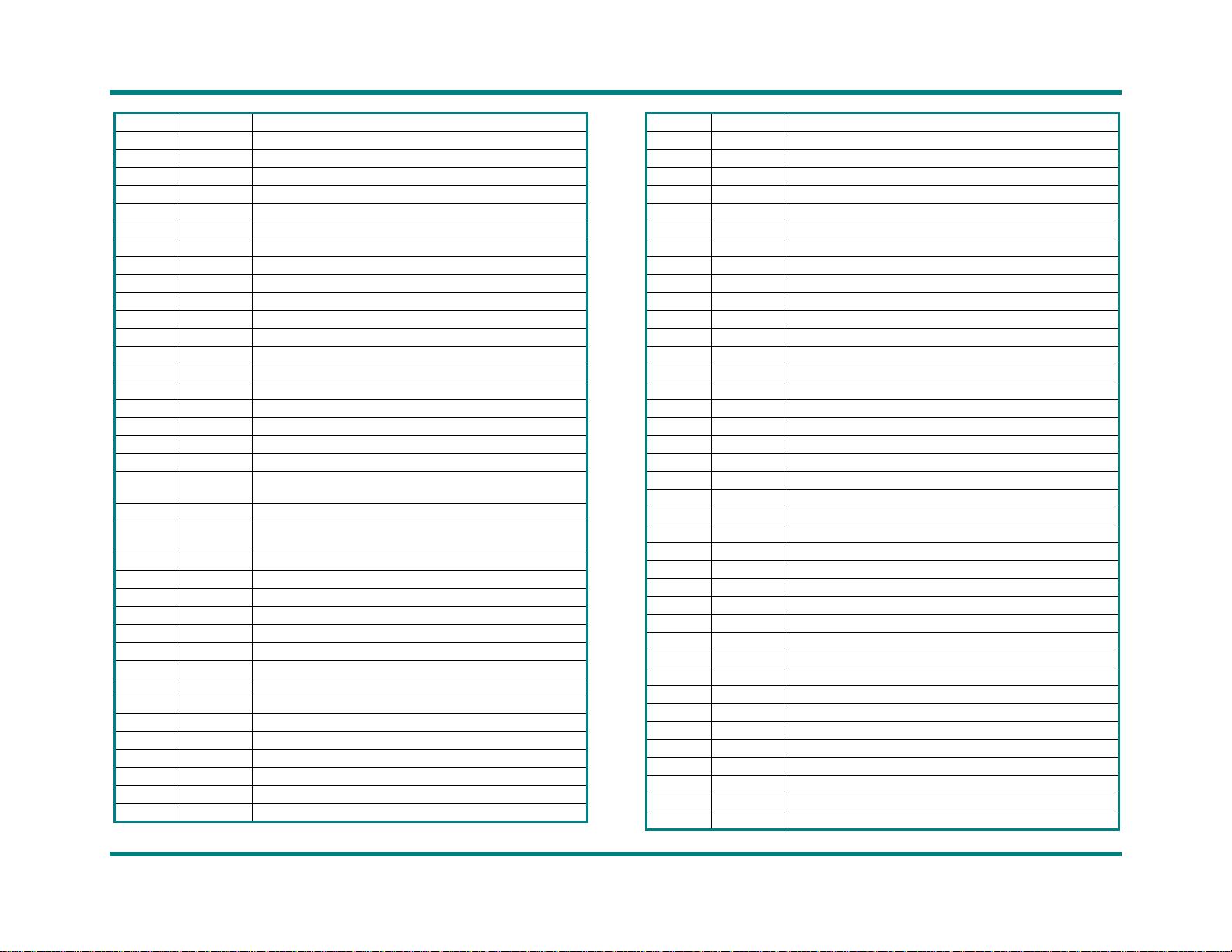

POST Task Routines

The following is a list of the Test Point codes written to port 80h at the start

of each routine, the beep codes issued for terminal errors, and a description

of the POST routine. Unless otherwise noted, these codes are valid for

PhoenixBIOS 4.0 Release 6.0.

NOTE: The following routines are sorted by their test point numbers

assigned in the BIOS code. Their actual order as executed during POST can

be quite different.

Code Beeps POST Routine Description

02h Verify Real Mode

03h Disable Non-Maskable Interrupt (NMI)

04h Get CPU type

06h Initialize system hardware

08h Initialize chipset with initial POST values

09h Set IN POST flag

0Ah Initialize CPU registers

0Bh Enable CPU cache

0Ch Initialize caches to initial POST values

0Eh Initialize I/O component