没有合适的资源?快使用搜索试试~ 我知道了~

内存的原理和时序(SDRAM、DDR、DDR-Ⅱ、Rambus+DRAM)

温馨提示

试读

41页

内存的原理和时序(SDRAM、DDR、DDR-Ⅱ、Rambus+DRAM)

资源推荐

资源详情

资源评论

第二章 DDR SDRAM 的原理和时序

DDR SDRAM 全称为 Double Data Rate SDRAM,中文名为“双倍数据流 SDRAM”。DDR SDRAM 在原

有的 SDRAM 的基础上改进而来。也正因为如此,DDR 能够凭借着转产成本优势来打败昔日的对手

RDRAM,成为当今的主流。由于 SDRAM 的结构与操作在前一章已有详细阐述,所以本文只着重讲讲 DDR

的原理和 DDR SDRAM 相对于传统 SDRAM(又称 SDR SDRAM)的不同。

DDR SDRAM可在一个时钟周期内传送两次数据

2.1 DDR 的基本原理

有很多文章都在探讨 DDR 的原理,但似乎也不得要领,甚至还带出一些错误的观点。首先我们

看看一张 DDR 正规的时序图。

DDR SDRAM 读操作时序图

从中可以发现它多了两个信号: CLK#与 DQS,CLK#与正常 CLK 时钟相位相反,形成差分时钟信

号。而数据的传输在 CLK 与 CLK#的交叉点进行,可见在 CLK 的上升与下降沿(此时正好是 CLK#的上

升沿)都有数据被触发,从而实现 DDR。在此,我们可以说通过差分信号达到了 DDR 的目的,甚至讲

CLK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说。

之所以能实现 DDR,还要从其内部的改进说起。

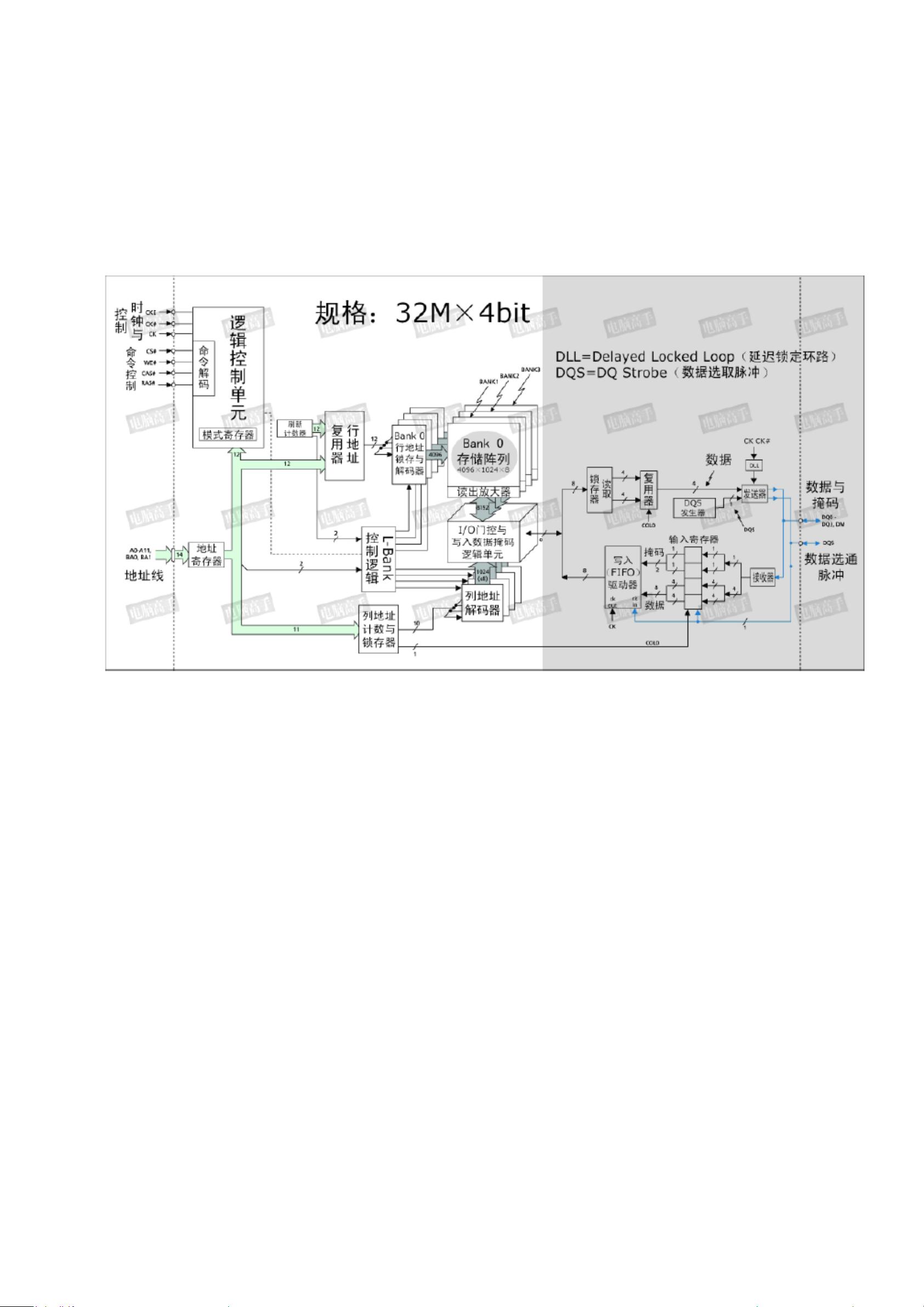

DDR 内存芯片的内部结构图,注意比较上文中 SDRAM 的结构图

这也是一颗 128Mbit 的内存芯片,标称规格也与前文的 SDRAM 一样为 32×4bit。从图中可以看

出来,白色区域内与 SDRAM 的结构基本相同,但请注意灰色区域,这是与 SDRAM 的不同之处。

首先就是内部的 L-Bank 规格。SDRAM 中 L-Bank 存储单元的容量与芯片位宽相同,但在 DDR SDRAM

中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解 SDRAM 时“芯片位宽=

存储单元容量”的公式了。也因此,真正的行、列地址数量也与同规格 SDRAM 不一样了。

以本芯片为例,在读取时,L-Bank 在内部时钟信号的触发下一次传送 8bit 的数据给读取锁存

器,再分成两路 4bit 数据传给复用器,由后者将它们合并为一路 4bit 数据流,然后由发送器在 DQS

的控制下在外部时钟上升与下降沿分两次传输 4bit 的数据给北桥。这样,如果时钟频率为 100MHz,

那么在 I/O 端口处,由于是上下沿触发,那么就是传输频率就是 200MHz。

现在大家基本明白 DDR SDRAM 的工作原理了吧,这种内部存储单元容量(也可以称为芯片内部

总线位宽)=2×芯片位宽(也可称为芯片 I/O 总线位宽)的设计,就是所谓的两位预取(2-bit

Prefetch),有的公司则贴切的称之为 2-n Prefetch(n 代表芯片位宽)。

2.2 DDR SDRAM 与 SDRAM 的不同

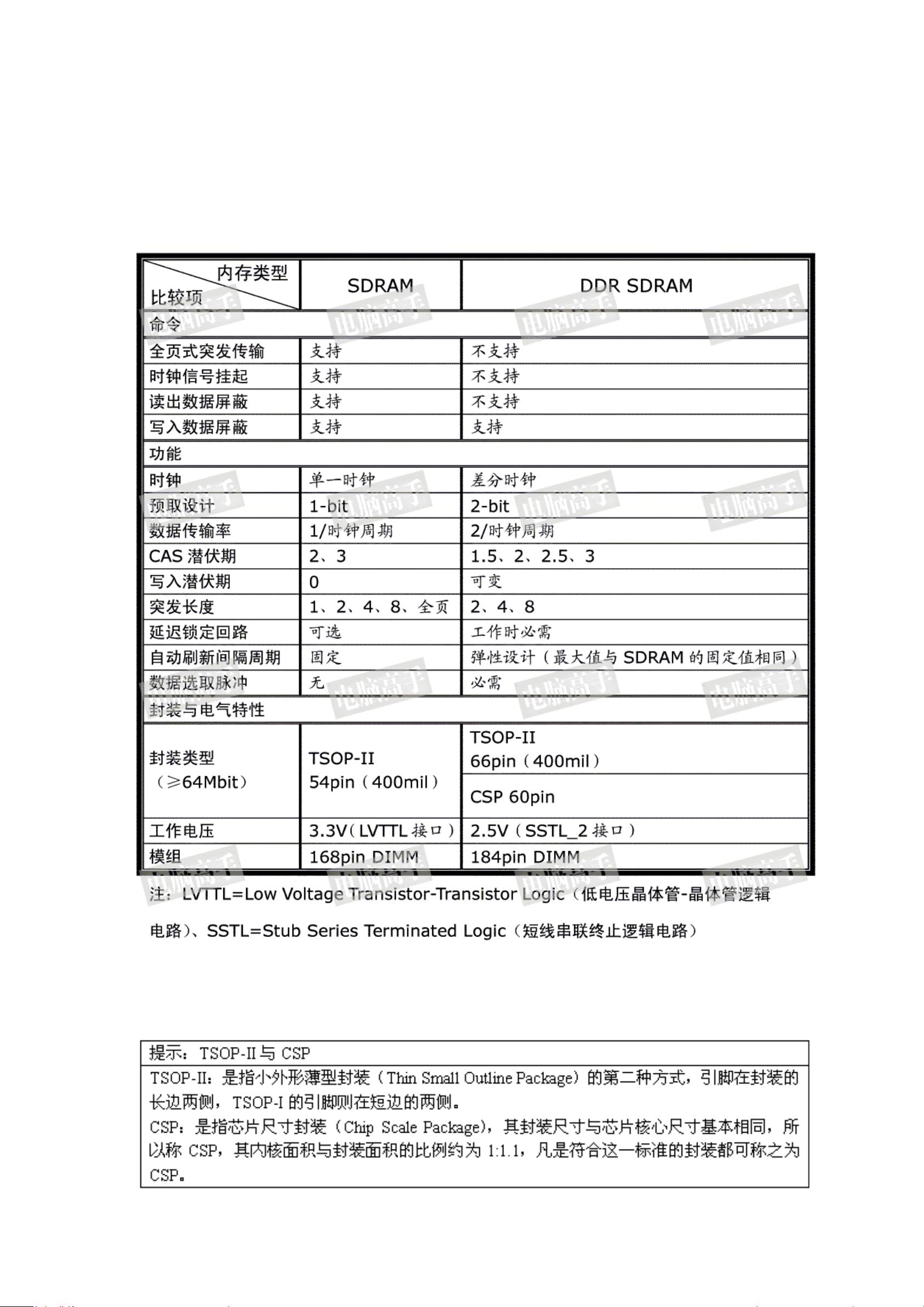

DDR SDRAM 与 SDRAM 的不同主要体现在以下几个方面,如下表。

DDR SDRAM 与 SDRAM 的主要不同对比表

DDR SDRAM 与 SDRAM 一样,在开机时也要进行 MRS,不过由于操作功能的增多,DDR SDRAM 在 MRS

之前还多了一 EMRS 阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存

器控制着 DLL 的有效/禁止、输出驱动强度、QFC 有效/无效等。

由于 EMRS 与 MRS 的操作方法与 SDRAM 的 MRS 大同小异,在此就不再列出具体的模式表了,有

兴趣的话可查看相关的 DDR 内存资料。下面我们就着重说说 DDR SDRAM 的新设计与新功能。

2.3 差分时钟

差分时钟(参见上文“DDR SDRAM 读操作时序图” )是 DDR 的一个必要设计,但 CK#的作用,

并不能理解为第二个触发时钟(你可以在讲述 DDR 原理时简单地这么比喻),而是起到触发时钟校准

的作用。

由于数据是在 CK 的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以

确保数据的正确传输,这就要求 CK 的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等

原因,CK 上下沿间距可能发生变化,此时与其反相的 CK#就起到纠正的作用(CK 上升快下降慢,CK#

则是上升慢下降快)。而由于上下沿触发的原因,也使 CL=1.5 和 2.5 成为可能,并容易实现。

与 CK 反相的 CK#保证了触发时机的准确性

2.4 数据选取脉冲(DQS)

DQS 是 DDR SDRAM 中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输

周期,并便于接收方准确接收数据。每一颗芯片都有一个 DQS 信号线,它是双向的,在写入时它用来

传送由北桥发来的 DQS 信号,读取时,则由芯片生成 DQS 向北桥发送。完全可以说,它就是数据的同

步信号。

在读取时,DQS 与数据信号同时生成(也是在 CK 与 CK#的交叉点)。而 DDR 内存中的 CL 也就是

从 CAS 发出到 DQS 生成的间隔,数据真正出现在数据 I/O 总线上相对于 DQS 触发的时间间隔被称为

tAC。注意,这与 SDRAM 中的 tAC 的不同。实际上,DQS 生成时,芯片内部的预取已经完毕了,tAC 是

指上文结构图中灰色部分的数据输出时间,由于预取的原因,实际的数据传出可能会提前于 DQS 发生

(数据提前于 DQS 传出)。由于是并行传输,DDR 内存对 tAC 也有一定的要求,对于 DDR266,tAC 的

允许范围是±0.75ns,对于 DDR333,则是±0.7ns,有关它们的时序图示见前文,其中 CL 里包含了一

段 DQS 的导入期。

DQS 在读取时与数据同步传输,那么接收时也是以 DQS 的上下沿为准吗?不,如果以 DQS 的上

下沿区分数据周期的危险很大。由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一

定的时间范围内,数据在各 I/O 端口的出现时间可能有快有慢,会与 DQS 有一定的间隔,这也就是为

什么要有一个 tAC 规定的原因。而在接收方,一切必须保证同步接收,不能有 tAC 之类的偏差。这样

剩余40页未读,继续阅读

资源评论

Alex&Yuan2017-12-22介绍挺不错的,不错的普及材料。

Alex&Yuan2017-12-22介绍挺不错的,不错的普及材料。 dabbler_zhu2012-06-29介绍挺不错的,不错的普及材料。

dabbler_zhu2012-06-29介绍挺不错的,不错的普及材料。

BIT工匠

- 粉丝: 19

- 资源: 36

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功