金石 东南大学 移动通信国家重点实验室 教授

潘晶 NI Lead User Program Manager

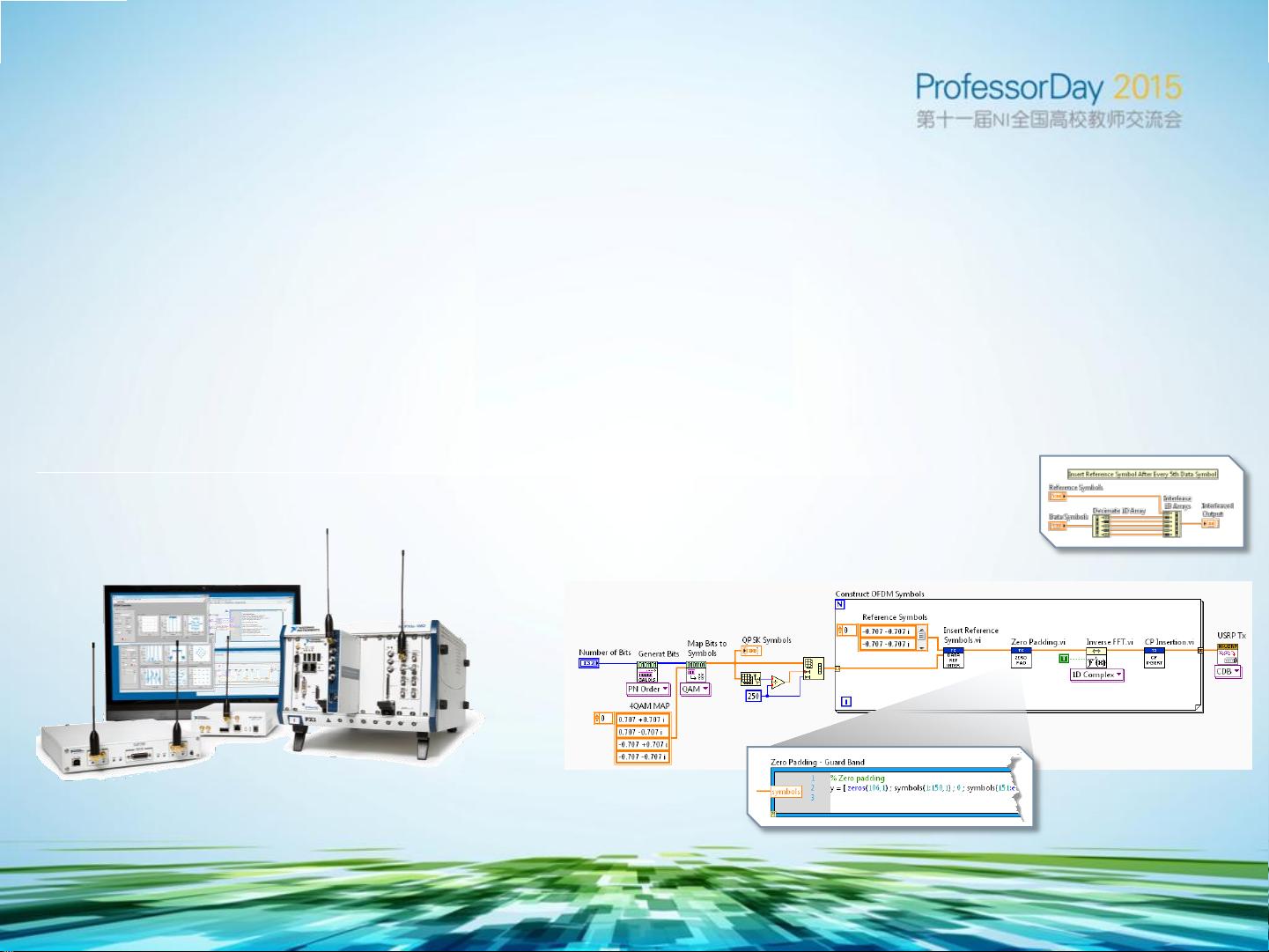

基于NI平台的5G与软件定义无线电创新

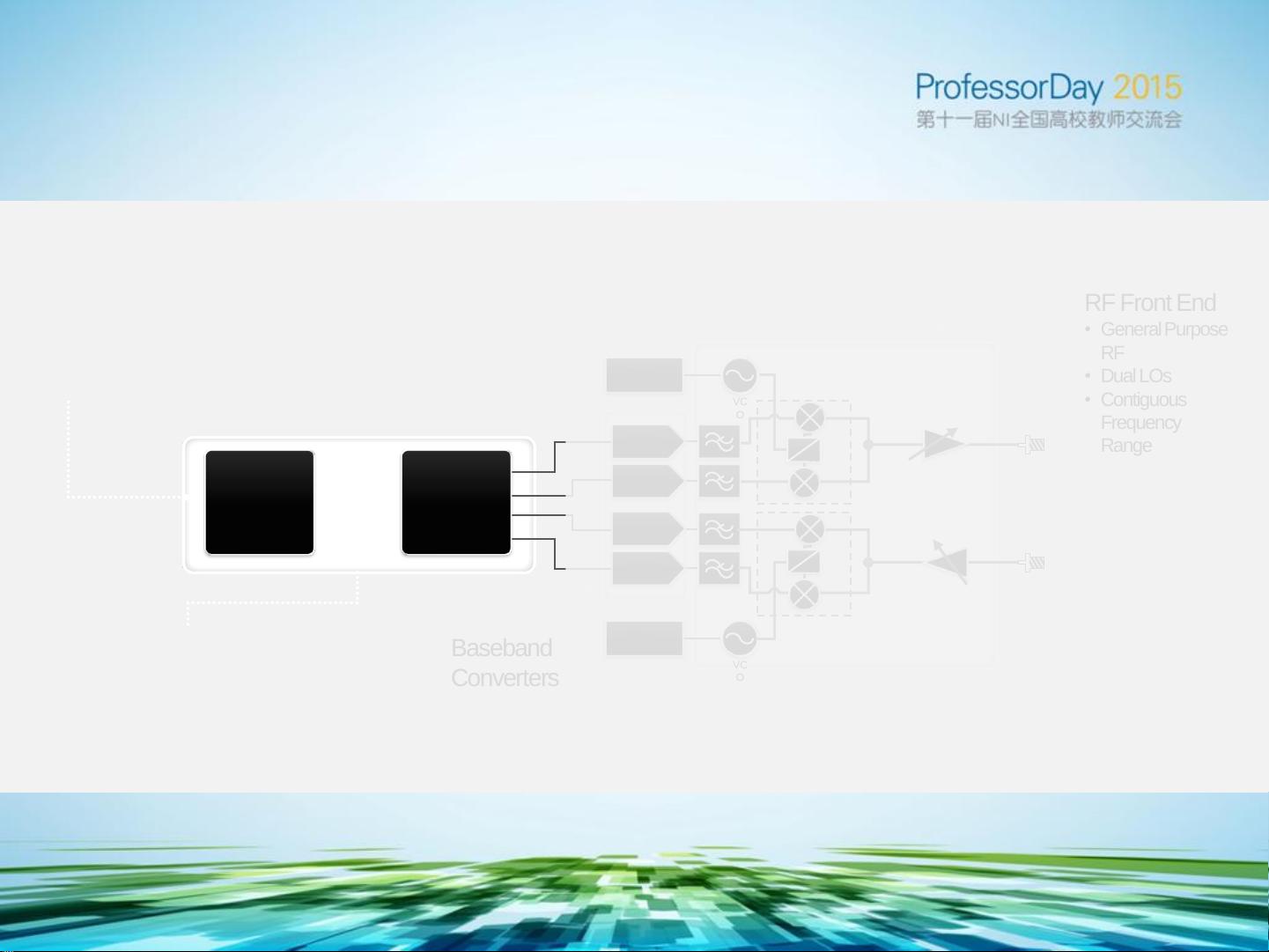

Software Defined Radio Architecture

CPU

GPP

FPGA

DSP

D/A

D/A

D/A

D/A

VC

O

PLL

VC

O

PLL

90

0

90

0

Host Connection

Determines Streaming Bandwidth

Ex. Gigabit E-net, PCIe

Multi-Processor

Subsystem

• Physical Layer (PHY)

• ex FPGA

Host processor

• Medium Access Control

(MAC) – Rx/Tx control

• ex. Multi-core CPU

Baseband

Converters

RF Front End

• General Purpose

RF

• Dual LOs

• Contiguous

Frequency

Range

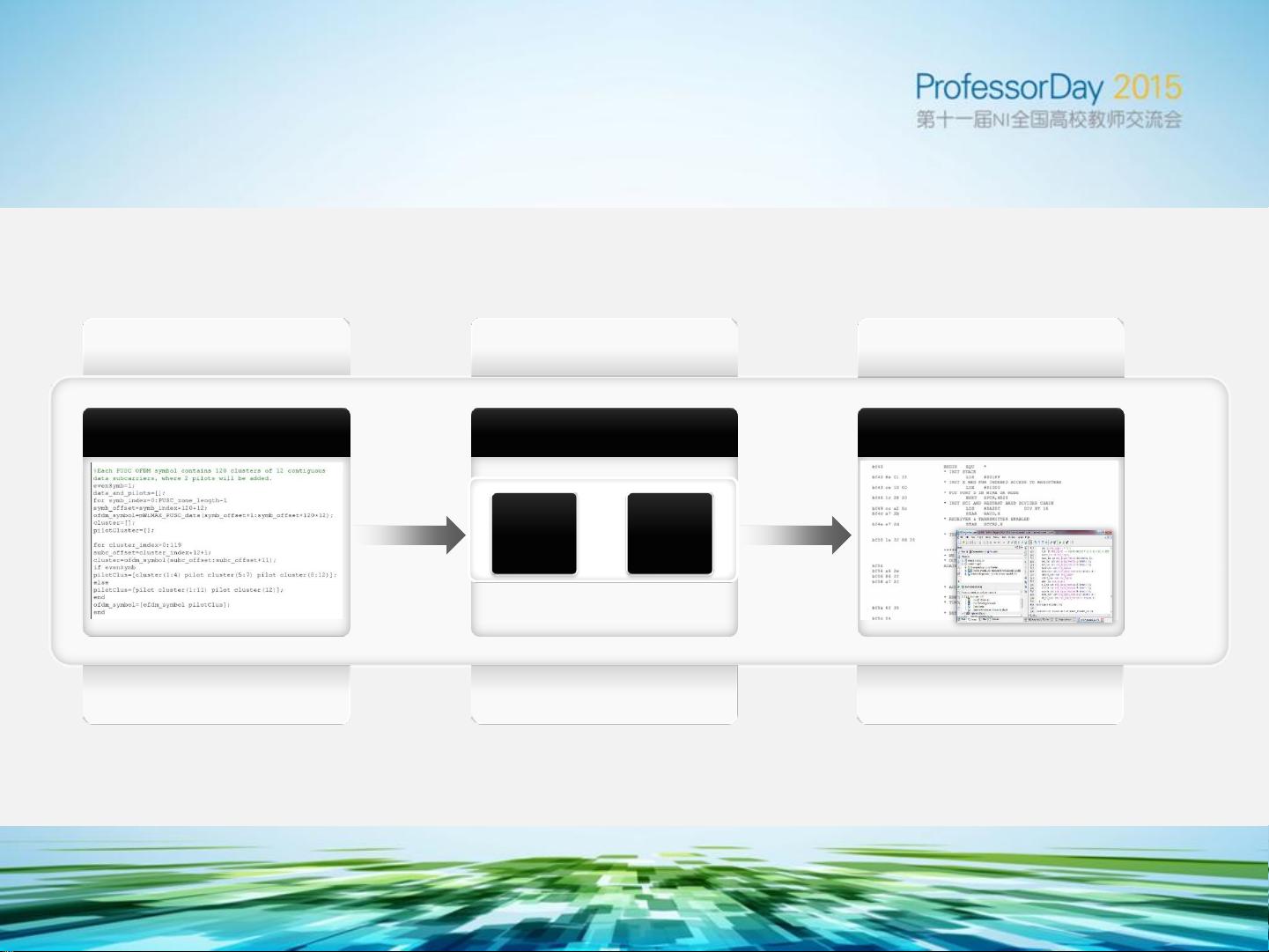

Today’s Development Challenge

• SDR development requires multiple, disparate software tools

• Software tools don’t address system design

Tools

• Math (.m files)

• Simulation (Hybrid)

• User Interface (HTML)

• FPGA (VHDL, Verilog)

• Host Control (C, C++, .NET)

• DSP (Fixed Point C,

Assembly)

• H/W Driver (C, Assembly)

• System Debug

• Long learning curves

• Limited reuse

• Need for “specialists”

• Increased costs

• Increased time-to-result

Targets

FPGAs

Multicore

Processors

The Challenge with Existing Tools

Disjointed path from concept to real-world signal

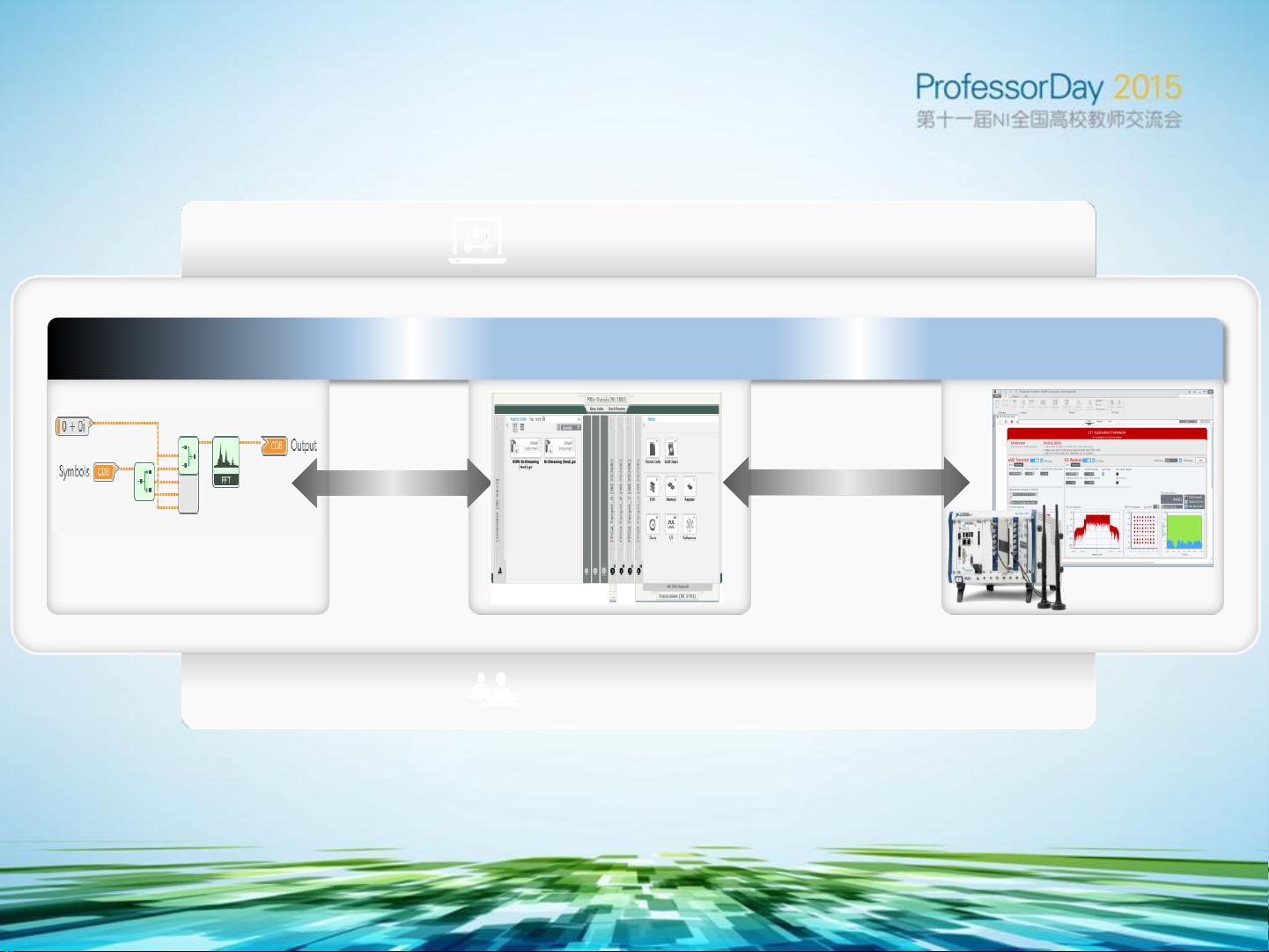

One Standard Tool

System Mapping

System Implementation

Algorithm Development

System Design Team

Floating

Point

Model

Design

Specifications

No Standard. No Tools

No Standard. Many Tools

Research Team Implementation Team

CPU

GPP

FPGA

DSP

The Ideal Solution

One continuous design flow that unifies the disparate design teams

Single, Cohesive Toolchain

System Mapping

System Implementation

Algorithm Development

Collaborative Design Team

Iterative

Modeling

Rapid hardware

mapping

exploration