FACT.C流水线相关性分析

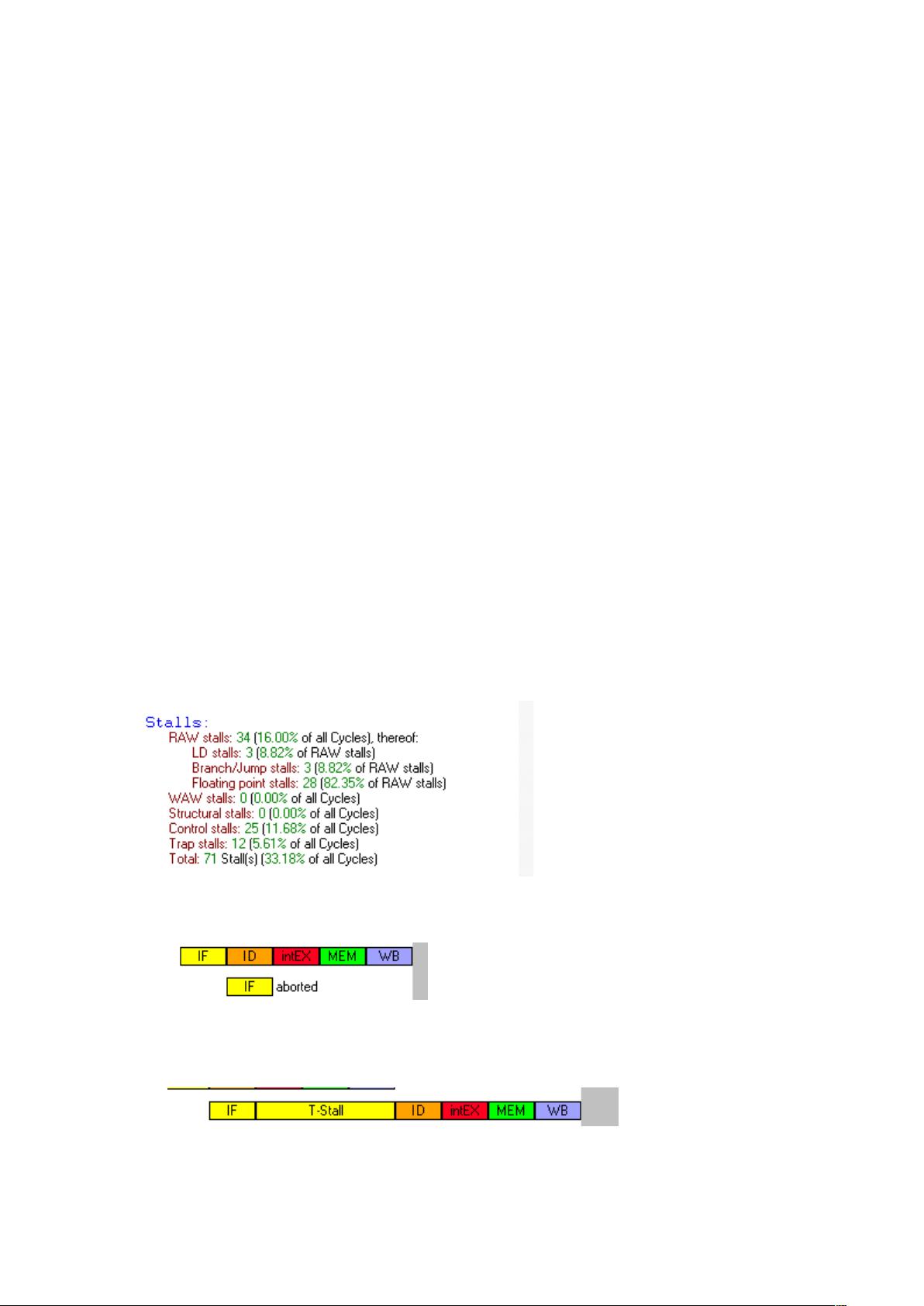

在计算机体系结构中,指令流水线是一种提高处理器性能的关键技术,它通过将指令的执行分解为多个阶段,使得多条指令可以在同一时间内并行处理。然而,流水线中会出现一些现象,导致性能下降,这些现象被称为相关性。本实验通过使用WINDLX模拟器,对三种主要的相关性进行了分析,即结构相关、数据相关和控制相关。 结构相关是指当处理器的不同部分在同一时间需要共享相同的硬件资源时发生的冲突。例如,两个指令都需要同一个ALU(算术逻辑单元)进行运算,就会发生结构相关。在实验中,Fact.s程序中结构相关出现了0次,这意味着该程序的指令序列并未直接导致这种类型的冲突。 数据相关则发生在一条指令的结果被另一条指令所需,而这两条指令的执行顺序又不是严格串行的情况下。例如,RAW(Read-After-Write)相关,指令A写入数据后,指令B立即尝试读取该数据。实验显示Fact.s中数据相关出现了17次,这表明在流水线执行过程中,有17个地方存在数据依赖,需要通过某种方式来解决。 控制相关通常与分支和跳转指令有关,当处理器需要根据前一条指令的结果来决定下一条指令的地址时,可能会出现控制相关。例如,Jal(跳转并链接)、Bnez(条件分支)和J(无条件跳转)指令在实验中引起了控制相关的例子。实验中控制相关共发生了37次,显示了分支和跳转指令对流水线性能的影响。 实验还探讨了增加特定硬件资源,如浮点运算部件,对性能的影响。在未增加浮点部件时,处理器可能无法高效处理浮点运算,但实验结果显示,即使增加了部件,性能也没有显著提升,反而浪费了资源,这可能是因为实验程序中的浮点运算不多,新增部件并未充分利用。 FORWARD部件用于解决数据相关,它能提前传递计算结果,减少等待时间。实验中,没有FORWARD部件时,数据相关导致了多次流水线暂停(STALL)。而添加FORWARD部件后,RAW STALL减少了65次,表明FORWARD部件显著提高了流水线效率。 转移指令的执行也影响流水线性能。转移成功时,需要额外的时钟周期来更新指令指针,而在转移不成功时,流水线可以连续运行,不产生额外开销。 流水线技术可以提高处理器的吞吐量,但也带来了相关性问题。通过增加硬件资源、优化数据传输和预测控制流,可以缓解这些问题。尽管本实验中并未涉及分支预测等高级技术,但它们在实际处理器设计中是解决控制相关的重要手段。理解并解决这些相关性是优化处理器性能的关键步骤,对于提升计算机系统的整体效率具有重要意义。

剩余8页未读,继续阅读

xiao_QP2012-10-01正好是老师要求的实验,先拿来参考了,然后在自己做一遍实验

xiao_QP2012-10-01正好是老师要求的实验,先拿来参考了,然后在自己做一遍实验

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功