西安电子科技大学

国家级精品课程数字电路与系统设计

国家级精品课程数字电路与系统设计

第 8 章 存储器和可编程逻辑器件

本章主要内容

半导体存储器

随机存取存储器

存储器容量的扩展

可编程逻辑器件

现场可编程逻辑阵列 (FPLA)

可编程阵列逻辑( PAL )

只读存储器

西安电子科技大学

国家级精品课程数字电路与系统设计

国家级精品课程数字电路与系统设计

1. 只读存储器( ROM )

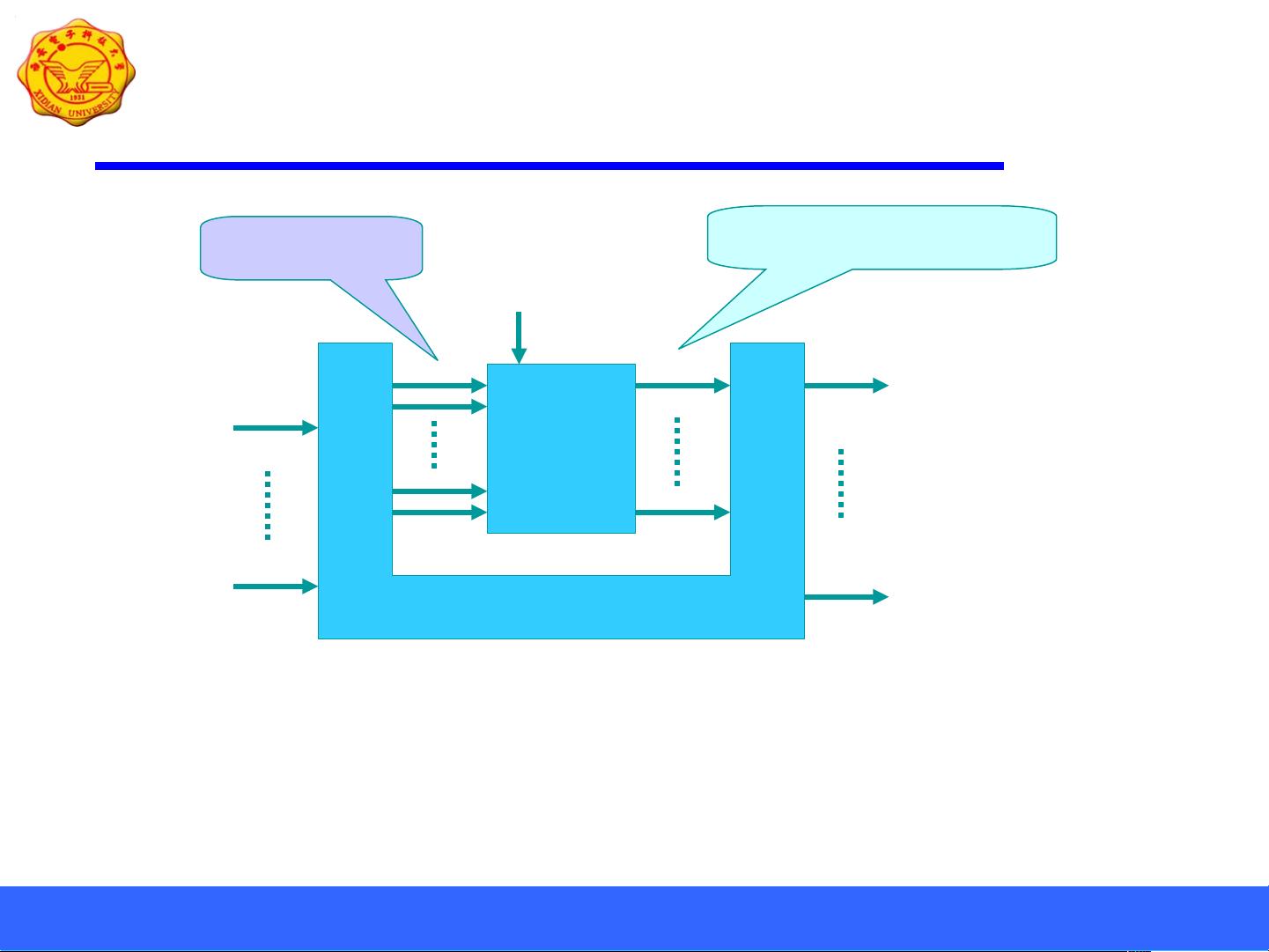

ROM 的存储结构

8.1 半导体存储器

存储容量 = 字 X 位

字 =2

n

n- 地址线数

地

址

译

码

器

存 储 矩 阵

输 出 缓 冲 器

D

m

1-

D

0

W

0

W

1

W

2 £ 1

n

A

0

A

1

A

n

£ 1

三 态 控 制

信 息 单 元

( )字

存 储 单 元

…

…

…

…

…

地

址

输

入

线

数据输出线

( 位 )

存储器容量

=32KX8

地址线数 =15

西安电子科技大学

国家级精品课程数字电路与系统设计

国家级精品课程数字电路与系统设计

地

址

译

码

器

W

0

W

1

W

2

W

3

R R R R

输 出 缓 冲 器

D

3

D

2

D

1

D

0

D

3

D

2

D

1

D

0

三 态 控 制

存 储 矩 阵

A

1

A

0

¡ä ¡ä ¡ä ¡ä

二极管 ROM 的结构图

地址 数据

A

1

A

0

D

3

D

2

D

1

D

0

0

0 1 0 0 1

0

1 0 1 1 1

1

0 1 1 1 0

1

1 0 1 0 1

W

0

W

1

W

2

W

3

ROM 的数据表

西安电子科技大学

国家级精品课程数字电路与系统设计

国家级精品课程数字电路与系统设计

D

3

=W

0

+W

2

D

2

=W

1

+W

2

+W

3

D

1

=W

1

+W

2

D

0

=W

0

+W

1

+W

3

地址 数据

A

1

A

0

D

3

D

2

D

1

D

0

0

0 1 0 0 1

0

1 0 1 1 1

1

0 1 1 1 0

1

1 0 1 0 1

W

0

W

1

W

2

W

3

D

3

= A

1

A

0

+ A

1

A

0

D

2

= A

1

A

0

+ A

1

A

0

+

A

1

A

0

D

1

= A

1

A

0

+ A

1

A

0

D

0

= A

1

A

0

+ A

1

A

0

+

A

1

A

0

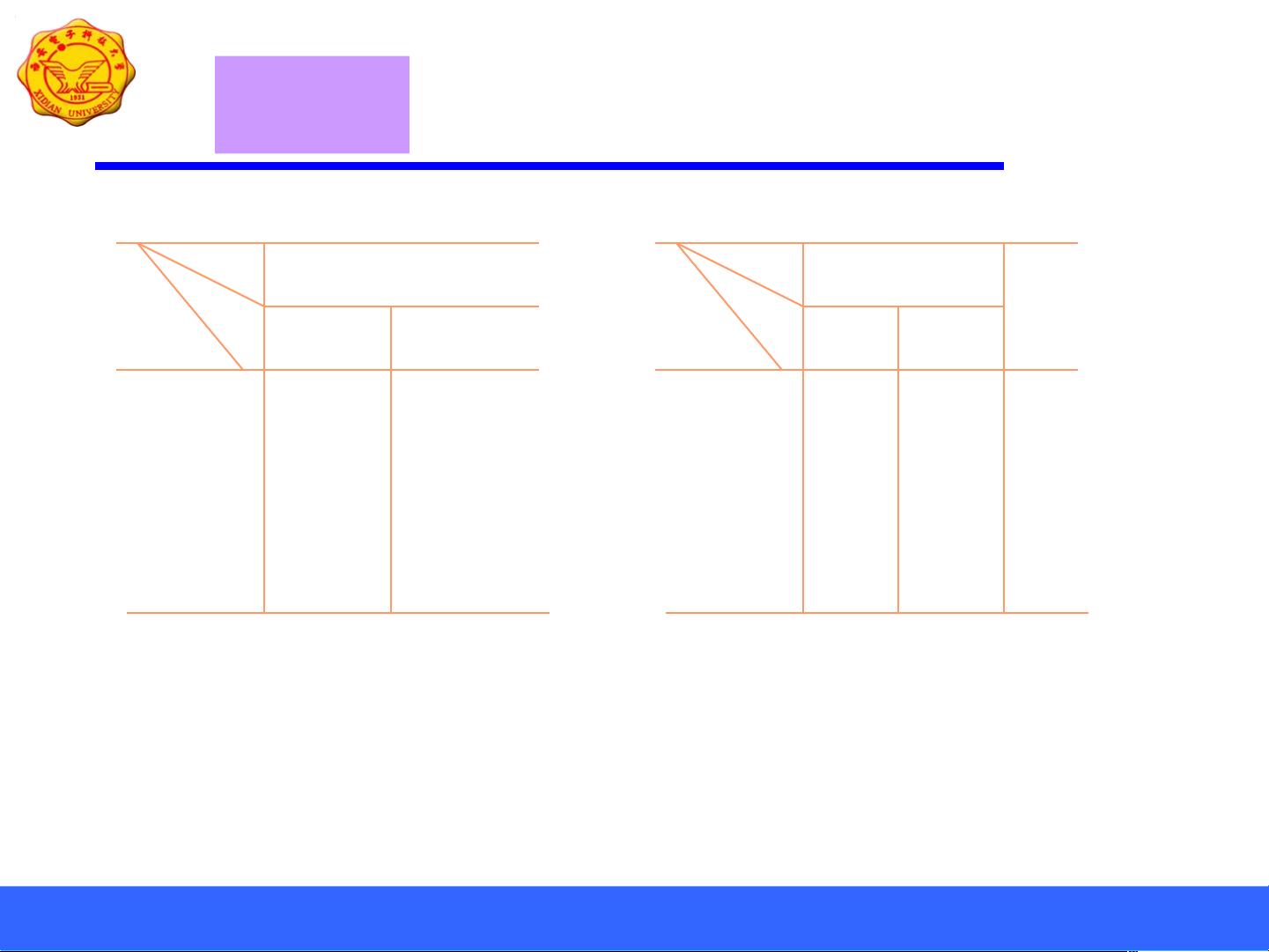

只读存储器( ROM )阵列图

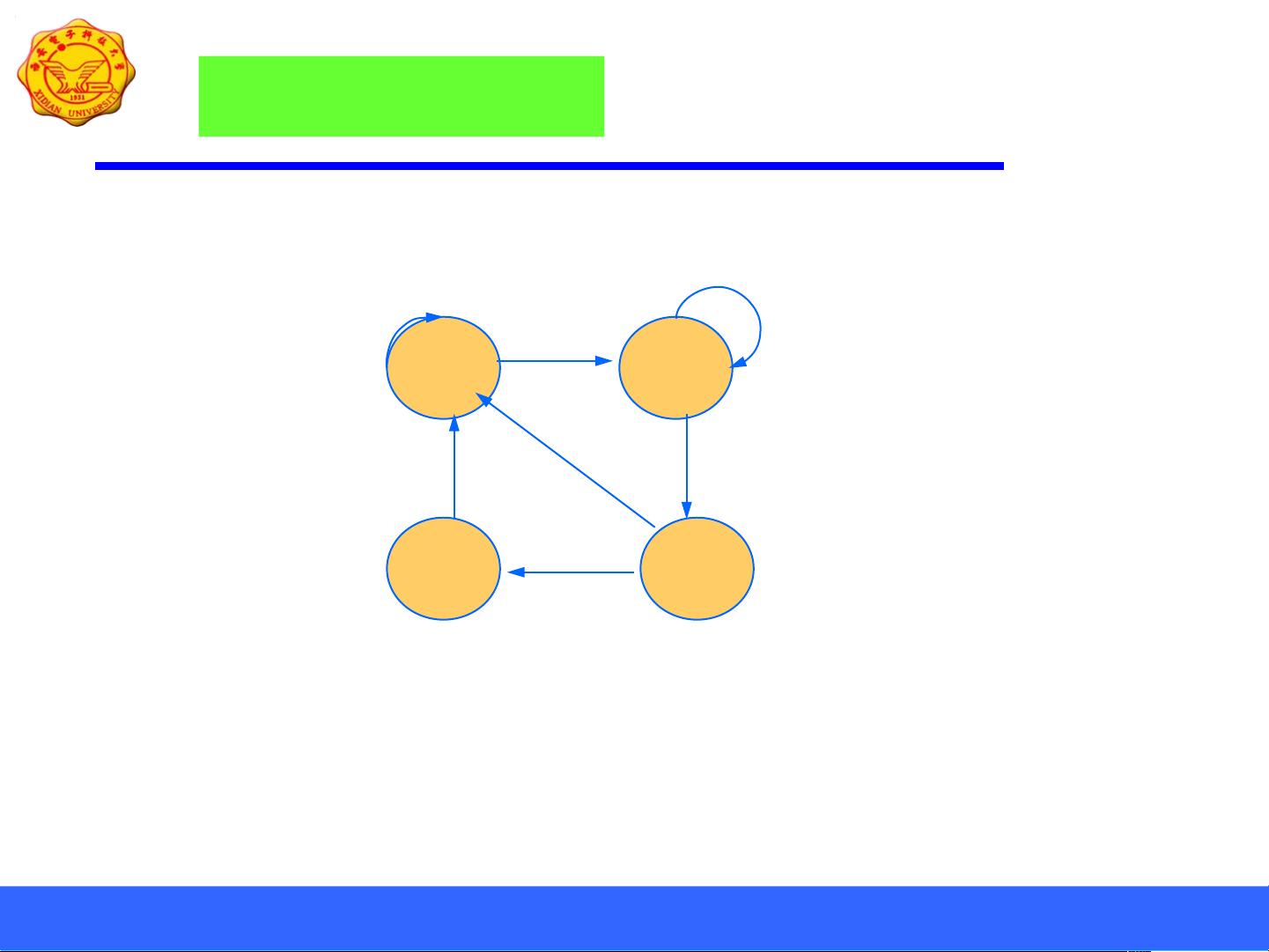

与 阵 列

或 阵 列

W

0

W

1

W

2 £ 1

n

D

m

1-

D

0

…

…

…

A

n

1-

A

0

ROM 的阵列框图

西安电子科技大学

国家级精品课程数字电路与系统设计

国家级精品课程数字电路与系统设计

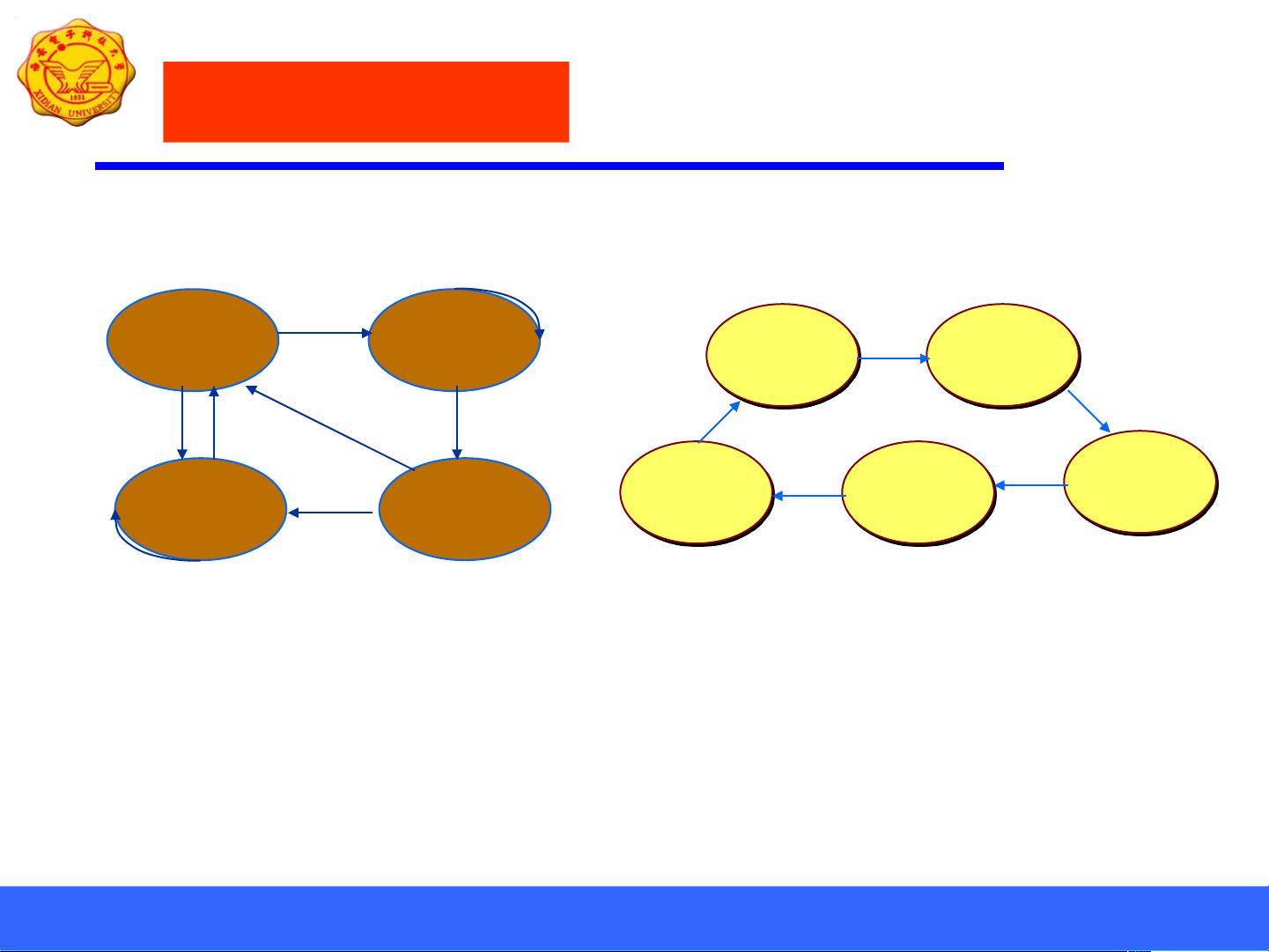

与 阵 列

或 阵 列

W

0

W

1

W

2 £ 1

n

D

m

1-

D

0

…

…

…

A

n

1-

A

0

1

W

0

W

1

W

2

W

3

D

3

D

2

D

1

D

0

A

1

A

0

1

与

阵

列

或

阵

列

ROM 的阵列框图 ROM 的阵列图

只读存储器( ROM )阵列图

D

3

= A

1

A

0

+ A

1

A

0

D

2

= A

1

A

0

+ A

1

A

0

+

A

1

A

0

D

1

= A

1

A

0

+ A

1

A

0

D

0

= A

1

A

0

+ A

1

A

0

+

A

1

A

0

评论0