抢答器数字逻辑课程设计

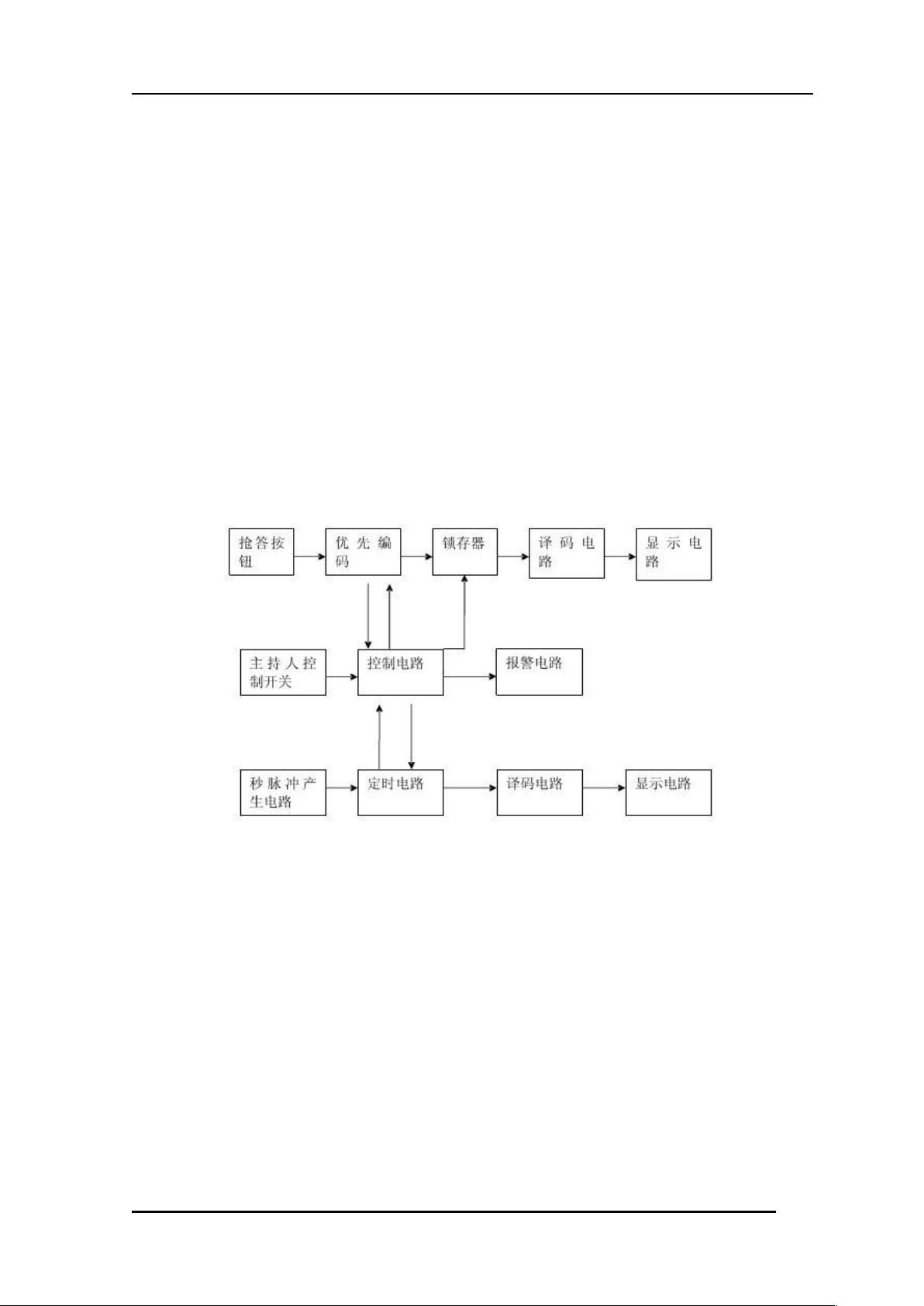

### 抢答器数字逻辑课程设计 #### 一、设计题目及要求 ##### 设计题目:智力竞赛抢答器 ##### 设计任务和要求: 1. **抢答判断与声音标志**:当任意一组参赛者按下抢答按钮,抢答器需能够精确识别并以声音作为标志,指示出抢答者。 2. **互锁功能**:一旦某组成功抢答,抢答器应自动阻止其他组别继续抢答,确保比赛公平。 3. **犯规与警告信号**:若参赛者在主持人宣布“开始”之前按下按钮,即视为犯规,抢答器需自动发出警告信号,并点亮指示灯。 ##### 方案特点: 1. **清零与控制机制**:具备清零功能,由主持人操作,确保在正式开始前无人违规抢答。 2. **定时功能**:设有9秒的抢答时限,若时限内无人抢答,视为所有选手放弃本轮抢答。 3. **报警与禁止抢答**:当9秒倒计时结束仍未有抢答者,系统自动报警,同时禁止任何后续的抢答行为。 #### 二、系统总体方案及硬件设计 ##### 系统总体方案 抢答器的核心在于其控制系统,通过硬件组件实现上述功能。系统包括主机控制器、输入设备(抢答按钮)、输出设备(显示器、扬声器)、以及定时和互锁电路。主机控制器负责接收输入信号,处理逻辑运算,控制输出反馈,同时管理定时和互锁功能。 ##### 硬件设计 **主要元件**:设计中使用的集成电路包括74LS148(优先编码器)、74LS279(双JK触发器/RS锁存器)、74LS48(七段译码驱动器)、74LS192(可逆计数器)、74LS00(四2输入与非门)、74LS121(单稳态多谐振荡器),以及其他辅助电子元器件如电阻、电容、三极管、显示器、开关等。 **主要芯片介绍**: 1. **74LS148**(优先编码器):用于处理多个输入信号中的优先级问题,能够从多个输入中选择最高优先级的信号进行编码,输出对应的二进制编码。在抢答器中,74LS148负责识别哪个抢答按钮被按下,并输出相应的编码,以便系统识别和响应。 - **工作原理**:当输入使能端EI为低电平,且至少有一个输入端有编码请求信号(逻辑0)时,优先编码工作状态标志GS为低电平,表示编码器处于工作状态。编码器会根据输入端的优先级输出对应的二进制编码。当所有输入端为高电平时,输出为全1,此时GS为高电平,表示无编码请求。 - **应用**:在抢答器中,每个抢答按钮连接至74LS148的一个输入端,当某按钮按下时,其对应的输入端为低电平,74LS148识别并输出该按钮的编码,系统根据编码确定抢答者。 **其他关键芯片**: - **74LS279**(双JK触发器/RS锁存器):用于存储抢答状态,一旦某个抢答按钮被按下,74LS279将锁定该状态,防止其他按钮的输入干扰。 - **74LS48**(七段译码驱动器):将二进制编码转换为七段显示码,用于驱动共阴极显示器,显示抢答者的编号。 - **74LS192**(可逆计数器):用于实现定时功能,设定抢答时限,超过时限则自动触发报警。 通过以上硬件设计,抢答器能够实现快速、准确的抢答识别,同时具备互锁、定时、警告等功能,确保比赛的公正性和安全性。 #### 三、智能竞赛抢答器的设计 在智能竞赛抢答器的设计中,重点在于数字逻辑电路的搭建与优化,确保系统的响应速度和稳定性。设计过程中需充分考虑信号传输的延迟、电路布局的合理性以及电源管理的有效性,以保障抢答器在实际比赛中的高效运作。 #### 四、参考文献 在设计智能竞赛抢答器时,参考了众多数字逻辑设计的经典教材和论文,包括但不限于《数字逻辑设计基础》、《现代数字电子技术》等,这些资料提供了丰富的理论知识和实践经验,对设计过程起到了重要的指导作用。此外,也参考了同类抢答器设计的案例分析,学习并吸取了其中的成功经验和失败教训,以期设计出更加完善、实用的智能竞赛抢答器。 智能竞赛抢答器的设计是一门集数字逻辑、电路设计、信号处理等多学科知识于一体的综合性工程。通过精心设计和严格测试,可以打造出既满足比赛需求又具备一定智能化特性的抢答系统,为智力竞赛增添更多的科技元素和公平竞争的氛围。

剩余9页未读,继续阅读

Chouke-Chungyoung2014-06-04这个还算不错,就是截图不好,哎,遗憾了

Chouke-Chungyoung2014-06-04这个还算不错,就是截图不好,哎,遗憾了 天马star2016-03-19还不错,学习到了

天马star2016-03-19还不错,学习到了

- 粉丝: 14

- 资源: 7

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 光储并网VSG系统Matlab simulink仿真模型,附参考文献 系统前级直流部分包括光伏阵列、变器、储能系统和双向dcdc变器,后级交流子系统包括逆变器LC滤波器,交流负载 光储并网VSG系

- file_241223_024438_84523.pdf

- 质子交膜燃料电池PEMFC Matlab simulink滑模控制模型,过氧比控制,温度控制,阴,阳极气压控制

- IMG20241223015444.jpg

- 模块化多电平变器(MMC),本模型为三相MMC整流器 控制策略:双闭环控制、桥臂电压均衡控制、模块电压均衡控制、环流抑制控制策略、载波移相调制,可供参考学习使用,默认发2020b版本及以上

- Delphi 12 控件之FlashAV FFMPEG VCL Player For Delphi v7.0 for D10-D11 Full Source.7z

- Delphi 12 控件之DevExpressVCLProducts-24.2.3.exe.zip

- Mysql配置文件优化内容 my.cnf

- 中国地级市CO2排放数据(2000-2023年).zip

- smart200光栅报警程序

信息提交成功

信息提交成功