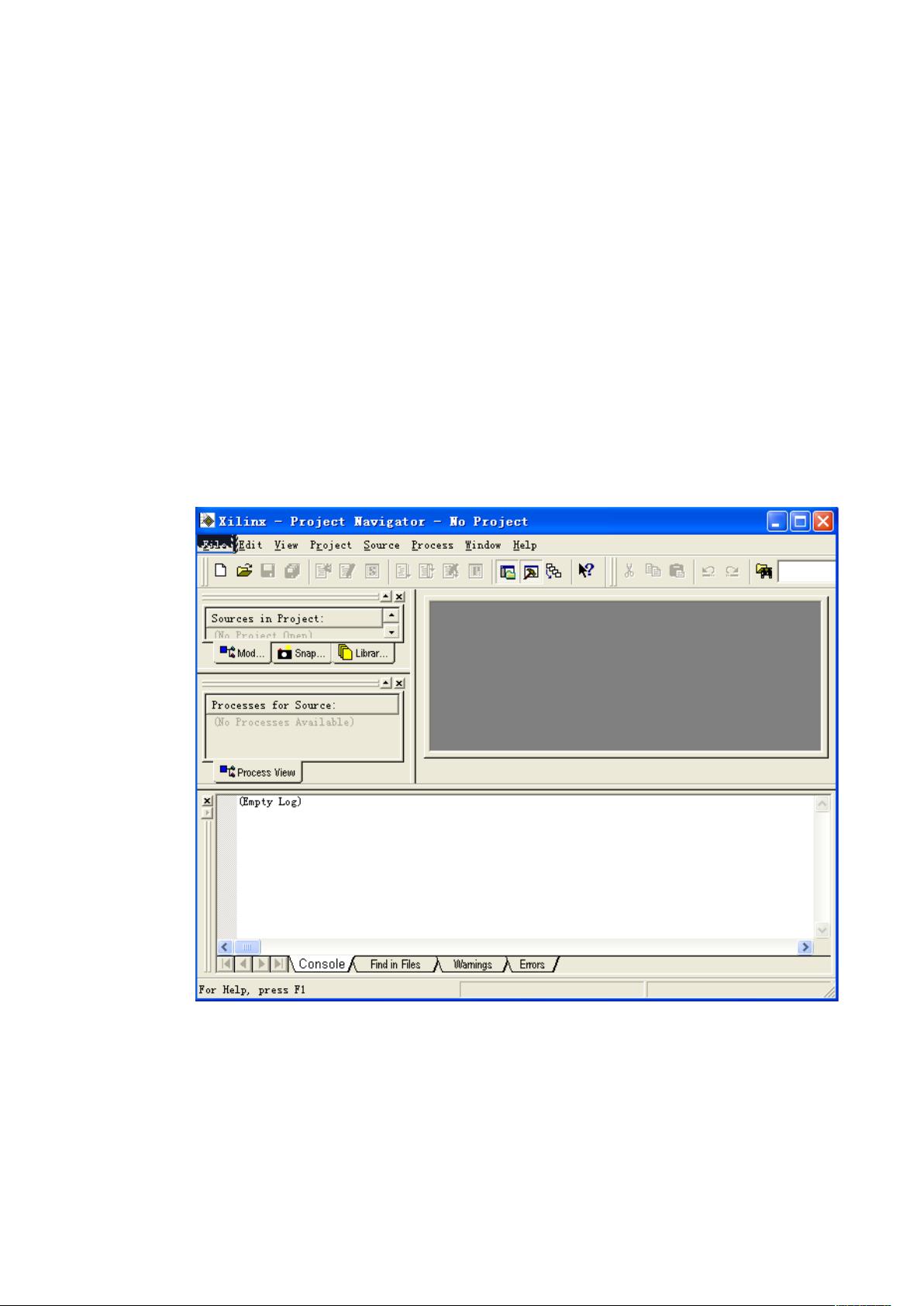

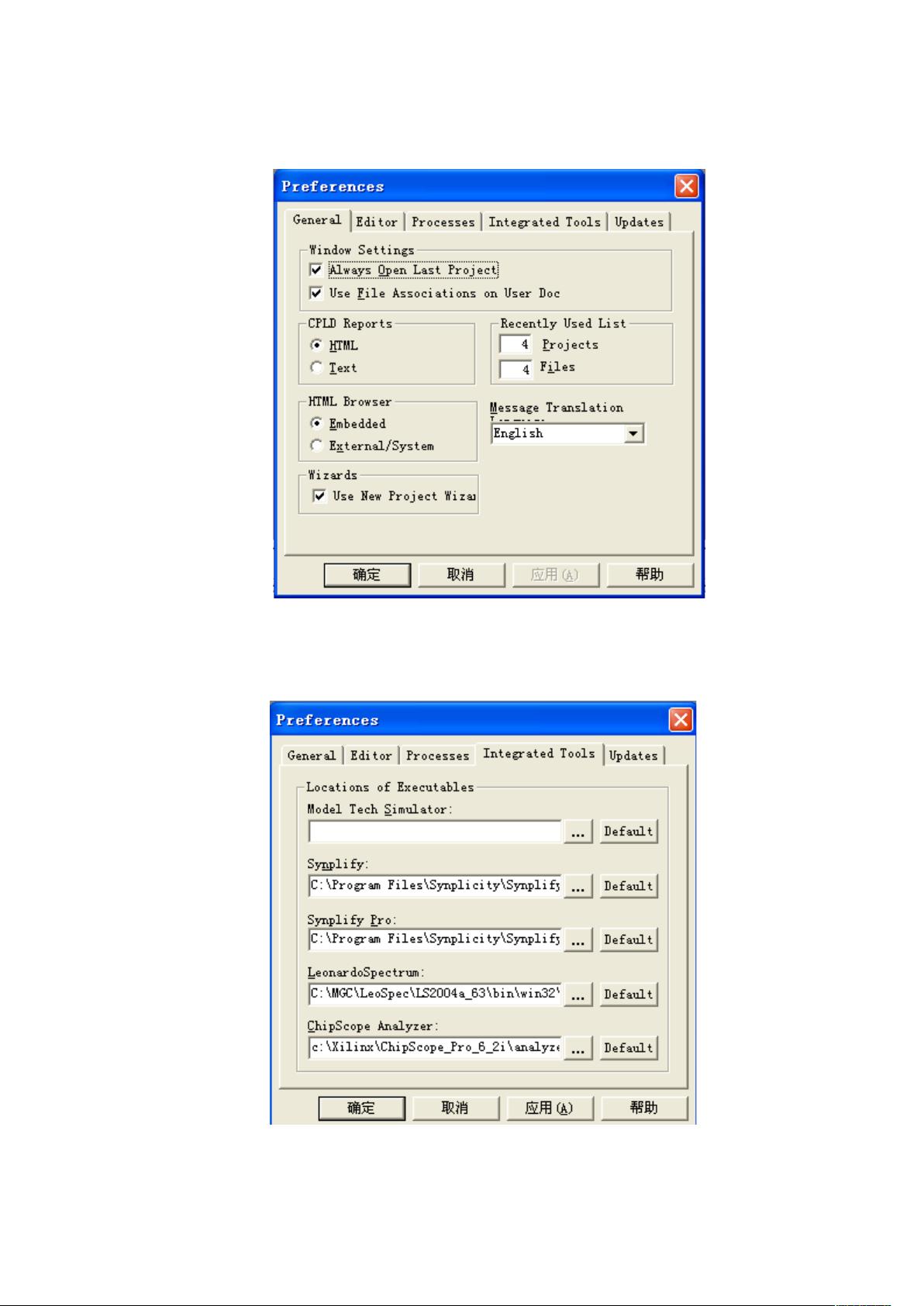

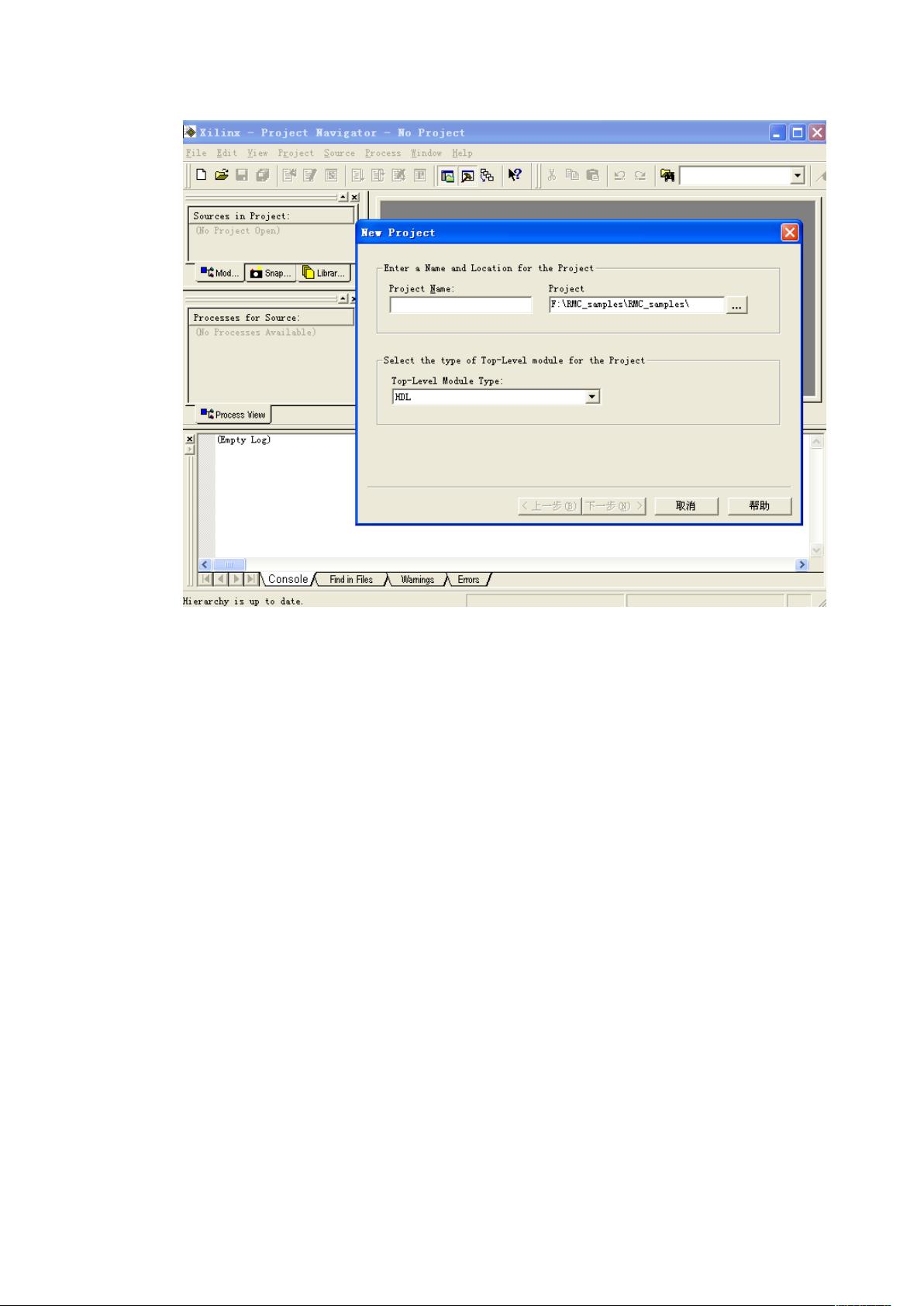

【Foundation ISE使用方法】 Foundation ISE是一款由Xilinx公司提供的FPGA(Field-Programmable Gate Array)集成开发环境,用于设计、实现和验证基于Xilinx FPGA的数字逻辑电路。该工具支持硬件描述语言(HDL),如VHDL和Verilog,允许工程师们在门级和行为级进行设计。 在使用Foundation ISE时,首先需要确保安装了兼容的版本,例如ISE6.2以上。同时,为了获得更高效的设计流程,可以选择第三方的综合工具,如Synplify pro 7.7.1或LEONARDO_2004AUP2。如果这些工具未安装,可以使用ISE自带的XST工具进行综合。仿真则推荐使用ModelSim SE 5.7以上的版本。 安装完毕后,可以通过桌面快捷方式或“开始”菜单启动Xilinx6 -> Project Navigator -> ISE,进入如图1所示的开始界面。接着,需要对第三方软件进行配置,如ModelSim的路径设定。这可以在主菜单的"EDIT" -> "Preferences"中完成,如图2所示。在"Integrated tools"中指定ModelSim的安装路径,如图3和4所示。设置完成后,重启ISE以使设置生效。 建立工程是设计流程的第一步,通过"File" -> "New Project"来创建新项目,如图5所示。在项目命名后,选择相应的Xilinx产品系列、器件型号、封装和速度等级,这将影响FPGA的性能,如图6所示。综合工具可根据已有软件选择,如未安装第三方工具,可以使用默认的XST。 设计文件的添加有两种方式:一是增加已存在的源文件,二是新建源文件。对于已存在的文件,只需在项目树中选中目标器件,右键点击并选择"Add Source",然后找到对应的文件,如图8和9所示。新建源文件时,选择VHDL或Verilog作为设计语言,并指定模块名称,如图11所示,最后完成创建,如图13所示。 在源文件中编写代码后,可以进行仿真验证。ModelSim在ISE中支持两种仿真方式:语言激励(Test Bench)和波形激励。对于熟悉语言的用户,推荐使用语言写激励,如图15所示,选择相应语言的Test Bench和Text Fixture。对于新手,可选择波形输入,右键选中模块,添加Test Bench Waveform,如图16所示。在建立的波形图上(图17)调整信号高低电平,保存波形,然后运行"Simulate Behavioral Model"开始行为仿真,如图18所示。 此外,约束文件(.ucf)的生成是必不可少的步骤,用于定义引脚分配、时钟速度和其他电气特性。在项目中添加新的限制文件(选择UCF图标),指定顶层源文件,如图19所示。约束文件的编辑能确保设计在实际硬件上的正确实现。 Foundation ISE提供了一个全面的FPGA设计平台,从设计输入、综合、仿真到硬件配置,涵盖了整个设计流程。理解并熟练使用它的各项功能,能够有效地提升设计效率和质量。

剩余21页未读,继续阅读

- 粉丝: 1

- 资源: 10

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 专业毕业实习指导书.docx

- 专业见习实施方案.docx

- 专题调研登记表.docx

- 最新紧固件标准型号对照表.docx

- docker-images-bak.zip

- haaaaaaaaaaaaaaaaaaaa

- VIENNA维也纳拓扑,三相整流simulink仿真:采用电压电流双闭环控制,电压外环采用PI控制,电流内环采用bang bang滞环控制 整流电压稳定在600V 有相关参考资料

- 改进的双锁相环阻抗重塑控制策略 复现一篇IEEE上英文文献 创新点:阻抗重塑 双锁相环 另有一份中文版报告(与模型完全对应) 采用改进的双锁相环阻抗重塑控制策略,不仅能保留较快的动态响应,还能极大地提

- Python入门学习-基本程序结构

- “三好”学生登记表.doc

- 部门包干经费报销单.doc

- 毕业生顶岗(就业)实习考核鉴定表.doc

- Scum内各种快捷键的使用与说明.xlsx

- 创新实践学分申报汇总表.docx

- 村级集体经济调研登记表.docx

- 大学生科研创新基金项目申请书.doc

信息提交成功

信息提交成功