没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

Xilinx PCIe 核的官方文档.The LogiCORE™ IP Endpoint Block Plus for PCI Express® core is a high-bandwidth, scalable, and reliable serial interconnect building block for use with Virtex®-5 LXT/SXT/FXT/TXT FPGA devices. The Endpoint Block Plus for PCI Express (PCIe®) solution supports 1-lane, 2-lane, 4-lane, and 8-lane configurations, all of which are protocol-compliant and electrically compatible with the PCI Express Base Specification v1.1.

资源推荐

资源详情

资源评论

DS551 April 19, 2010 www.xilinx.com 1

Product Specification

© 2006–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and

other countries. All other trademarks are the property of their respective owners. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG.

The LogiCORE™ IP Endpoint Block Plus for PCI

Express

® core is a high-bandwidth, scalable, and reli-

able serial interconnect building block for use with

Virtex®-5 LXT/SXT/FXT/TXT FPGA devices. The

Endpoint Block Plus for PCI Express

(PCIe®) solution

supports 1-lane, 2-lane, 4-lane, and 8-lane configura-

tions, all of which are protocol-compliant and electri-

cally compatible with the PCI Express Base Specification

v1.1.

PCI Express offers a serial architecture that alleviates

many of the limitations of parallel bus architectures by

using clock data recovery (CDR) and differential signal-

ing. Using CDR (as opposed to source synchronous

clocking) lowers pin count, enables superior frequency

scalability, and makes data synchronization easier. The

layered architecture of PCI Express provides for future

attachment to copper, optical, or emerging physical sig-

naling media. PCI Express technology, adopted by the

PCI-SIG as the next generation PCI, is backward-com-

patible to the existing PCI software model.

With higher bandwidth per pin, low overhead, low

latency, reduced signal integrity issues, and CDR architec-

ture, the Endpoint Block Plus for PCIe sets the industry

standard for a high-performance, cost-efficient third-gen-

eration I/O solution.

The Endpoint Block Plus solutions are compatible with

industry-standard application form factors such as the

PCI Express Card Electromechanical (CEM) v1.1 and the

PCI Industrial Computer Manufacturers Group (PICMG)

3.4 specifications.

The Endpoint Block Plus for PCIe

solutions are defined

in the following table.

LogiCORE IP Endpoint Block

Plus v1.14 for PCI Express®

DS551 April 19, 2010 Product Specification

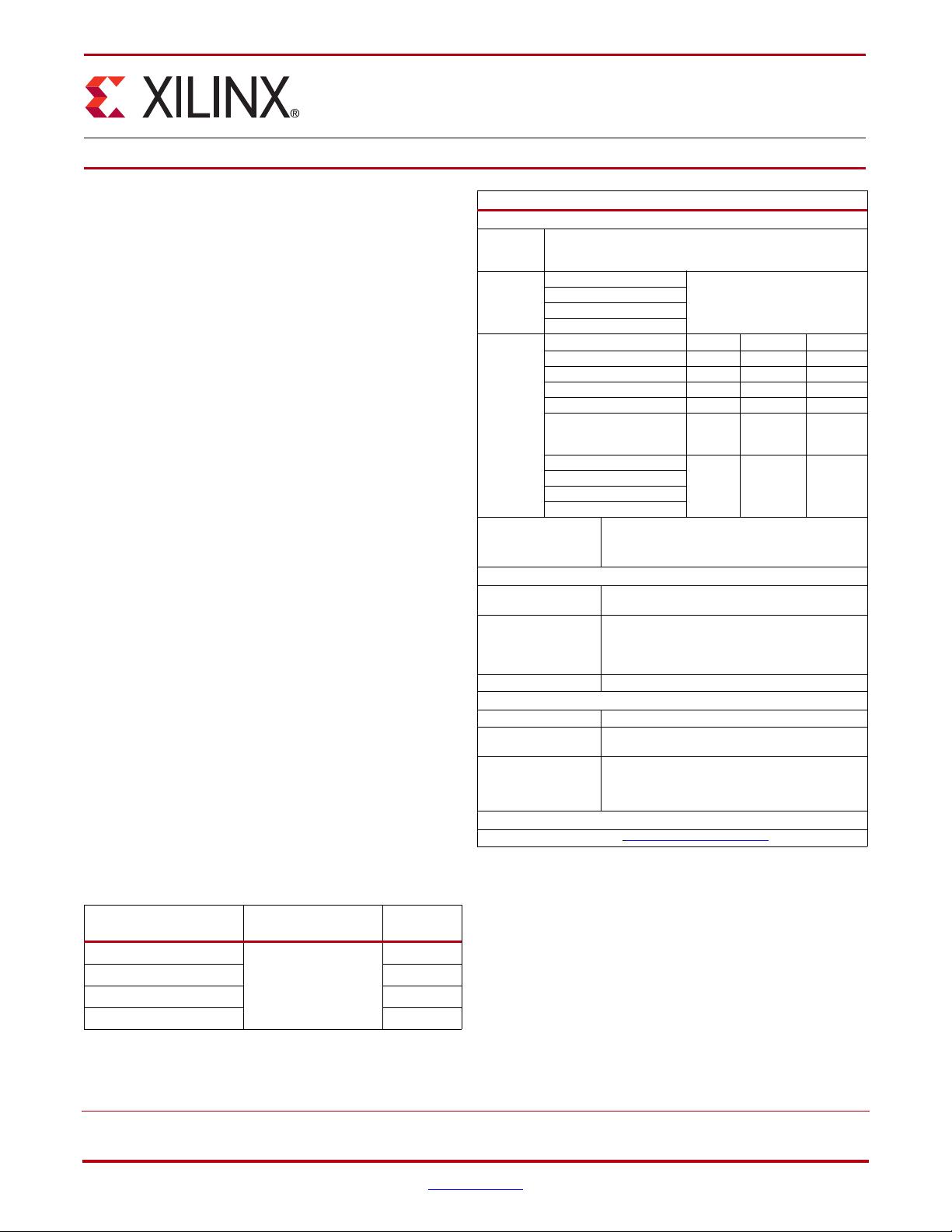

Product FPGA Support

Data Path

Width

1-lane Endpoint Block Plus

Virtex-5 FPGA

LXT/SXT/FXT/TXT

64

2-lane Endpoint Block Plus 64

4-lane Endpoint Block Plus 64

8-lane Endpoint Block Plus 64

LogiCORE IP Facts

Core Specifics

Supported

FPGA

Families

(1)

1. For the complete list of supported devices, see the 12.1 release notes for

this core.

Virtex-5 LXT/SXT/FXT/TXT

(2)

2. Virtex-5 FPGA solutions require the latest production silicon stepping and

are pending hardware validation; the LogiCOR

E IP w

arranty does not in-

clude production usage with engineering sample silicon (ES).

Minimum

Device

Req.

1-lane Endpoint Block Plus

XC5VLX20T-1

(3)

XC5VSX35T-1

XC5VFX30T-1

XC5VTX150T-1

3. XC5VLX20T does not support 8-lane product.

2-lane Endpoint Block Plus

4-lane Endpoint Block Plus

8-lane Endpoint Block Plus

Resources

Used

Product I/O

(4)

4. GTP or GTX transceivers.

LUT

(5)

5. Numbers are for the default core configuration; actual LUT and FF utiliza-

tion values vary based on specific configurations.

FF

4

1-lane Endpoint Block Plus 1

(6)

6. In Virtex-5 devices, 1-lane Endpoint core uses 1 GTP/GTX tile (2 GTP or

GTX transceivers).

2125 2625

2-lane Endpoint Block Plus 2 2150 2675

4-lane Endpoint Block Plus 4 2175 2750

8-lane Endpoint Block Plus 8 2250 2925

Block

RAM

CMPS

(7)

#

Tx

Buffers

7. Capability Maximum Payload Size (CMPS).

CMPS

1-lane Endpoint Block Plus

614

(8)

8. Supports 14 TLPs at CMPS (512 bytes payload):

- 8 Non-posted, 3 Posted, 3 Completion.

- Supports 22 TLPs at 256 bytes payload: 8 Non-posted, 7 Posted,

7 Completion.

- Supports 24 TLPs at 128 bytes payload or less: 8 Non-posted,

8 Posted, 8 Completion.

512

2-lane Endpoint Block Plus

4-lane Endpoint Block Plus

8-lane Endpoint Block Plus

Special Features

GTP and GTX Transceivers

Virtex-5 Integrated Block for PCI Express

Phased Lock Loop, Block RAM

Provided with Core

Documentation

Product Specification, Getting Started Guide,

User Guide, Instantiation Template

Design Files

Verilog® and VHDL Simulation Models

Verilog Source Files

Verilog and VHDL Test Bench

Verilog and VHDL Example Design

Constraints File User Constraints File (UCF)

Design Tool Support

HDL Synthesis Tool XST, Synopsys® Synplify® Pro D-2009.12

Xilinx Implementation

To o l s

Xilinx ISE® v12.1

Simulation Tools

(9)

9. Requires a Verilog LRM-IEEE 1364-2005 encryption-compliant simulator.

For VHDL simulation, a mixed HDL license is required.

Cadence® Incisive Enterprise Simulator (IES) v9.2 and

above

Synopsys® VCS and VCS MX 2009.12 and above

Mentor Graphics® ModelSim® v6.5c and above

Support

Provided by Xilinx, Inc. @ www.xilinx.com/support

LogiCORE IP Endpoint Block Plus v1.14 for PCI Express®

2 www.xilinx.com DS551 April 19, 2010

Product Specification

Features

• High-performance, highly flexible, scalable, and reliable, general purpose I/O core

♦ Compliant with the PCI Express Base Specification v1.1

♦ Compatible with conventional PCI software model

• Incorporates Xilinx Smart-IP™ technology to guarantee critical timing

• Uses GTP transceivers for Virtex-5 LXT and SXT devices and GTX transceivers for Virtex-5 FXT

and TXT devices

♦ 2.5 Gbps line speed

♦ Supports 1-lane, 2-lane, 4-lane, and 8-lane operation

♦ Elastic buffers and clock compensation

♦ Automatic clock data recovery

• 8b/10b encode and decode

• Supports Lane Reversal and Lane Polarity Inversion per PCI Express specification requirements

• Standardized user interface

♦ Easy-to-use packet-based protocol

♦ Full-duplex communication

♦ Back-to-back transactions enable greater link bandwidth utilization

♦ Supports flow control of data and discontinuation of an in-process transaction in transmit

direction

♦ Supports flow control of data in receive direction

• Supports removal of corrupted packets for error detection and recovery

• Compliant with PCI/PCI Express power management functions

• Supports a maximum transaction payload of up to 512 bytes

• Supports Multi-Vector MSI for up to 32 vectors

• Bandwidth scalability with interconnect width

• Fully compliant with PCI Express transaction ordering rules

Applications

The Endpoint Block Plus for PCI Express architecture enables a broad range of computing and commu-

nications target applications, emphasizing performance, cost, scalability, feature extensibility and mis-

sion-critical reliability. Typical applications include

• Data communications networks

• Telecommunications networks

• Broadband wired and wireless applications

• Cross-connects

• Network interface cards

• Chip-to-chip and backplane interconnect

• Crossbar switches

• Wireless base stations

DS551 April 19, 2010 www.xilinx.com 3

Product Specification

LogiCORE IP Endpoint Block Plus v1.14 for PCI Express®

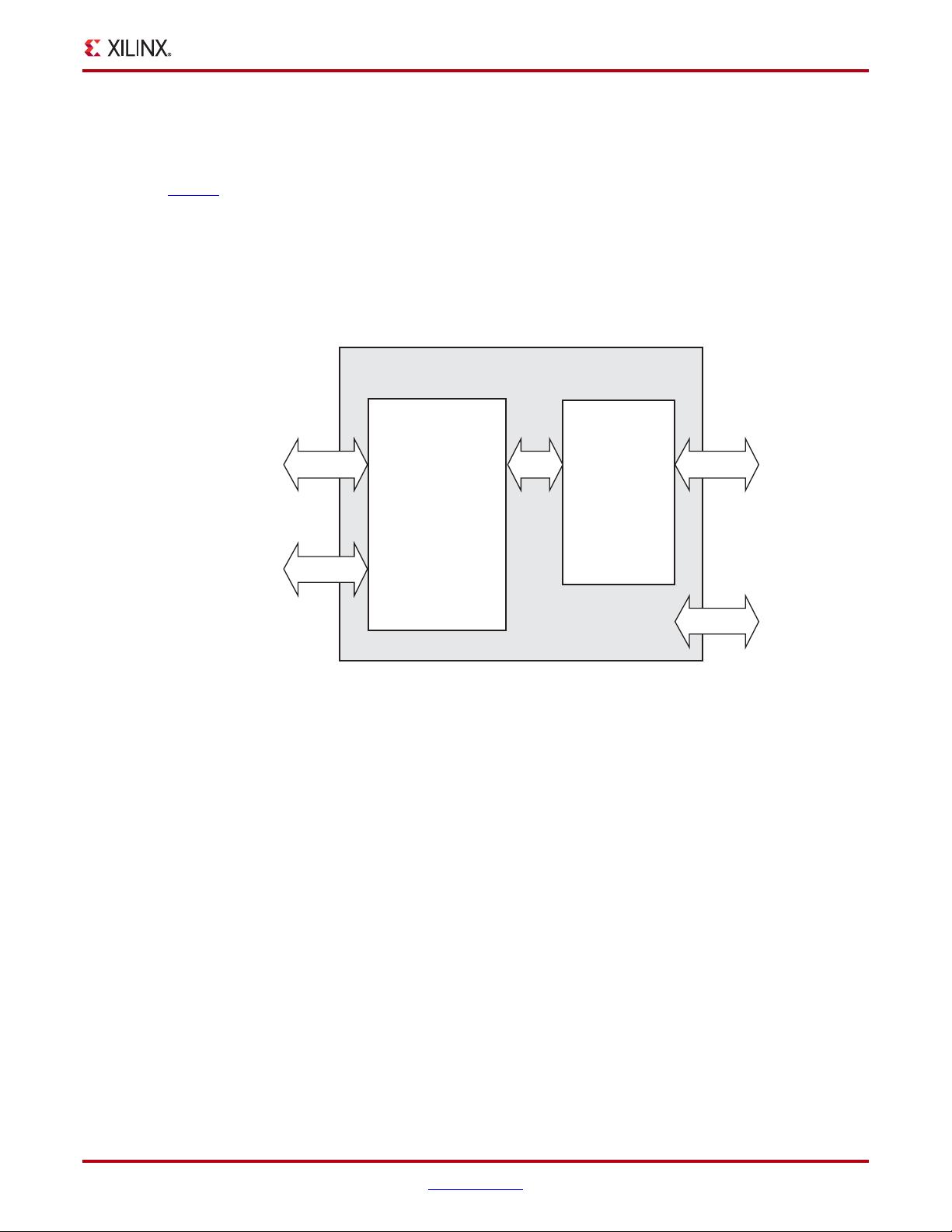

Functional Description

The Endpoint Block Plus for PCIe internally instances the Virtex-5 FPGA Integrated Block for PCI

Express. For information about the internal architecture of the Virtex-5 FPGA Endpoint block, see

UG 197

, Virtex-5 FPGA Integrated Endpoint Block for PCI Express Designs User Guide. Figure 1 illustrates

the interfaces to the core.

• System (SYS) interface

• PCI Express (PCI EXP) interface

• Configuration (CFG) interface

• Transaction (TRN) interface

Protocol Layers

The Endpoint Block Plus for PCIe follows the PCI Express Base Specification layering model, which con-

sists of the Physical, Data Link, and Transaction Layers. The protocol uses packets to exchange infor-

mation between layers. Packets are formed in the Transaction and Data Link Layers to carry

information from the transmitting component to the receiving component. Necessary information is

added to the packet being transmitted, which is required to handle the packet at specific layers.

At the receiving end, each layer of the receiving element processes the incoming packet, strips the rel-

evant information and forwards the packet to the next layer. As a result, the received packets are trans-

formed from their Physical Layer representation to their Data Link Layer representation and

Transaction Layer representation.

The functions of the protocol layers include:

• Generating and processing of TLPs

• Flow-control management

• Initialization and power management functions

• Data protection

• Error checking and retry functions

• Physical link interface initialization

X-Ref Target - Figure 1

Figure 1: Endpoint Block Plus for PCI Express Top-level Functional Blocks and Interfaces

Virtex-5

Integrated Block

for PCI Express

RocketIO

Transceivers

Endpoint Block Plus for PCI Express

PCI Express

(PCI_EXP)

System

(SYS)

Transaction

(TRN)

Config uration

(CFG)

PCI

Express

Fabric

User

Logic

Host

Interface

Clock

and

Reset

剩余17页未读,继续阅读

资源评论

zqingshun

- 粉丝: 1

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功