基于JTAG的边界扫描技术

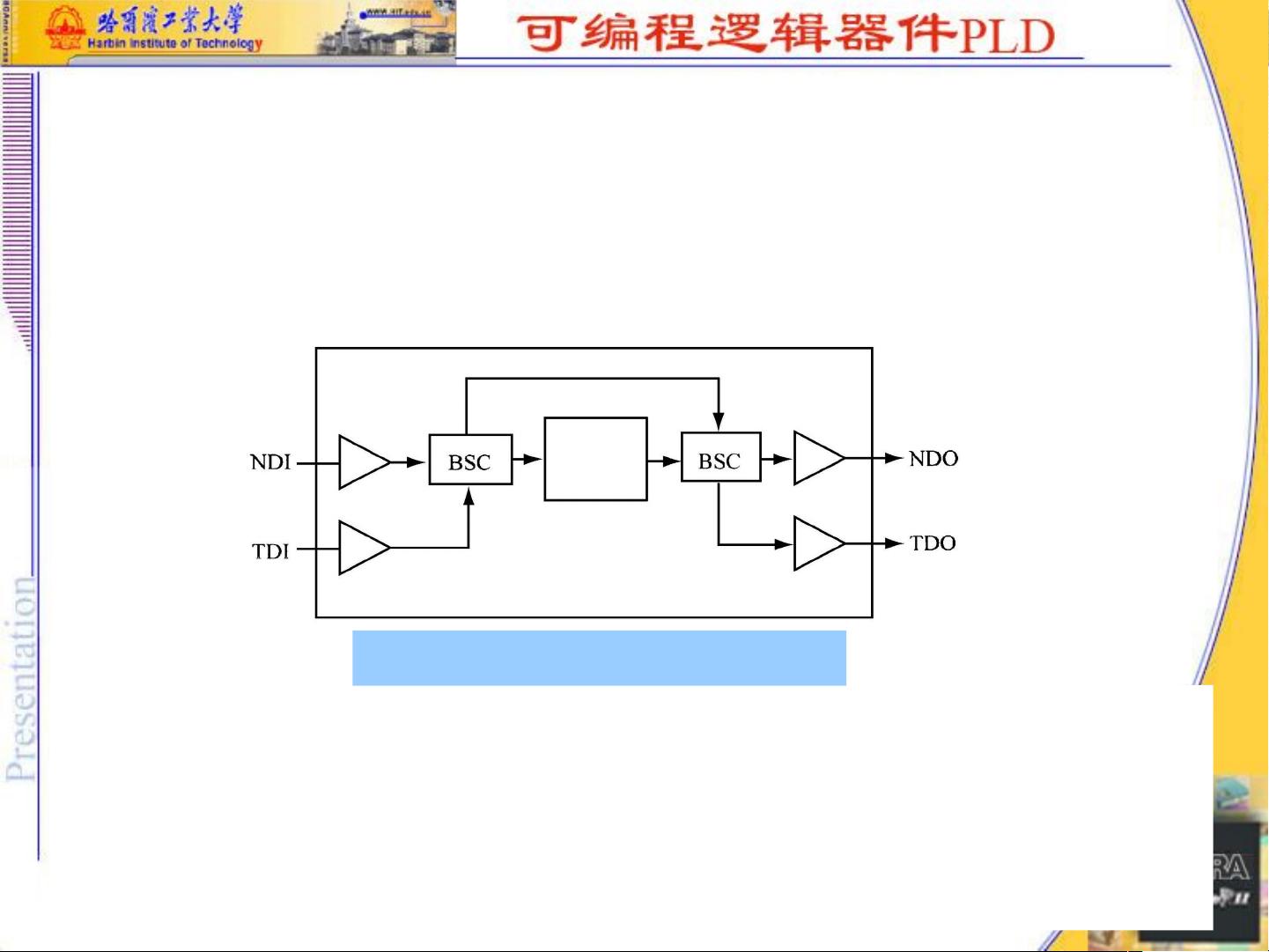

"基于JTAG的边界扫描技术" 基于JTAG的边界扫描技术是一种新兴的测试技术,旨在解决印制电路板测试的难题。随着微电子技术、微封装技术和印制板制造技术的不断发展,印制电路板变得越来越小、密度越来越大、复杂程度越来越高,传统的“探针”方法已不能满足要求。 边界扫描测试(Boundary Scan Testing,简写BST)技术是Joint Test Action Group(JTAG)于20世纪80年代提出的,后来在1990年被批准为IEEE标准1149.1-1990。该标准提供了有效地测试引线间隔致密的电路板上元器件的能力。 边界扫描测试技术有两个主要优点:一是方便芯片的故障定位,能迅速准确地测试两个芯片管脚的连接是否可靠,提高测试检验效率;二是具有JTAG接口的芯片,内置一些预先定义好的功能模式,通过边界扫描通道来使芯片处于某个特定的功能模式,以提高系统控制的灵活性,方便系统设计。 边界扫描技术是一种应用于数字集成电路器件的测试性结构设计方法。所谓“边界”是指测试电路被设置在IC器件逻辑功能电路的四周,位于靠近器件输入、输出引脚的边界处。所谓“扫描”是指连接器件各输入、输出引脚的测试电路实际上是一组串行移位寄存器,这种串行移位寄存器被叫做“扫描路径”,沿着这条路径可输入由“0”和“1”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确。 边界扫描单元(Boundary Scan Cell,简写BSC)是边界扫描测试的核心组件。每个BSC有两个数据通道:测试数据通道和正常数据通道。边界扫描单元BSC的连接图核心逻辑能够迫使逻辑追踪引脚信号,也能从引脚或器件核心逻辑信号中捕获数据。 边界扫描测试技术的核心思想是在芯片管脚和芯片内部逻辑之间,即紧挨元件的每个输入、输出引脚处增加移位寄存器组,在测试模式下,寄存器单元在相应的指令作用下,控制输出引脚的状态,读入输入引脚的状态,从而允许用户对PCB上的互连进行测试。 边界扫描测试技术的电路结构主要包括指令寄存器、数据寄存器和测试访问端口(TAP)控制器。测试访问端口(TAP)是边界扫描测试的控制中心,它控制着边界扫描寄存器的工作状态。TAP控制器由指令寄存器、数据寄存器和测试模式选择信号组成。 JTAG测试接口是一种标准化的测试接口,通常由五个信号引脚组成:TDI、TDO、TMS、TCK和TRST。这些信号引脚的名称和含义如下: * TDI:测试数据输入,指令和测试编程数据的串行输入引脚。 * TDO:测试数据输出,指令和测试编程数据的串行输出引脚。 * TMS:测试模式选择,该输入引脚是一个控制信号,它决定TAP控制器的转换。 * TCK:测试时钟输入,时钟输入到BST电路,一些操作发生在上升沿,而另一些发生在下降沿。 * TRST:测试复位输入,低电平有效,用于初始化或复位BST电路。 基于JTAG的边界扫描技术是一种高效、可靠的测试技术,广泛应用于数字集成电路器件的测试和检测。

剩余19页未读,继续阅读

- 粉丝: 6

- 资源: 23

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功