没有合适的资源?快使用搜索试试~ 我知道了~

AR0130寄存器表

温馨提示

试读

60页

AR0130寄存器表,列出了AR0130所有的寄存器

资源推荐

资源详情

资源评论

AR0130: Register Reference

Aptina reserves the right to change products or specifications without notice.

AR0130 Registers - Rev. C Pub. 2/14 EN

1 ©2011 Aptina Imaging Corporation. All rights reserved.

Aptina Confidential and Proprietary

AR0130 Registers, Rev. C

For more information, refer to the data sheet on Aptina's Web site: www.aptina.com

AR0130 Register Reference

Aptina reserves the right to change products or specifications without notice.

AR0130 Registers - Rev. C Pub. 2/14 EN

2 ©2011 Aptina Imaging Corporation. All rights reserved.

AR0130: Register Reference

Introduction

Aptina Confidential and Proprietary

Introduction

This register reference is provided for engineers who are designing cameras that use the

AR0130.

Register Address Space

The AR0130 provide a 16-bit register address space accessed through a serial interface.

Each register location is 8 or 16 bits in size.

The address space is divided into the five major regions shown in Table 1.

Register Notation

The underlying mechanism for reading and writing registers provides byte write capa-

bility. However, it is convenient to consider some registers as multiple adjacent bytes.

The AR0130 use 8-bit, 16-bit, and 32-bit registers, all implemented as 1 or more bytes at

naturally aligned, contiguous locations in the address space.

In this document, registers are described either by address or by name. When registers

are described by address, the size of the registers is explicit. For example, R0x3024 is an

8-bit register at address 0x3024, and R0x3000

–1 is a 16-bit register at address 0x3000–

0x3001. When registers are described by name, the size of the register is implicit. It is

necessary to refer to the register table to determine that model_id is a 16-bit register.

Register Aliases

A consequence of the internal architecture of the AR0130 is that some registers are

decoded at multiple addresses. Some registers in “configuration space” are also decoded

in “manufacturer-specific space.” To provide unique names for all registers, the name of

the register within manufacturer-specific register space has a trailing underscore. For

example, R0x0000

–1 is model_id, and R0x3000–1 is model_id_. The effect of reading or

writing a register through any of its aliases is identical.

Bit Fields

Some registers provide control of several different pieces of related functionality, and

this makes it necessary to refer to bit fields within registers. As an example of the nota-

tion used for this, the least significant 4 bits of the model_id register are referred to as

model_id[3:0] or R0x0000

–1[3:0].

Table 1: Address Space Regions

Address Range Description

0x0000–0x0FFF Reserved

0x1000–0x1FFF Reserved

0x2000–0x2FFF Reserved

0x3000–0x3FFF Manufacturer-specific registers (read-only and read-write dynamic registers)

0x4000–0xFFFF Reserved

Aptina reserves the right to change products or specifications without notice.

AR0130 Registers - Rev. C Pub. 2/14 EN

3 ©2011 Aptina Imaging Corporation. All rights reserved.

AR0130: Register Reference

Register Notation

Aptina Confidential and Proprietary

Byte Ordering

Registers that occupy more than 1 byte of address space are shown with the lowest

address in the highest-order byte lane to match the byte-ordering on the bus. For

example, the model_id register is R0x0000

–1. In the register table the default value is

shown as 0x2402. This means that a READ from address 0x0000 would return 0x26, and a

READ from address 0x0001 would return 0x00. When reading this register as two 8-bit

transfers on the serial interface, the 0x26 will appear on the serial interface first, followed

by the 0x00.

Address Alignment

All register addresses are aligned naturally. Registers that occupy two bytes of address

space are aligned to even 16-bit addresses, and registers that occupy four bytes of

address space are aligned to 16-bit addresses that are an integer multiple of 4.

Bit Representation

For clarity, 32-bit hex numbers are shown with an underscore between the upper and

lower 16 bits. For example: 0x3000_01AB.

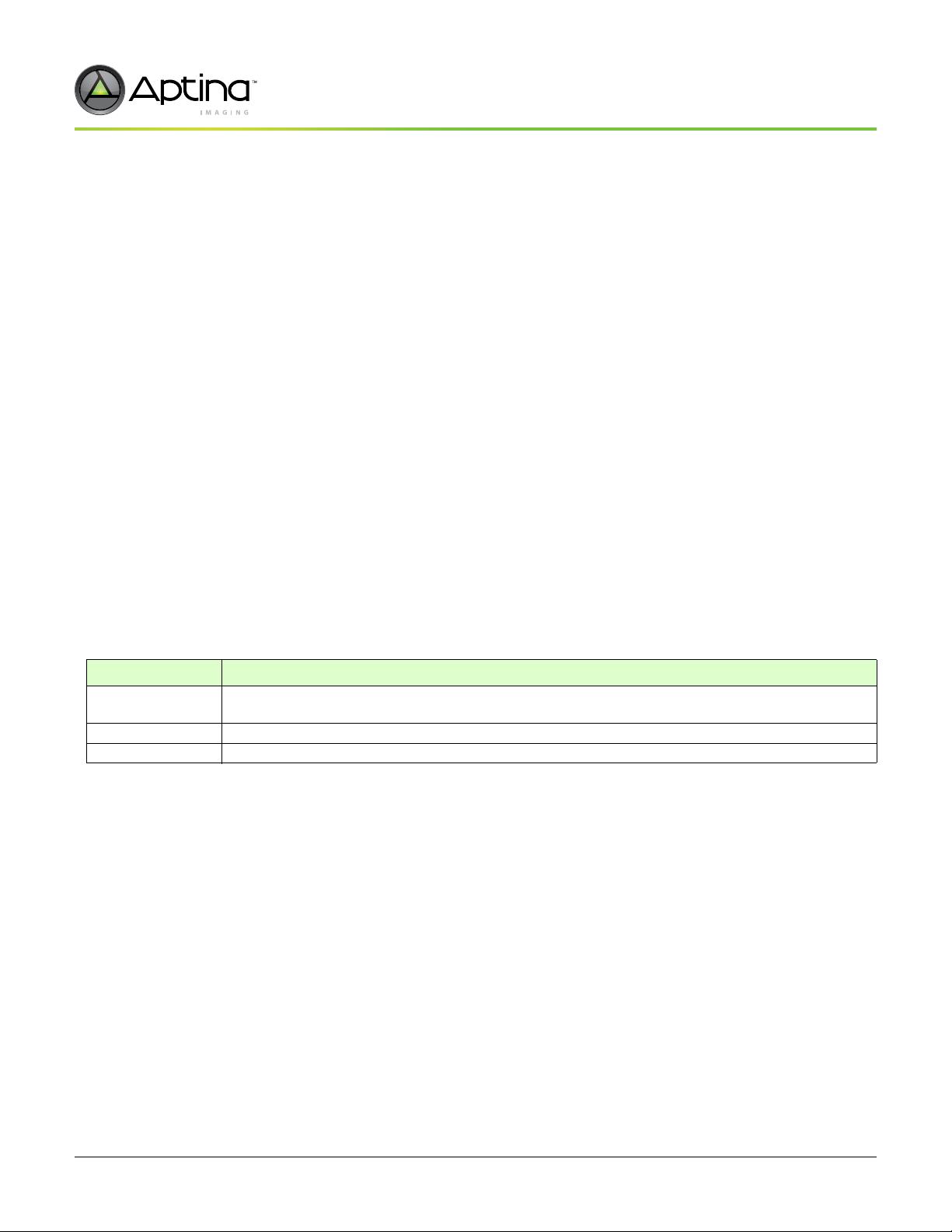

Data Format

Most registers represent an unsigned binary value or set of bit fields. For all other register

formats, the format is stated explicitly at the start of the register description. The nota-

tion for these formats is shown in Table 2.

Table 2: Data Formats

Name Description

FIX16 Signed fixed-point, 16-bit number: two’s complement number, 8 fractional bits.

Examples: 0x0100 = 1.0, 0x8000 = –128, 0xFFFF = –0.0039065

UFIX16 Unsigned fixed-point, 16-bit number: 8.8 format. Examples: 0x0100 = 1.0, 0x280 = 2.5

FLP32 Signed floating-point, 32-bit number: IEEE 754 format. Example: 0x4280_0000 = 64.0

Aptina reserves the right to change products or specifications without notice.

AR0130 Registers - Rev. C Pub. 2/14 EN

4 ©2011 Aptina Imaging Corporation. All rights reserved.

AR0130: Register Reference

Register Behavior

Aptina Confidential and Proprietary

Register Behavior

Registers vary from “read-only,” “read/write,” and “read, write-1-to-clear.”

Double-Buffered Registers

Some sensor settings cannot be changed during frame readout. For example, changing

x_addr_start partway through frame readout would result in inconsistent row lengths

within a frame. To avoid this, the AR0130 double-buffer many registers by implementing

a “pending” and a “live” version. READs and WRITEs access the pending register; the live

register controls the sensor operation.

The value in the pending register is transferred to a live register at a fixed point in the

frame timing, called frame start. Frame start is defined as the point at which the first

dark row is read out internally to the sensor. In the register tables the “Sync’d” column

shows which registers or register fields are double-buffered in this way.

Bad Frames

A bad frame is a frame where all rows do not have the same integration time or where

offsets to the pixel values have changed during the frame.

Many changes to the sensor register settings can cause a bad frame. For example, when

line_length_pck is changed, the new register value does not affect sensor behavior until

the next frame start. However, the frame that would be read out at that frame start will

have been integrated using the old row width, so reading it out using the new row width

would result in a frame with an incorrect integration time.

By default, bad frames are not masked. If the masked bad frame option is enabled, both

LV and FV are inhibited for these frames so that the vertical blanking time between

frames is extended by the frame time.

In the register tables, the “Bad Frame” column shows where changing a register or

register field will cause a bad frame. This notation is used:

N—No. Changing the register value will not produce a bad frame.

Y—Yes. Changing the register value might produce a bad frame.

YM—Yes; but the bad frame will be masked out when mask_corrupted_frames

(R0x0105) is set to “1.”

Aptina reserves the right to change products or specifications without notice.

AR0130 Registers - Rev. C Pub. 2/14 EN

5 ©2011 Aptina Imaging Corporation. All rights reserved.

AR0130: Register Reference

TAble of Contents

Aptina Confidential and Proprietary

TAble of Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Register Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Register Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Register Aliases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Bit Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Byte Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Address Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Bit Representation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Data Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Register Behavior. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Double-Buffered Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Bad Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Register Summary Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Manufacturer-Specific Register List and Default Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Manufacturer-Specific Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

剩余59页未读,继续阅读

资源评论

newmsg_sdr2019-11-05资料可以,就是太贵了,C版本的,我刚刚上传了D版本的,更新,只要5个积分。

newmsg_sdr2019-11-05资料可以,就是太贵了,C版本的,我刚刚上传了D版本的,更新,只要5个积分。

Mihawk666

- 粉丝: 0

- 资源: 11

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功