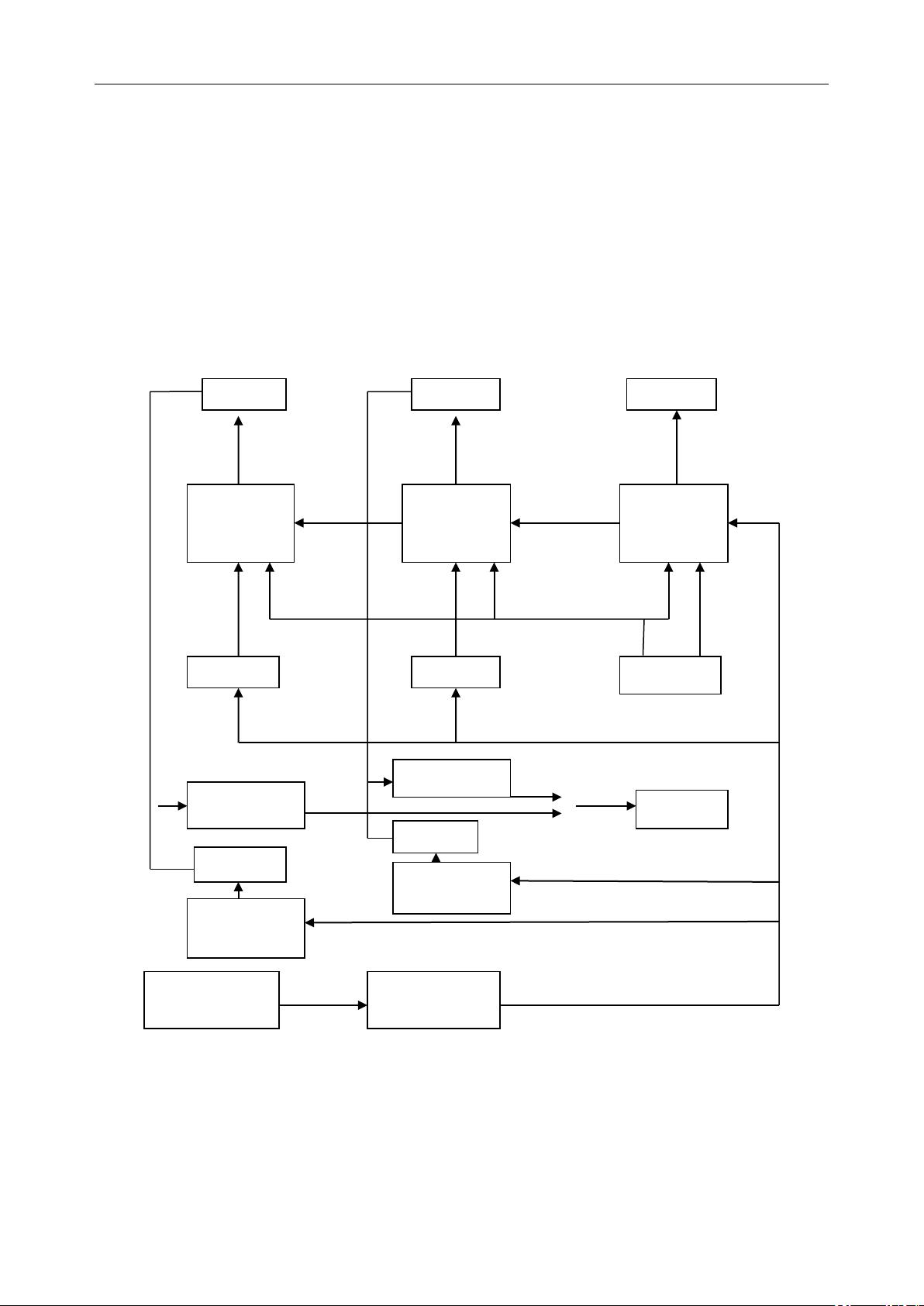

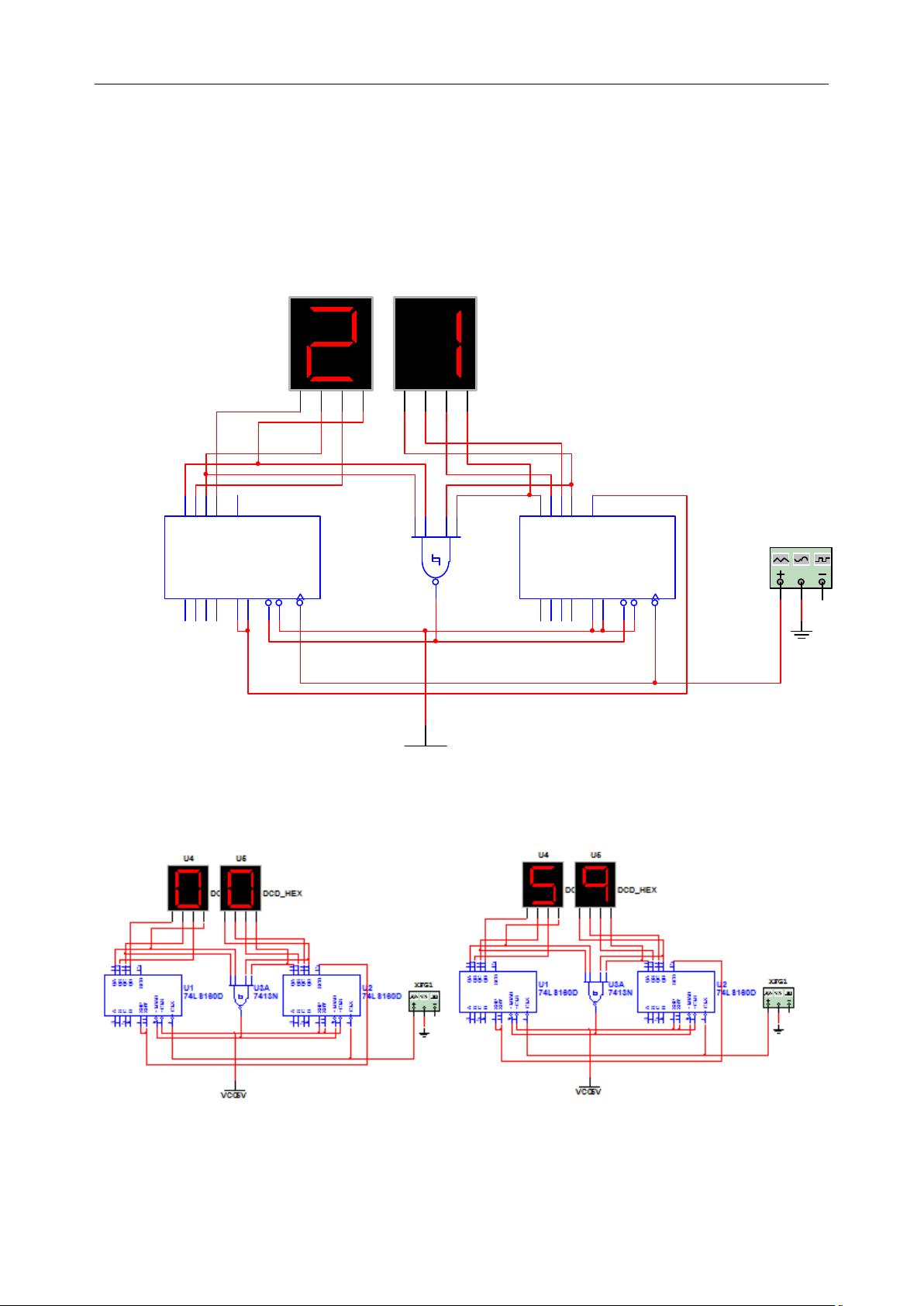

数字电子技术课程设计报告.doc 数字电子钟是一种用数字显示秒﹑分﹑时的记时装置,与传统的机械时钟相比,它一般具有走时准确﹑显示直观﹑无机械传动装置等优点,因而得到了广泛的应用:小到人们的日常生活中的电子手表、电子闹钟,大到车站﹑码头﹑机场等公共场所的大型数字显电子钟。 本课程设计是要通过简单的逻辑芯片实现数字电子钟。要点在于用555芯片连接输出为一秒的多谐振荡器用于时钟的秒脉冲,用74LS160(10进制计数器)、74LS00(与非门芯片)等连接成60和24进制的计数器,再通过数码管显示,构成简单数字时钟。 关键词 数字时钟、计数器、555芯片、分频器 《数字电子技术课程设计报告——基于555芯片的数字电子钟实现》 数字电子钟是现代生活中的常见设备,其精准的计时、直观的显示以及无机械传动的特性使其在众多领域得到广泛应用。本课程设计的目标是利用基本的逻辑芯片构建一个简单的数字时钟,其中核心部分包括555定时器、计数器和分频器。设计的关键在于通过555芯片构造一个多谐振荡器,输出稳定的1KHz时钟脉冲,然后通过74LS160这样的十进制计数器和74LS00与非门芯片组合,形成60进制和24进制的计数器,最终通过数码管进行时间的显示。 技术要求中,设计的数字时钟需具备24小时制的时、分、秒显示,并能进行校时,确保准确性。555定时器作为多谐振荡器,其产生的1KHz脉冲经过千分频器(由三级74LS90组成)降频至1Hz,以满足计时需求。此外,设计还要求有闹钟功能,增强实用性。 系统结构上,数字时钟分为时、分、秒计数器,校时电路以及显示电路。计数器部分,秒和分计数器由两个60进制的同步递增计数器(74LS160)组成,小时计数器则是一个24进制的同步递增计数器。这些计数器通过异步级联方式相互连接,确保时间的连续累加。显示器部分,采用数码管显示,提供清晰的时间读取。 60进制计数器由两片74LS160和74LS13与非门组成,其工作原理是通过计数器的逐位翻转实现0到59的循环计数。而24进制计数器则是通过两片74LS160和74LS10与非门,实现0到23的循环计数。这两个计数器的组合,实现了数字时钟的完整功能。 555定时器作为多谐振荡器,其输出的1KHz脉冲是整个系统的心脏。通过调整电阻和电容值,可以精确控制振荡器的输出频率,以满足设计需求。在实际操作中,可能需要微调电阻值以获取更接近1KHz的频率。 总结来说,这个数字电子技术课程设计项目旨在通过基础的数字逻辑组件实现一个功能完备的数字时钟。学生将深入理解555定时器的工作原理,掌握计数器的构建方法,以及如何通过分频器调控时钟信号。此外,通过实际操作,学生还将学习到数字电路设计、电路调试和系统集成的重要技能。这个项目不仅巩固了理论知识,也锻炼了实践能力,是数字电子技术学习过程中的一个重要实践环节。

剩余10页未读,继续阅读

- 粉丝: 195

- 资源: 3404

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

- 1

- 2

前往页