Scalable and Modularized

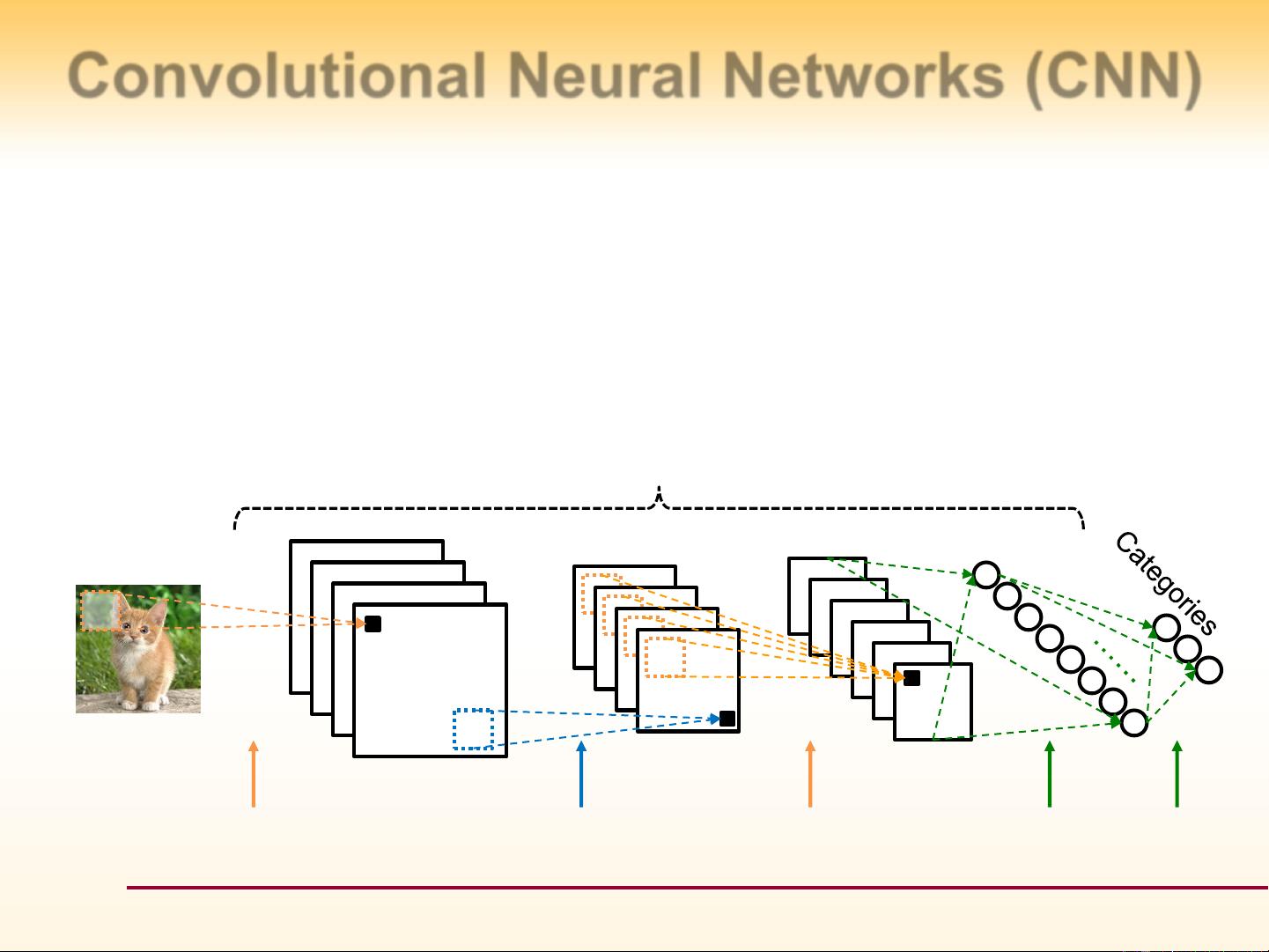

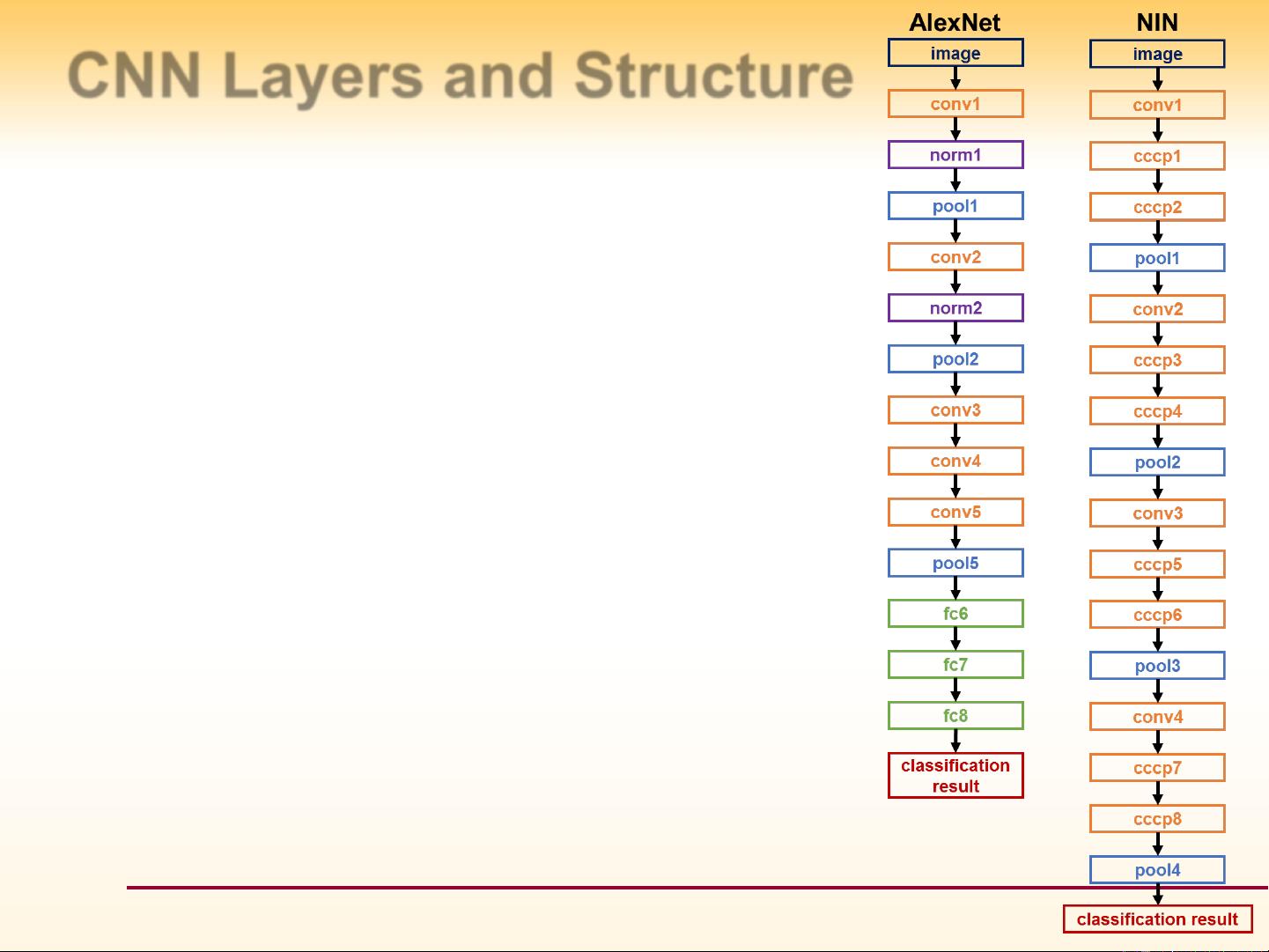

深度学习FPGA设计与实现是近年来人工智能加速硬件领域的一个热点研究方向,由于深度学习模型的复杂性和计算密集性,传统的CPU已经无法满足其对计算性能和能效的要求。因此,如何将深度学习模型,特别是卷积神经网络(CNN)高效地映射到专用集成电路(ASIC)和现场可编程门阵列(FPGA)等硬件加速器上,成为了研究的重点。 文章标题“Scalable and Modularized”强调了FPGA加速器设计的两个核心原则:可扩展性(Scalability)和模块化(Modularity)。这意味着设计者需要构建能够适应不同规模深度学习模型,并且可以通过组合不同的模块快速实现硬件设计的FPGA加速器。 在描述中提到的“深度学习FPGA设计与实现”,我们可以理解为文章将主要讨论如何将深度学习算法中的CNN映射到FPGA硬件上的细节问题。CNN是目前识别和检测任务中的主导方法,其迭代性高,并且主要由几种类型的层组成,包括卷积层(Convolution)、激活层(Activation)、池化层(Pooling)以及全连接层(Fully-connected)。随着深度学习技术的发展,CNN的层数从最初的几个增加到现在的超过100层,每层的计算复杂度也不断上升。 CNN的层和结构对硬件设计提出了更高的要求。卷积层包含了绝大多数的操作(>90%),是深度学习加速中的重点。池化层(Pooling)和局部响应归一化层(LRN)虽然操作相对简单,但是对保持特征的不变性至关重要。全连接层需要大量的权重矩阵乘法,对存储和带宽的要求非常高。 文章还提到了当前的CNN加速器的比较,包括基于软件的GPU加速器,如Caffe和TensorFlow,以及基于高层次综合(HLS)和硬件描述语言(RTL)的FPGA加速器。GPU加速器虽然提供了高度模块化的灵活深度学习框架,并且利用GPU上的成千上万个并行核心实现了加速,但其缺点是功耗高(>100W)。HLS加速器的优势在于设计迭代时间短和设计优化快,但其无法充分利用低层次的硬件结构。而基于RTL设计的通用CNN加速器虽然对CNN模型配置具有灵活性,但在硬件资源使用上并不高效。 作者Yufei Ma等人提出了一种模块化的CNN RTL编译器,目的是在FPGA上实现高度可扩展和模块化的CNN加速器。通过设计一个能够支持多层次并高效利用FPGA资源的编译器,可以在不同的CNN模型之间实现更好的资源复用和硬件加速。文章的实验结果将展示该编译器在实现不同CNN模型时的性能和资源利用率,以及与现有技术的比较。 模块化设计的好处在于,它允许开发者通过组合不同的计算模块来适配不同的CNN架构,从而实现快速设计、优化以及更新。这种设计方法可以大幅降低设计复杂度和提高设计效率,进而缩短产品从设计到市场的周期。 整体而言,文章将探讨深度学习算法特别是CNN算法的实现原理,分析当前CNN硬件加速器的优缺点,并详细介绍一种新的模块化CNN RTL编译器的设计理念和实验结果。这对于希望深入了解如何将深度学习算法高效部署到FPGA平台的研究者和工程师来说具有重要的参考价值。

剩余35页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- samtec IP68 接插件数据手册

- 使用 Fluent 在 2D 中模拟单个 气泡在水中上升 包括流畅的案例文件

- C#ASP.NET网盘管理源码数据库 Access源码类型 WebForm

- 深入解析 C++ std::thread 的.detach () 方法:原理、应用与陷阱

- Vue 条件渲染之道:v-if 与 v-else 的深度应用与最佳实践

- PHP网址导航书签系统源码带文字搭建教程数据库 MySQL源码类型 WebForm

- C++ 线程安全日志系统:设计、实现与优化全解析

- OpenGL使用OpenGL基于Instancing实现粒子系统

- 使用 ansys Fluent 进行径向弯曲散热器热分析

- 构建可复用 Vue 组件的实战指南与深度解析

信息提交成功

信息提交成功