一种用 VHDL 语言设计的数字密码锁

A Digital Password 2Lock Designed by VHDL

刘 钰

3

张有志

LIU Yu AHANG You2zhi

摘 要 为了进一步减少现有数字密码锁系统的规模 ,提高其性能的灵活性 ,本文利用 EDA 技术 ,用 VHDL 语言 ,

在 MAX+ PLUS Ⅱ环境下 ,设计了一种新型的数字密码锁 ,它体积小、功耗低、价格便宜、安全可靠 ,维护和

升级都十分方便 ,具有较好的应用前景。

关键词 数字密码锁 FPGA VHDL MAX+ PLUS Ⅱ

Abstract To further reduce the size of present digital password2lock and improve the flexibility of the perfor2

mance , a new2type digital password 2 lock is designed with EDA technology and VHDL language. This new digital pass2

word2lock has better application prospect , because of small volume , low power , low price , securityand easy maintenance

and upgrade.

Keywords Digital password2lock FPGA VHDL MAX+ PLUS Ⅱ

3 山东大学信息科学与工程学院 济南 250100

随着电子技术的发展 ,具有防盗报警等功能的电子密码

锁代替密码量少 、安全性差的机械式密码锁已是必然趋势。

目前大部分密码锁采用单片机进行设计 ,电路比较复杂 ,性

能不够灵活

[122 ]

。本文采用先进的 EDA 技术 ,利用 MAX +

PLUXⅡ工作平台和 VHDL 语言

[324 ]

,设计了一种新型的密码

锁。该密码锁具有密码预置和误码报警等功能 ,用一片 FP2

GA 芯片实现。由于充分利用了 FPGA 芯片密度大、功耗低、

可重复编程和具有嵌入式阵列块的结构特点 ,因而该数字密

码锁体积小、功耗低、价格便宜、安全可靠 ,维护和升级都十

分方便。

1 数字密码锁的设计要求

该密码锁的密码由五位十进制数字组成 , 初始设定

“00000”。可由用户任意设置密码 ;密码输入正确时开锁 ;连

续三次输入错误密码时系统报警。

2 数字密码锁的总体结构

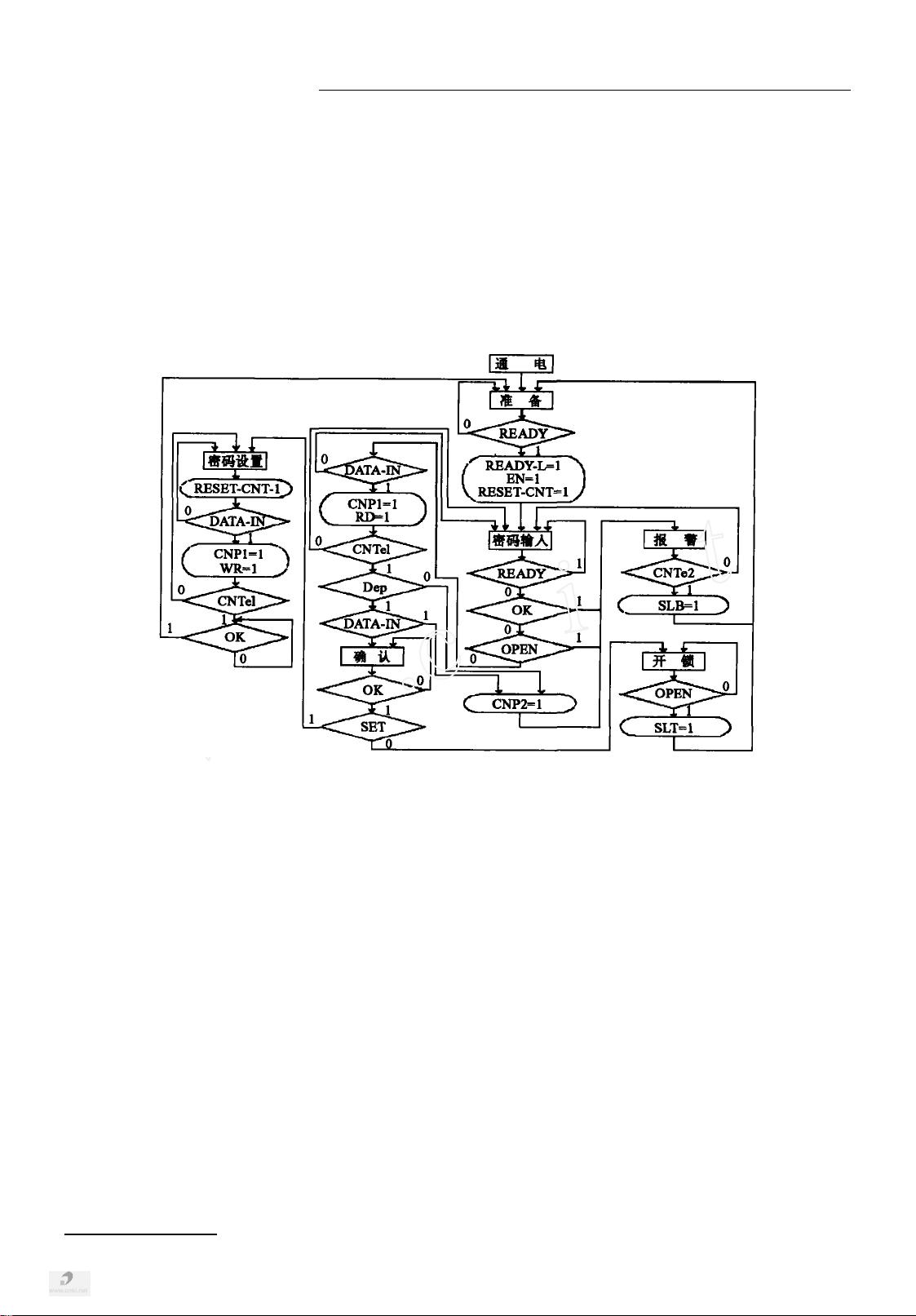

数字密码锁的系统结构框图由图 1 所示。

控制器模块是整个系统的控制核心 ,负责接收其它模块

传来的输入信号 ,再根据系统的功能产生相应的控制信号送

到相关的模块。

消抖同步电路用来消去开关电平抖动现象并提供同步

信号 ;编码器接收消抖同步电路传来的数字密码信号后编码

输出给比较器和 RAM ,并提供一个数字输入信号 ;比较器用

来接收编码器和双口 RAM 送来的数字密码并进行比较 ,结

果送入移位寄存器 ;移位寄存器采用串入并出的方式 ,将比

较器的输出结果送给控制器和计数器 2 ;分频器用来提供系

统使用的两路时钟信号 ;计数器 1 给 RAM 提供地址信号并

产生比较位数的控制信号 ;计数器 2 对输入错误次数累积 ,

达到规定次数时输出报警信号 ;双口 RAM 用来存储设置的

密码。

图 1 数字密码锁的系统结构框图

开锁时 , 先 按“READY”键 , 输 入 密 码 , 再 按“OK”和

“OPEN”键 ;设置密码时 ,先按“SET”键 ,键入要设置的密码 ,

再按“OK”键确定 ;若输入密码正确 ,锁打开 ,若锁不能打开 ,

说明输入密码有误 ,可按“READY”键重新输入密码 。

3 数字密码锁的控制器的设计

由图 1 可以看出 ,除控制器外其他电路模块都比较简

单 ,限于篇幅不再赘述 ,在此只讨论控制器的设计问题。

3. 1 控制器的工作原理

信息技术与信息化

数据采集与嵌入式系统

2004 年第 4 期

37

© 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net