没有合适的资源?快使用搜索试试~ 我知道了~

ADN4604ASVZ-RL

需积分: 35 14 下载量 160 浏览量

2016-10-18

13:32:17

上传

评论

收藏 1.31MB PDF 举报

温馨提示

该ADN4604是一个16×16异步的,协议无关, 数字交叉点开关,带有16个差分PECL-/CML- 兼容的输入和16路差分CML输出. 该ADN4604是优化逆止到归零(NRZ)信号,每端口高达4.25 Gbps的数据速率.每个端口提供输入均衡和可编程输出摆幅和输出预加 重的固定水平.

资源推荐

资源详情

资源评论

4.25 Gbps,

16 × 16

,

Di

g

ital Cross

p

oint Switch

ADN4604

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

FEATURES

DC to 4.25 Gbps per port NRZ data rate

Programmable receive equalization

12 dB boost at 2 GHz

Compensates 40 inches of FR4 at 4.25 Gbps

Programmable transmit preemphasis/deemphasis

Up to 12 dB boost at 4.25 Gbps

Compensates 40 inches of FR4 at 4.25 Gbps

Low power: 130 mW per channel at 3.3 V (outputs enabled)

16 × 16, fully differential, nonblocking array

Double rank connection programming with dual

connection maps

Low jitter, typically 20 ps

Flexible I/O supply range

DC- or ac-coupled differential CML inputs

Programmable CML output levels

Per-lane input P/N pair inversion for routing ease

50 Ω on-chip I/O termination

Supports 8b/10b, scrambled or uncoded NRZ data

Serial (I

2

C slave or SPI) control interface

100-lead TQFP, Pb-free package

APPLICATIONS

Fiber optic network switching

High speed serial backplane routing to OC-48 with FEC

XAUI: 10GBASE-KX4

Gigabit Ethernet over backplane: 1000BASE-KX

1×, 2×, and 4× Fibre Channel

InfiniBand®

Digital video (HDMI, DVI, DisplayPort, 3G-/HD-/SD-SDI)

Data storage networks

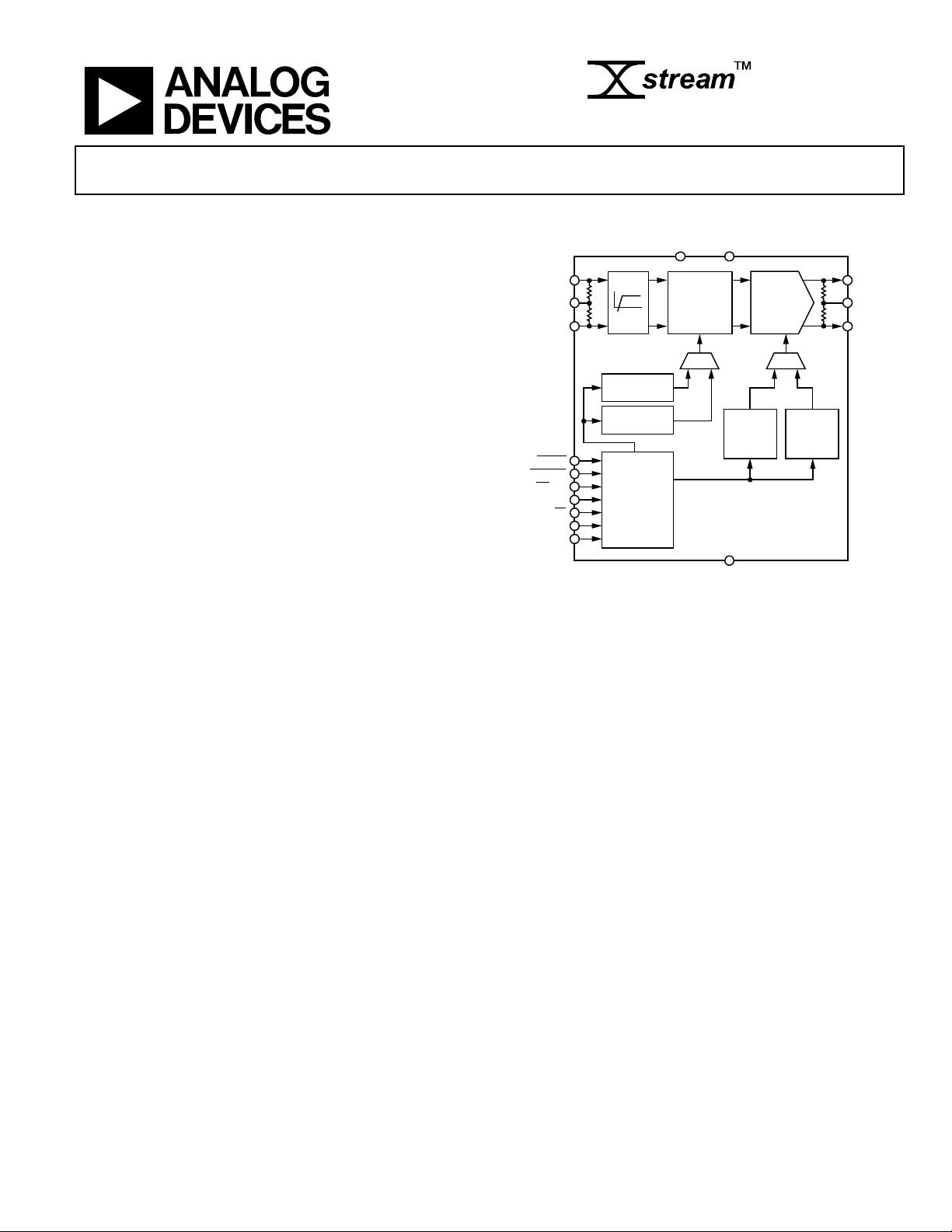

FUNCTIONAL BLOCK DIAGRAM

V

EQ

RX TX

PRE-

EMPHASIS

16 × 16

SWITCH

MATRIX

CONNECTION

MAP 0

CONNECTION

MAP 1

PER-PORT

OUTPUT

LEVEL

SETTINGS

OUTPUT

LEVEL

HOOKUP

TABLE

ADN4604

SERIAL

INTERFACE

CONTROL

LOGIC

CC

V

EE

DV

CC

OP[15:0]

V

TTON

,

V

TTOS

ON[15:0]

IP[15:0]

V

TTIE

,

V

TTIW

IN[15:0]

I2C/SPI

ADDR1/SDI

SDA/SDO

SCL/SCK

RESET

UPDATE

ADDR0/CS

07934-001

Figure 1.

GENERAL DESCRIPTION

The ADN4604 is a 16 × 16 asynchronous, protocol agnostic,

digital crosspoint switch, with 16 differential PECL-/CML-

compatible inputs and 16 differential CML outputs.

The ADN4604 is optimized for nonreturn-to-zero (NRZ) sig-

naling with data rates of up to 4.25 Gbps per port. Each port

offers a fixed level of input equalization and programmable

output swing and output preemphasis.

The ADN4604 nonblocking switch core implements a 16 × 16

crossbar and supports independent channel switching through

the serial control interface. The ADN4604 has low latency and

very low channel-to-channel skew.

An I

2

C® or SPI interface is used to control the device and pro-

vide access to advanced features, such as additional levels of

preemphasis and output disable.

The ADN4604 is packaged in a 100-lead TQFP package and

operates from −40°C to +85°C.

ADN4604

Rev. 0 | Page 2 of 40

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Specifications ............................................................... 3

I

2

C Timing Specifications ............................................................ 4

SPI Timing Specifications ........................................................... 5

Absolute Maximum Ratings ............................................................ 6

ESD Caution .................................................................................. 6

Pin Configuration and Function Descriptions ............................. 7

Typical Performance Characteristics ........................................... 10

Theory of Operation ...................................................................... 16

Introduction ................................................................................ 16

Receivers ...................................................................................... 16

Switch Core ................................................................................. 17

Transmitters ................................................................................ 19

Termination ................................................................................. 23

I

2

C Serial Control Interface ........................................................... 24

Reset ............................................................................................. 24

I

2

C Data Write ............................................................................. 24

I

2

C Data Read .............................................................................. 25

SPI Serial Control Interface .......................................................... 26

Register Map ................................................................................... 28

Applications Information .............................................................. 32

Supply Sequencing ..................................................................... 34

Power Dissipation....................................................................... 34

Output Compliance ................................................................... 34

Printed Circuit Board (PCB) Layout Guidelines ................... 36

Outline Dimensions ....................................................................... 38

Ordering Guide .......................................................................... 38

REVISION HISTORY

10/09—Revision 0: Initial Version

ADN4604

Rev. 0 | Page 3 of 40

SPECIFICATIONS

ELECTRICAL SPECIFICATIONS

V

CC

= 3.3 V, V

TTIx

= 3.3 V, V

TTOx

= 3.3 V, DV

CC

= 3.3 V, V

EE

= 0 V, R

L

= 50 Ω, data rate = 4.25 Gbps, ac-coupled inputs and outputs, differential

input swing = 800 mV p-p, T

A

= 27°C, unless otherwise noted.

Table 1.

Parameter Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

Data Rate (DR) per Channel (NRZ) DC 4.25 Gbps

Deterministic Jitter Data rate = 4.25 Gbps, no channel 20 ps p-p

Random Jitter RMS, no channel 1 ps rms

Residual Deterministic Jitter with

Receive Equalization

Data rate = 4.25 Gbps, 20 in. FR4, EQ boost = 12 dB 27 ps p-p

Data rate = 4.25 Gbps, 30 in. FR4, EQ boost = 12 dB 43 ps p-p

Data rate = 4.25 Gbps, 40 in. FR4, EQ boost = 12 dB 70 ps p-p

Residual Deterministic Jitter with

Transmit Preemphasis

Data rate = 4.25 Gbps, 20 in. FR4, PE boost = 4.2 dB 23 ps p-p

Data rate = 4.25 Gbps, 30 in. FR4, PE boost = 6 dB 25 ps p-p

Data rate = 4.25 Gbps, 40 in. FR4, PE boost = 6 dB 35 ps p-p

Propagation Delay Input to output, EQ boost = 12 dB 800 ps

Channel-to-Channel Skew ±50 ps

Switching Time Update logic switching to 50% output data 100 ns

Output Rise/Fall Time 20% to 80% 75 ps

INPUT CHARACTERISTICS

Differential Input Voltage Swing V

ICM

1

= V

CC

− 0.6 V; V

CC

= V

MIN

to V

MAX

, T

A

= T

MIN

to T

MAX

200 2000 mV p-p diff

Input Voltage Range Single-ended absolute voltage level, V

L

V

EE

+ 1.1 V

Single-ended absolute voltage level, V

H

V

CC

+ 0.3 V

OUTPUT CHARACTERISTICS

Output Voltage Swing Differential, PE boost = 0 dB, default output level, at dc 600 800 900 mV p-p diff

Output Voltage Range Single-ended absolute voltage level, V

L

V

CC

– 1.3 V

Single-ended absolute voltage level, V

H

V

CC

+ 0.2 V

Per-Port Output Current PE boost = 0 dB, default output level 16 mA

PE boost = 6 dB, default output level 32 mA

TERMINATION CHARACTERISTICS

Resistance Single-ended, V

CC

= 2.7 V to 3.6 V, V

TTI

= 2.2 V to 3.6 V,

V

TTO

= 2.2 V to 3.6 V, T

A

= T

MIN

to T

MAX

;

44 50 56 Ω

Temperature Coefficient 0.025 Ω/°C

POWER SUPPLY

Operating Range

V

CC

V

EE

= 0 V 2.7 3.3 3.6 V

DV

CC

V

EE

= 0 V 2.7 3.3 3.6 V

V

TTIE

, V

TTIW

V

EE

= 0 V 1.3 3.3 V

CC

+ 0.3 V

V

TTON

, V

TTOS

V

EE

= 0 V 2.2

2

3.3 V

CC

+ 0.3 V

Supply Current Outputs disabled

I

CC

95 110 mA

I

DVCC

20 35 mA

I

TTIE

+ I

TTIW

+ I

TTON

+ I

TTOS

0 10 mA

Supply Current All outputs enabled, ac-coupled I/O, 400 mV I/O swings

(800 mV p-p differential), PE boost = 0 dB,

50 Ω far-end terminations

I

CC

342 370 mA

I

DVCC

20 35 mA

I

TTIE

+ I

TTIW

+ I

TTON

+ I

TTOS

256 280 mA

Supply Current All outputs enabled, ac-coupled I/O, 400 mV I/O swings

(800 mV p-p differential), PE boost = 6 dB,

50 Ω far-end terminations

I

CC

486 540 mA

I

DVCC

20 35 mA

I

TTIE

+ I

TTIW

+ I

TTON

+ I

TTOS

512 540 mA

ADN4604

Rev. 0 | Page 4 of 40

Parameter Conditions Min Typ Max Unit

THERMAL CHARACTERISTICS

Operating Temperature Range −40 +85 °C

θ

JA

Still air; JEDEC 4-layer test board 24.9 °C/W

θ

JB

Still air 11.6 °C/W

θ

JC

At the exposed pad 0.95 °C/W

LOGIC CHARACTERISTICS

Input High Voltage Threshold (V

IH

) DV

CC

= 3.3 V 0.7 × V

CC

V

CC

V

Input Low Voltage Threshold (V

IL

) DV

CC

= 3.3 V V

EE

0.3 × V

CC

V

Output High Voltage (V

OH

) 2 kΩ pull-up resistor to DV

CC

DV

CC

V

Output Low Voltage (V

OL

) I

OL

= 3 mA V

EE

0.4 V

07934-002

1

V

ICM

is the input common-mode voltage.

2

Minimum V

TTO

is only applicable for a limited range of output current settings. Refer to the Power Dissipation section.

I

2

C TIMING SPECIFICATIONS

SPSrS

SDA

SCL

t

f

t

f

t

f

t

f

t

BUF

t

LOW

t

HD:STA

t

HD:DAT

t

HIGH

t

SU:DAT

t

SU:STA

t

SU:STO

t

HD:STA

Figure 2. I

2

C Timing Diagram

Table 2. I

2

C Timing Specifications

Parameter Symbol Min Max Unit

SCL Clock Frequency f

SCL

0 400+ kHz

Hold Time for a Start Condition t

HD;STA

0.6 μs

Setup Time for a Repeated Start Condition t

SU;STA

0.6 μs

Low Period of the SCL Clock t

LOW

1.3 μs

High Period of the SCL Clock t

HIGH

0.6 μs

Data Hold Time t

HD;DAT

0 μs

Data Setup Time t

SU;DAT

10 ns

Rise Time for Both SDA and SCL t

r

1 300 ns

Fall Time for Both SDA and SCL t

f

1 300 ns

Setup Time for Stop Condition t

SU;STO

0.6 μs

Bus-Free Time Between a Stop Condition and a Start Condition t

BUF

1 ns

Bus Idle Time After a Reset 10 ns

Reset Pulse Width 10 ns

ADN4604

Rev. 0 | Page 5 of 40

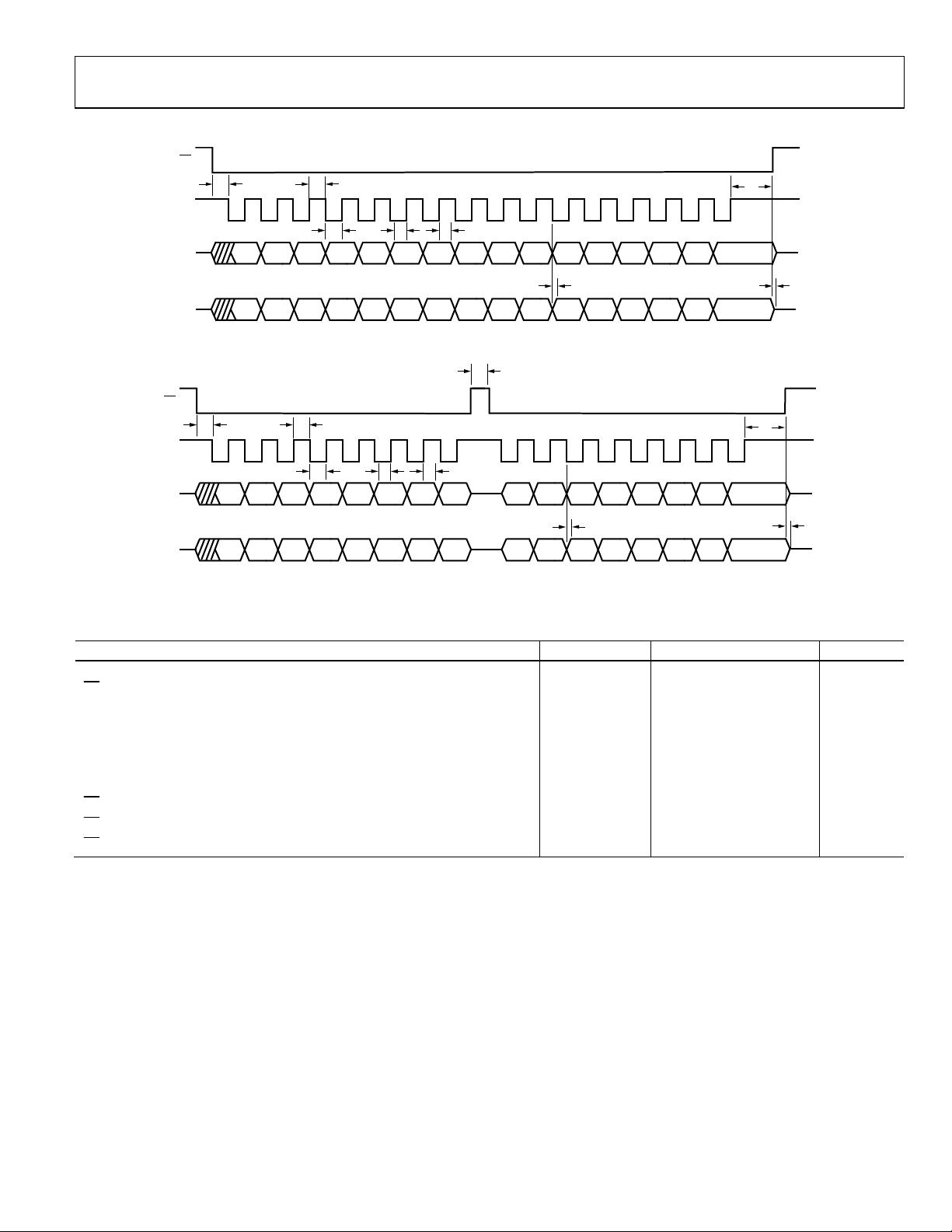

SPI TIMING SPECIFICATIONS

t

1

t

2

t

3

t

5

t

6

t

4

t

8

t

7

A7

CS

SCK

SDI

A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

SDO

XXXXXXXXXXXXXXX X

07934-003

Figure 3. SPI Write Timing Diagram

t

1

t

2

t

9

t

3

t

5

t

6

t

4

t

7

t

8

A7

CS

SCK

SDI

A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

X

SDO

X X X X X X X D7D6D5D4D3D2D1 D0

07934-004

Figure 4. SPI Read Timing Diagram

Table 3. SPI Timing Specifications

Parameter Symbol Min Max Unit

SCK Clock Frequency f

SCK

0 10 MHz

CS to SCK Setup Time

t

1

10 ns

SCK High Pulse Width t

2

40 ns

SCK Low Pulse Width t

3

40 ns

Data Access Time After SCK Falling Edge t

4

35 ns

Data Setup Time Prior to SCK Rising Edge t

5

20 ns

Data Hold Time After SCK Rising Edge t

6

10 ns

CS to SCK Hold Time

t

7

10

ns

CS to SDO High Impedance

t

8

40

ns

CS High Pulse Width

t

9

10

ns

剩余39页未读,继续阅读

资源评论

看雪

- 粉丝: 13

- 资源: 25

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 英雄联盟(League of Legends, LOL)数据集,包含:英雄联盟比赛数据,英雄联盟选手数据(KDA,伤害数,承伤数,补刀等),英雄联盟对战情况数据

- Python爬虫开发与实战-从入门到精通

- Spring项目集成FastDFS文件服务器代码

- 江科大STM32学习笔记(上)-最终版本

- 2024 Java offer 收割指南.pdf

- 12万字 java 面经总结.pdf

- SpringMVC面试题.pdf

- JAVA核心面试知识整理.pdf

- SpringCloud面试题.pdf

- SpringBoot面试题.pdf

- Spring面试专题.pdf

- 并发编程基础知识.pdf

- 代码随想录知识星球精华(最强八股文)第五版(Go篇).pdf

- 代码随想录知识星球精华(最强八股文)第五版(概述).pdf

- 代码随想录知识星球精华(最强八股文)第五版(面经篇).pdf

- 代码随想录知识星球精华(最强八股文)第五版(星球资源篇).pdf

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功