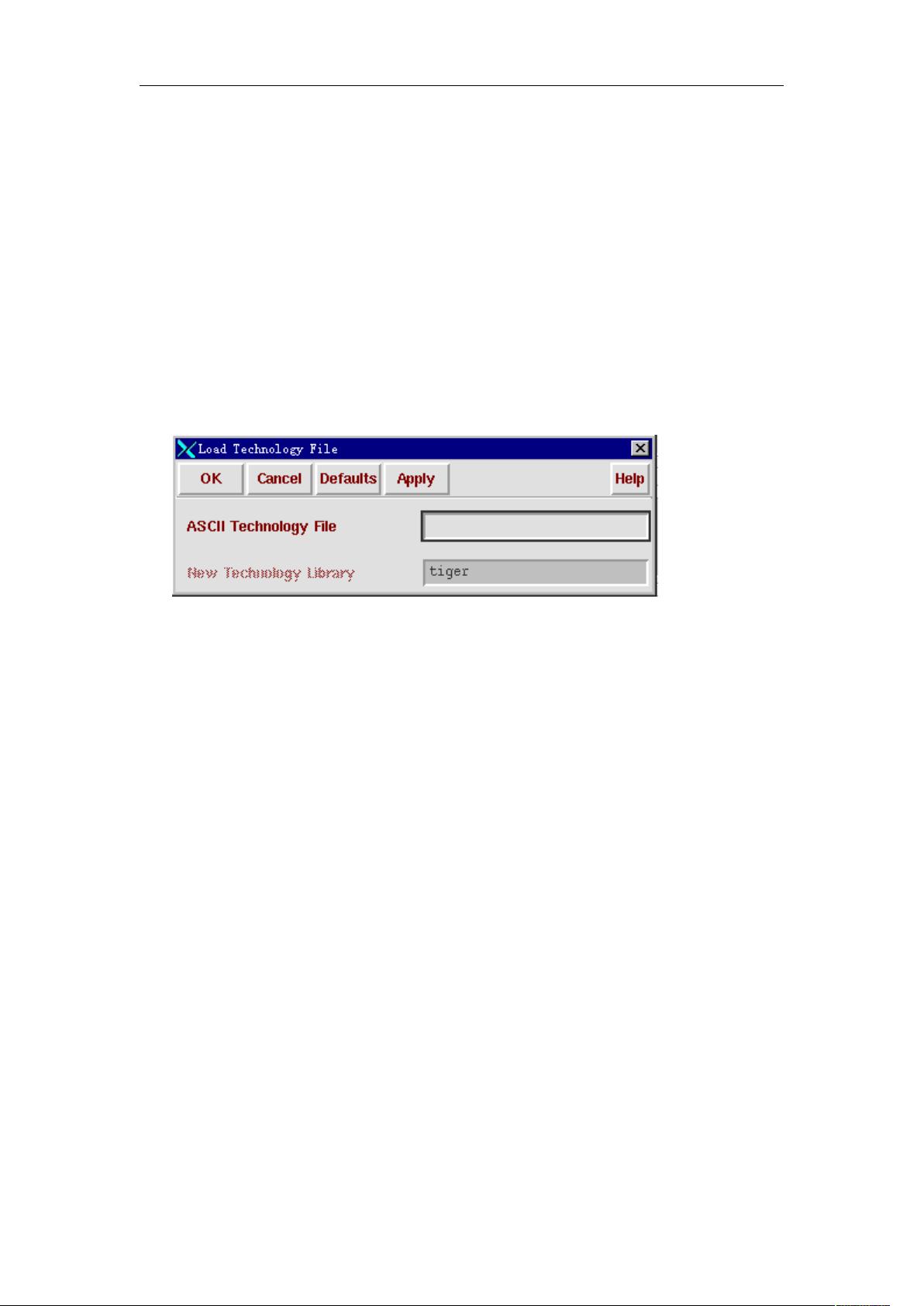

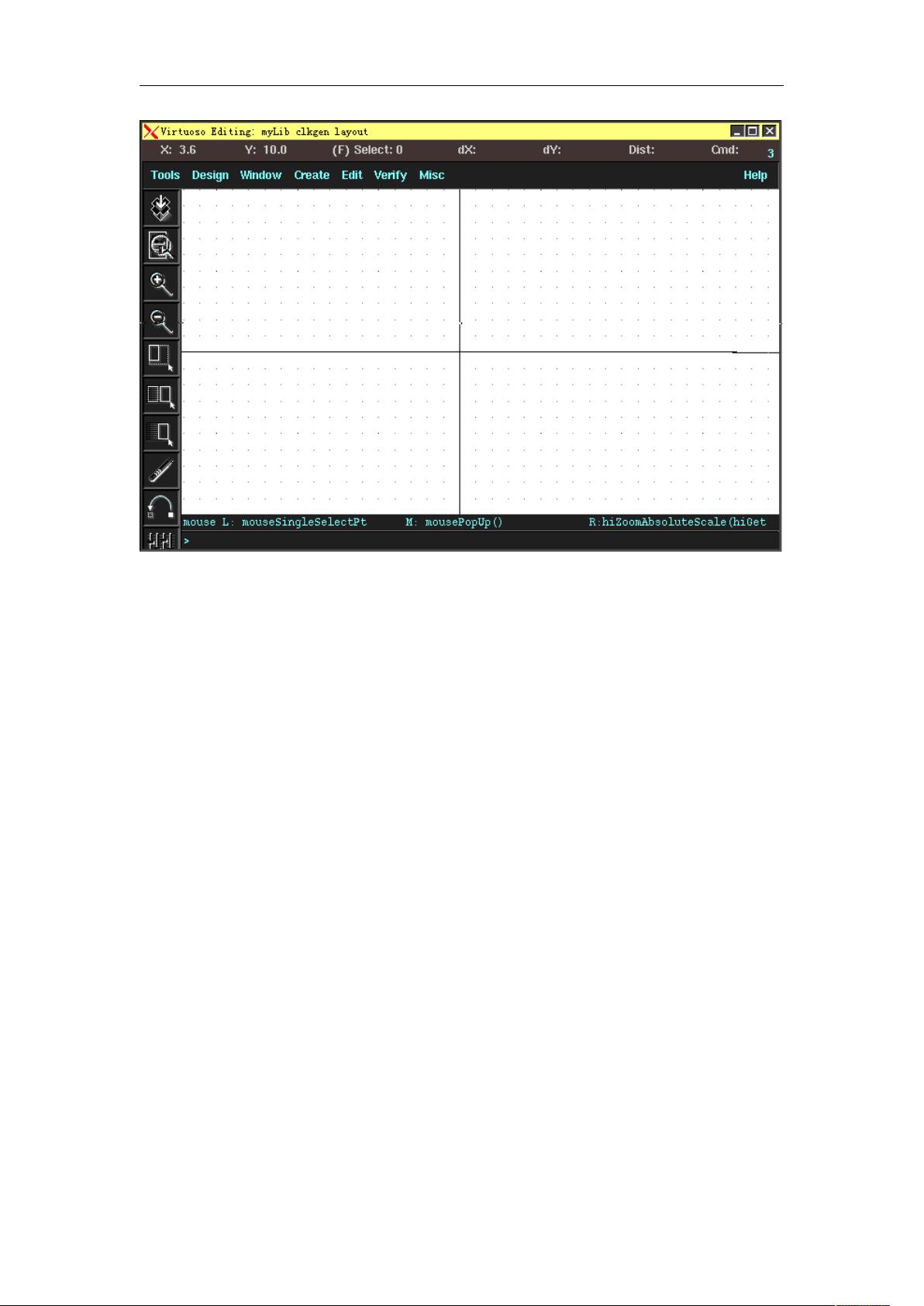

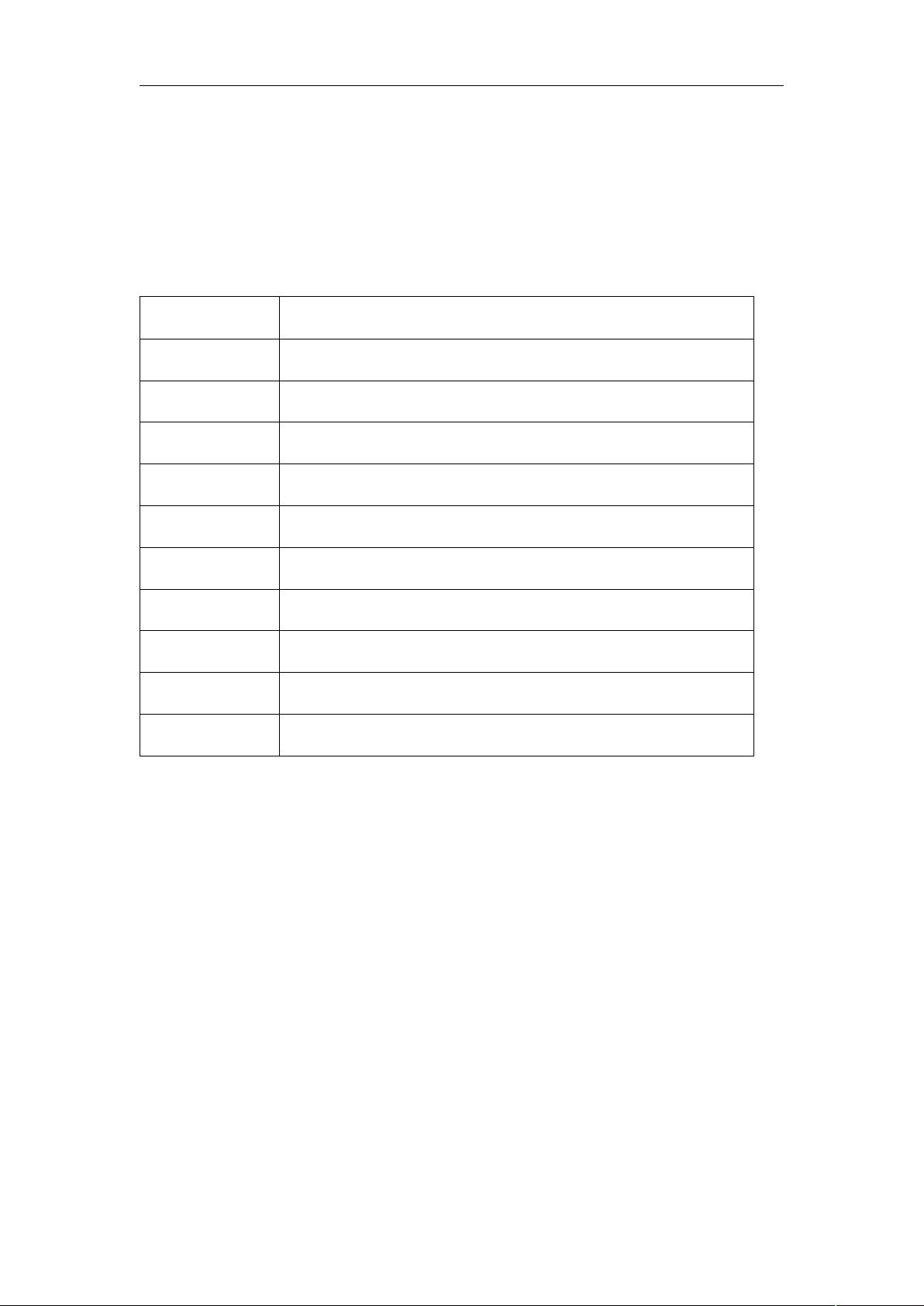

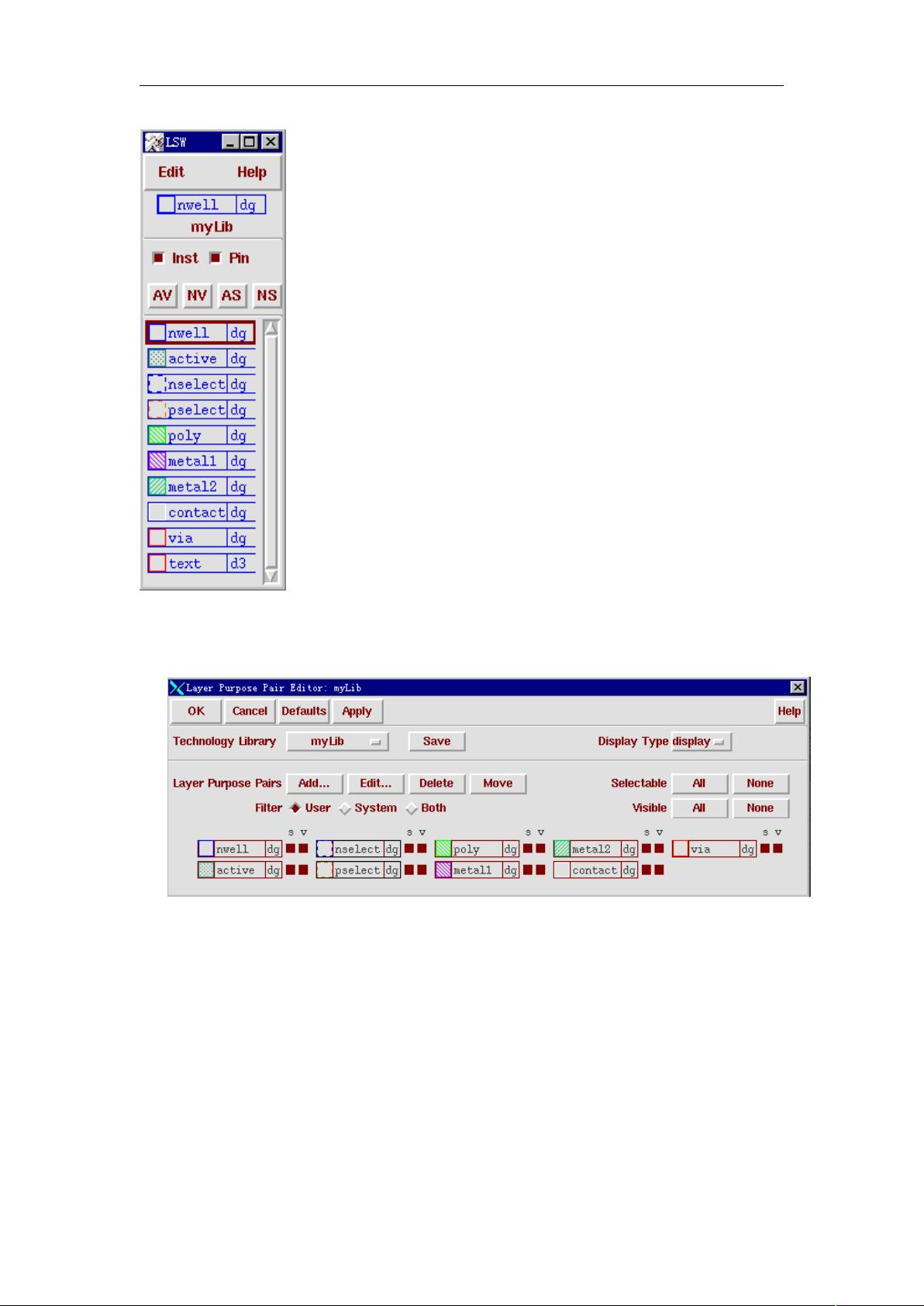

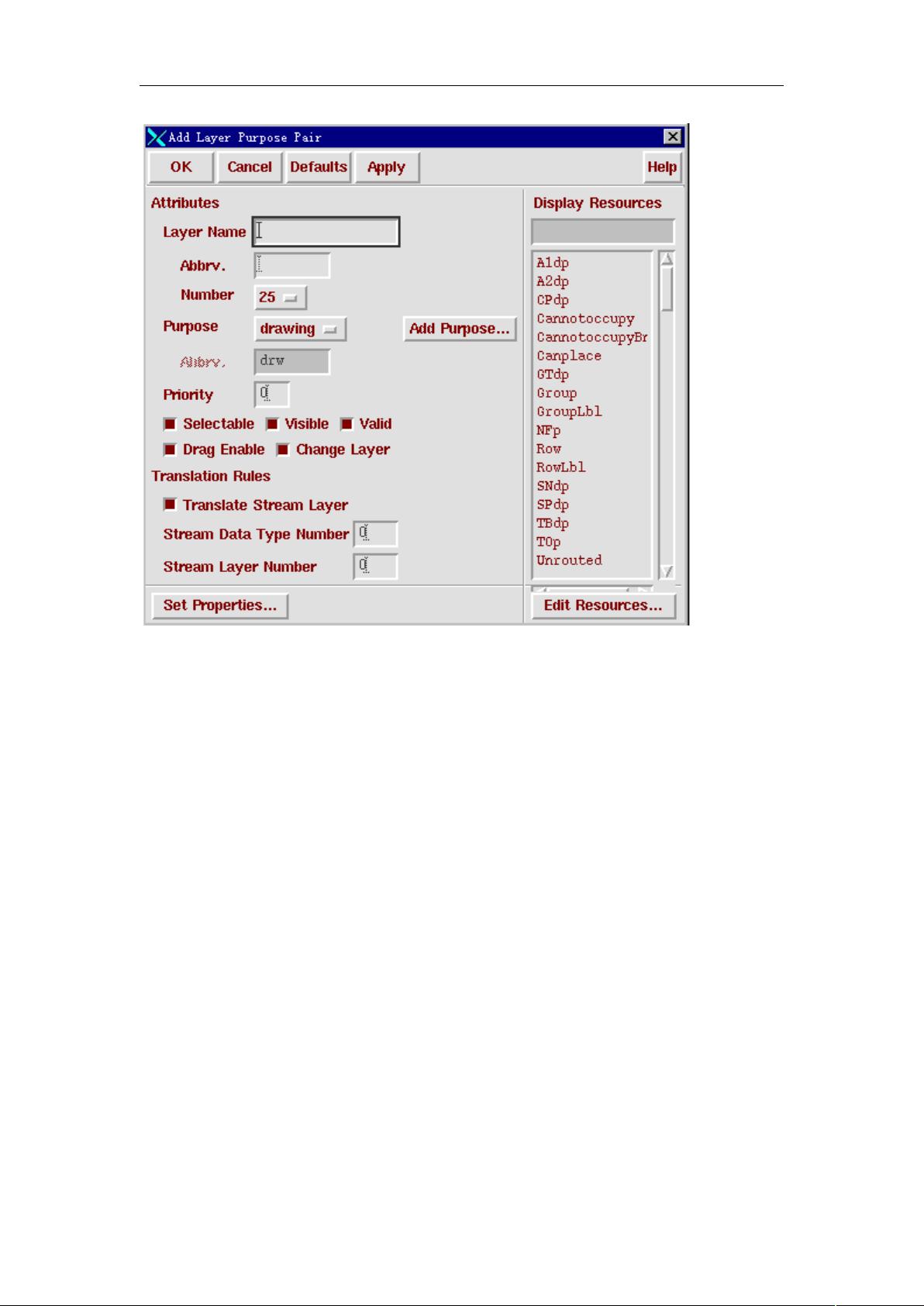

Cadence 版图设计 Cadence 版图设计是指使用 Cadence 软件绘制模拟集成电路的版图。版图设计是集成电路设计的重要步骤,涉及到电路的物理实现。通过 Cadence 版图设计,我们可以绘制出实用的模拟集成电路版图,以便在实际应用中使用。 Cadence cdsSPICE 是一个功能强大的模拟电路设计工具,可以帮助我们设计和模拟模拟电路。使用 Cadence cdsSPICE,我们可以快速地设计和模拟电路,提高设计效率和准确性。 在 Cadence 版图设计中,我们需要首先建立一个新的库 myLib,然后创建一个新的版图文件。在建立版图文件时,我们需要选择 compile a new tech file 或 attach to an existing tech file。然后,我们可以建立名为 inv 的 cell,并创建其 schematic view、symbol view 和 layout view。 在 layout view 中,我们可以使用 virtuoso editing 窗口来绘制版图。virtuoso editing 窗口由三部分组成:Icon menu、menu banner 和 status banner。Icon menu 列出了一些最常用的命令的图标,menu banner 包含了编辑版图所需要的各项指令,并按相应的类别分组。status banner 显示的是坐标、当前编辑指令等状态信息。 在版图视窗外的左侧还有一个层选择窗口(Layer and Selection Window LSW),可以选择所编辑图形所在的层,选择哪些层可供编辑,选择哪些层可以看到。为了绘制版图,我们需要建立我们自己的工艺库所需的版图层次及其显示属性。 绘制版图时,我们需要根据电路的设计要求选择合适的版图层次和显示属性,以确保版图的正确性和可靠性。 Cadence 版图设计为我们提供了一个强大的工具来实现模拟集成电路的设计和模拟,使得我们可以快速地设计和实现模拟电路。 Cadence 版图设计的优点包括: * 可以快速地设计和模拟模拟电路 * 可以提高设计效率和准确性 * 可以实现模拟集成电路的设计和模拟 * 可以快速地绘制版图和实现电路的物理实现 Cadence 版图设计的应用领域包括: * 模拟电路设计 * 集成电路设计 * 电子设计自动化 * 电路模拟和测试 Cadence 版图设计是一个功能强大的工具,可以帮助我们快速地设计和模拟模拟电路,并实现电路的物理实现。

剩余63页未读,继续阅读

- 粉丝: 0

- 资源: 11

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 面部、耳廓损伤损伤程度分级表.docx

- 农资使用情况调查问卷.docx

- 燃气管道施工资质和特种设备安装改造维修委托函.docx

- 食物有毒的鉴定方法.docx

- 市政道路工程联合质量抽检记录表.docx

- 市政道路工程联合质量抽检项目、判定标准、频率或点数.docx

- 视力听力残疾标准.docx

- 视器视力损伤程度分级表.docx

- 收回扣检查报告.docx

- 输液室管理制度、治疗配药室、注射室、处置室感染管理制度、查对制度.docx

- 听器听力损伤程度分级表.docx

- 新生儿评分apgar标准五项、五项体征的打分标准.docx

- 医疗废弃物环境风险评价依据、环境风险分析.docx

- 预防溺水宣传口号.docx

- 招标代理方案评分表.docx

- 职业暴露后的处理流程.docx

信息提交成功

信息提交成功

- 1

- 2

前往页