没有合适的资源?快使用搜索试试~ 我知道了~

Xilinx FPGA上QDMA的说明文档

需积分: 19 9 下载量 167 浏览量

2023-02-14

20:31:43

上传

评论 1

收藏 9.18MB PDF 举报

温馨提示

试读

171页

Xilinx FPGA上QDMA的说明文档

资源推荐

资源详情

资源评论

QDMA Subsystem for PCI

Express v4.0

产品指南

Vivado Design Suite

PG302 (v4.0) 2022 年 5 月 20 日

本文档为英语文档的翻译版本,若译文与英语原文存在歧义、差异、不一致或冲突,概以英语文档为准。译文可

能并未反映最新英语版本的内容,故仅供参考,请参阅最新版本的英语文档获取最新信息。

赛灵思⽮志不渝地为员⼯、客户与合作伙伴打造有归属感的包容性环境。

为此,我们正从产品和相关宣传资料中删除⾮包容性语⾔。我们已发起内

部倡议,以删除任何排斥性语⾔或者可能固化历史偏⻅的语⾔,包括我们

的软件和 IP 中嵌⼊的术语。虽然在此期间,您仍可能在我们的旧产品中

发现⾮包容性语⾔,但请确信,我们正致⼒于践⾏⾰新使命以期与不断演

变的⾏业标准保持⼀致。如需了解更多信息,请参阅此链接。

目录

第 1 章:引言...............................................................................................................................................................4

功能特性.......................................................................................................................................................................... 4

IP 相关信息......................................................................................................................................................................5

第 2 章:概述...............................................................................................................................................................6

QDMA 架构..................................................................................................................................................................... 6

限制................................................................................................................................................................................18

应用................................................................................................................................................................................19

许可和订购.....................................................................................................................................................................19

第 3 章:产品规格..................................................................................................................................................20

标准................................................................................................................................................................................20

性能和资源使用情况......................................................................................................................................................20

器件最低要求.................................................................................................................................................................22

QDMA 操作................................................................................................................................................................... 23

端口描述........................................................................................................................................................................ 80

寄存器空间.................................................................................................................................................................. 103

第 4 章:利用子系统进行设计.....................................................................................................................114

通用设计指南...............................................................................................................................................................114

时钟设置...................................................................................................................................................................... 115

串联配置...................................................................................................................................................................... 116

基于 PCIe 的 Dynamic Function eXchange............................................................................................................. 116

第 5 章:设计流程步骤..................................................................................................................................... 118

自定义和生成子系统....................................................................................................................................................118

约束子系统.................................................................................................................................................................. 133

仿真..............................................................................................................................................................................134

综合与实现.................................................................................................................................................................. 136

第 6 章:设计示例................................................................................................................................................137

可用设计示例...............................................................................................................................................................137

设计示例寄存器........................................................................................................................................................... 143

自定义和生成设计示例................................................................................................................................................150

第 7 章:测试激励文件..................................................................................................................................... 151

架构..............................................................................................................................................................................152

缩放式仿真超时........................................................................................................................................................... 152

PG302 (v4.0) 2022

年 5 月 20 日 china.xilinx.com

QDMA Subsystem for PCIe 2

Send Feedback

测试选择...................................................................................................................................................................... 152

波形转储...................................................................................................................................................................... 153

输出日志记录...............................................................................................................................................................153

测试描述...................................................................................................................................................................... 154

模型任务列表...............................................................................................................................................................154

附录 A:升级............................................................................................................................................................156

从 v3.1 到 v4.0 的更改.................................................................................................................................................156

与 DMA/Bridge Subsystem for PCI Express 的比较............................................................................................... 156

附录 B:调试........................................................................................................................................................... 157

在 Xilinx.com 上寻求帮助...........................................................................................................................................157

调试工具...................................................................................................................................................................... 158

硬件调试...................................................................................................................................................................... 158

附录 C:应用软件开发...................................................................................................................................... 159

器件驱动程序...............................................................................................................................................................159

Linux QDMA 软件架构 (PF/VF)..................................................................................................................................160

使用驱动程序...............................................................................................................................................................161

参考软件驱动程序流程................................................................................................................................................162

附录 D:附加资源与法律声明..................................................................................................................... 168

赛灵思资源.................................................................................................................................................................. 168

Documentation Navigator 与设计中心....................................................................................................................168

参考资料...................................................................................................................................................................... 168

修订历史...................................................................................................................................................................... 169

请阅读:重要法律声明................................................................................................................................................171

PG302 (v4.0) 2022 年 5 月 20 日 china.xilinx.com

QDMA Subsystem for PCIe 3

Send Feedback

第 1 章

引言

赛灵思 QDMA Subsystem for PCI Express (PCIe

®

) 旨在利用多队列的概念实现高性能 DMA,以搭配 PCI Express

®

3.x

Integrated Block 一起使用,它与 DMA/Bridge Subsystem for PCI Express 的不同之处在于,后者使用多个赛灵思卡到

主机 (C2H) 和主机到卡 (H2C) 通道。

本指南适用于面向 UltraScale+ 器件的 QDMA Subsystem for PCIe。如需了解有关 Versal

®

ACAP 子系统的详细信息,

请参阅《Versal ACAP DMA and Bridge Subsystem for PCI Express 产品指南》(PG344)。

功能特性

• UltraScale+

™

器件中支持 PCIe Integrated Block(PCIe 集成块)。

• 支持 64、128、256 和 512 位数据路径。

• 支持 x1、x2、x4、x8 或 x16 链路宽度。

• 支持 Gen1、Gen2 和 Gen3 链路速度。Gen4 适用于 PCIE4C 块。

• 支持 AXI4 存储器映射接口和 AXI4-Stream 接口(按队列)。

• 2048 个队列集合

○

2048 个 H2C 描述符环。

○

2048 个 C2H 描述符环。

○

2048 个 C2H 完成 (CMPT) 环。

• 支持轮询模式(状态描述符写回)和中断模式。

• 中断

○

2048 个 MSI-X 矢量。

○

每个功能最多 8 个 MSI-X。

注释:可以为每个功能分配更多矢量。如需了解更多信息,请参阅答复记录 72352。

○ 中断聚合。

• C2H 串流中断调制。

• C2H 串流完成队列条目合并。

• 通过用户逻辑进行描述符和 DMA 自定义

○

允许定制描述符格式。

○

流量管理。

第 1 章:引言

PG302 (v4.0) 2022 年 5 月 20 日 china.xilinx.com

QDMA Subsystem for PCIe 4

Send Feedback

• 支持含最多 4 个物理功能 (PF) 和 252 个虚拟功能 (VF) 的 SR-IOV

○ 精简虚拟机管理器型号。

○ QID 虚拟化。

○ 仅允许有特权的功能/物理功能对上下文和寄存器进行编程。

○ 支持功能级别复位 (FLR)。

○ 邮箱。

• 基于队列的丰富可编程性,例如,AXI4 存储器映射接口对比 AXI4-Stream 接口。

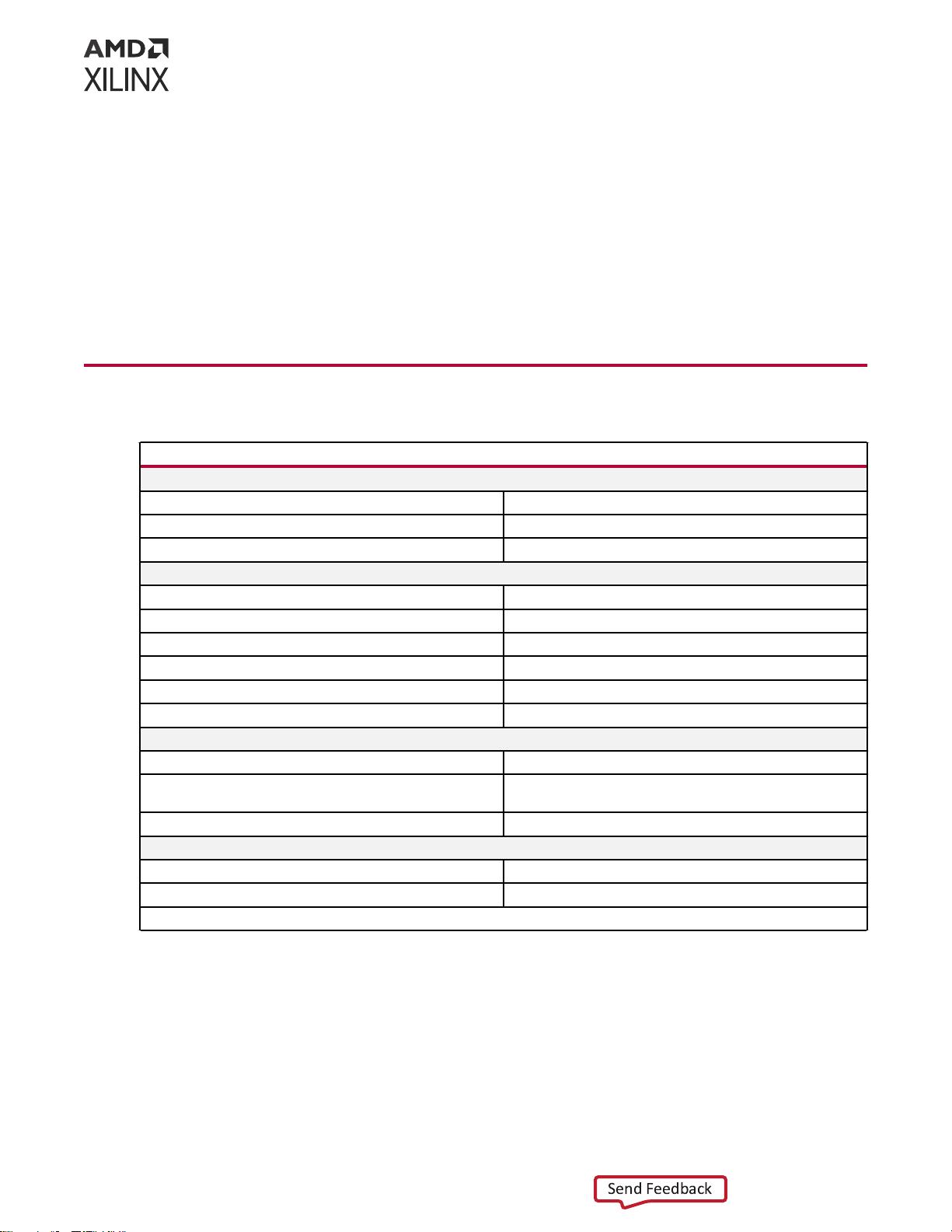

IP 相关信息

LogiCORE IP 相关信息表

子系统规格

支持的器件系列

1

UltraScale+

™

支持的用户接口 AXI4 存储器映射、AXI4-Stream、AXI4-Lite

资源 资源使用情况网页。

子系统

设计文件 加密 System Verilog

设计示例 Verilog

测试激励文件 Verilog

约束文件 赛灵思约束文件 (XDC)

仿真模型 Verilog

支持的软件驱动程序 Linux、DPDK 和 Windows 驱动程序

2

经过测试的设计流程

3

设计输入 Vivado Design Suite

仿真 如需了解受支持的仿真器的相关信息,请参阅赛灵思设计工具:

版本说明指南。

综合 Vivado 综合

支持

版本说明和已知问题 主答复记录:70927

所有 Vivado IP 变更日志 Vivado IP 主变更日志:72775

赛灵思技术支持网页

注释:

1. 如需获取受支持的器件的完整列表,请参阅 Vivado IP 目录。

2. 如需获取驱动程序详情,请参阅赛灵思 DMA IP 驱动程序。

3. 如需了解受支持的工具版本的相关信息,请参阅赛灵思设计工具:版本说明指南。

4. 对于 Versal ACAP,请参阅《Versal ACAP DMA and Bridge Subsystem for PCI Express 产品指南》(PG344)。

第 1 章:引言

PG302 (v4.0) 2022 年 5 月 20 日 china.xilinx.com

QDMA Subsystem for PCIe 5

Send Feedback

剩余170页未读,继续阅读

资源评论

yunsun

- 粉丝: 1

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功