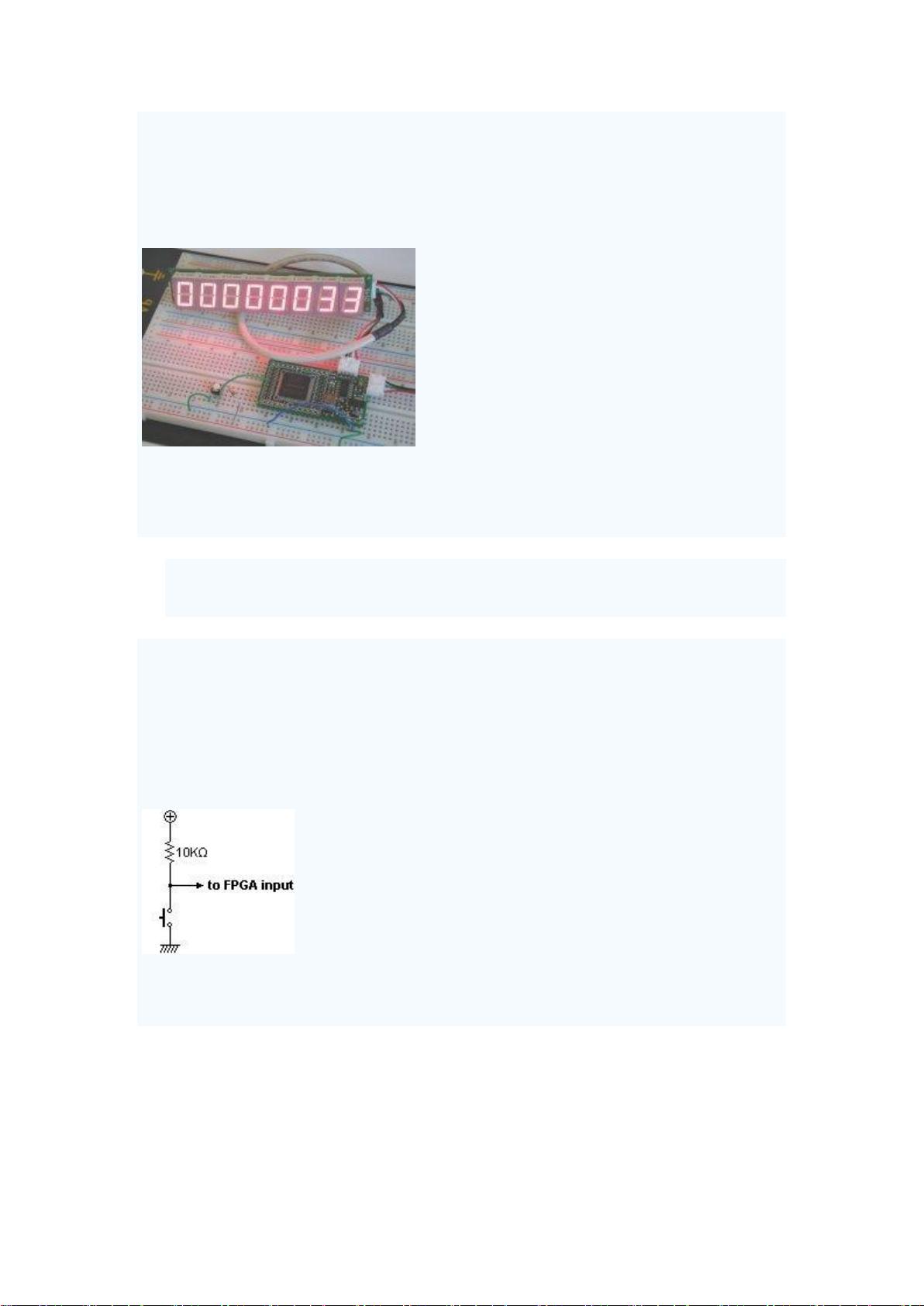

### FPGA按键防抖详解 #### 引言 在FPGA设计中,处理机械按键的输入是一项常见的任务。然而,由于机械按键的物理特性,按下或释放按键时会产生一系列的抖动信号,这可能导致误操作,尤其是在高速数字系统中。本文将深入探讨FPGA中的按键防抖技术,以及如何使用Verilog语言实现这一功能。 #### 按键抖动问题描述 当一个机械按键被按下或释放时,由于物理接触的不稳定,会产生多个快速的闭合和断开信号,这就是所谓的“按键抖动”。这种现象对于人类来说几乎不可察觉,但对于敏感的数字电路,特别是高速运行的FPGA,却能造成显著的影响。如果不加以处理,这些抖动信号会被错误地识别为多次按键动作,从而导致程序逻辑的混乱。 #### 解决方案:软件防抖 传统的解决方案是在硬件层面上添加RC滤波器或施密特触发器来消除抖动,但这增加了系统的复杂性和成本。在FPGA中,可以采用更为灵活且高效的软件防抖技术。这种方法的核心是利用FPGA内部的计数器和时序控制,来判断按键的真实状态变化。 #### Verilog实现 在Verilog中实现按键防抖主要涉及以下几个步骤: 1. **信号同步**:需要将外部按键信号PB(低有效)同步至内部时钟域,以避免异步信号引起的元器件不稳定。这通常通过两级D触发器实现,确保信号的稳定过渡。 2. **计数器设计**:接下来,设计一个足够宽的计数器(例如,16位),用于测量按键状态变化的持续时间。计数器的溢出时间应足以覆盖最长的按键抖动周期,一般设置为2-10ms之间。 3. **状态检测**:定义一个状态变量PB_state,用于存储按键的当前状态(按下或释放)。同时,通过比较PB_state与同步后的PB信号,判断是否发生了真实的按键状态变化。 4. **防抖逻辑**:当检测到按键状态变化时,启动计数器。一旦计数器达到预设阈值(即溢出),确认按键状态确实改变,更新PB_state的值。此外,通过PB_down和PB_up信号,分别指示按键被按下和释放的瞬间。 #### 实现细节 ```verilog module PushButton_Debouncer(clk, PB, PB_state, PB_up, PB_down); input clk; // 时钟信号 input PB; // 原始按键信号,低有效 output PB_state; // 按键状态,高有效表示按下 output PB_down; // 按下瞬间脉冲 output PB_up; // 释放瞬间脉冲 reg PB_sync_0; // 第一级同步触发器 always @(posedge clk) PB_sync_0 <= ~PB; reg PB_sync_1; // 第二级同步触发器 always @(posedge clk) PB_sync_1 <= PB_sync_0; reg [15:0] PB_cnt; // 计数器,用于防抖检测 reg PB_state; // 当前按键状态 wire PB_idle = (PB_state == PB_sync_1); // 检测按键状态是否变化 wire PB_cnt_max = &PB_cnt; // 检查计数器是否溢出 always @(posedge clk) begin if (!PB_idle) begin PB_cnt <= PB_cnt + 1; if (PB_cnt_max) PB_state <= ~PB_state; end else PB_cnt <= 0; end assign PB_down = ~PB_state & ~PB_idle & PB_cnt_max; // 按下瞬态 assign PB_up = PB_state & ~PB_idle & PB_cnt_max; // 释放瞬态 endmodule ``` #### 结论 通过上述方法,可以在FPGA中有效地实现按键防抖,提高系统对按键输入的准确性和响应速度。软件防抖不仅减少了对外部硬件的需求,还提供了更高的灵活性和可配置性,能够适应不同应用场景下的需求。在实际开发中,根据具体按键的特性和系统时钟频率,可能需要调整计数器的宽度和溢出时间,以达到最佳的防抖效果。

- 粉丝: 1

- 资源: 5

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功