没有合适的资源?快使用搜索试试~ 我知道了~

单片机音乐彩灯设计.doc

1 下载量 76 浏览量

2022-11-29

00:21:48

上传

评论

收藏 729KB DOC 举报

温馨提示

试读

14页

单片机音乐彩灯设计.doc

资源推荐

资源详情

资源评论

..

-

. . word.zl-

艺术彩灯控制系统设计

一. 概述

1.1 艺术彩灯的设计背景及意义

彩灯是人们日常生活中的一种装饰用品,它美观大方,尤其在节日期间,倍增节日气氛。它

蕴涵着丰富的文化底蕴,被广泛地应用于各种店面的装饰。变换无穷的彩灯样式,给城市增

添活力,吸引着人们的注意力,深受人民的喜爱。在日常生活中,人们还将彩灯摆放成各种

图案,增添美感。随着电子技术的开展,应用系统向着小型化、快速化、大容量、重量轻的

方向开展。科学技术更加贴近人们的生活,向着满足人们需求的方向开展。节日彩灯的设计

与制作工艺也一步一步的走向成熟。

1.2 系统设计功能概述

本设计是以 AT89C51 单片机为根底的音乐彩灯控制方案,来实现对 LED 彩灯的控制。以

AT89C51 单片机作为主控核心,通过汇编语言来控制单片机按下“开场〞按键,8 个 LED

灯从上到下开场循环点亮,按下“上〞按键,灯由上向下流动,按下“下〞按键,灯由下向

上流动,按下“停顿〞按键,所有灯为暗。

二.彩灯设计容简要:

2.1 彩灯设计任务:

以单片机为核心,设计一个节日音乐彩灯控制器。

2.2 彩灯设计要求:

P1.2----开场,按此键那么灯开场流动〔由上而下〕。 P1.3----停顿,按此键那么停顿流动,所

有灯为暗。 P1.4----上,按此键那么灯由上向下流动。 P1.5----下,按此键那么灯由下向上流

动。

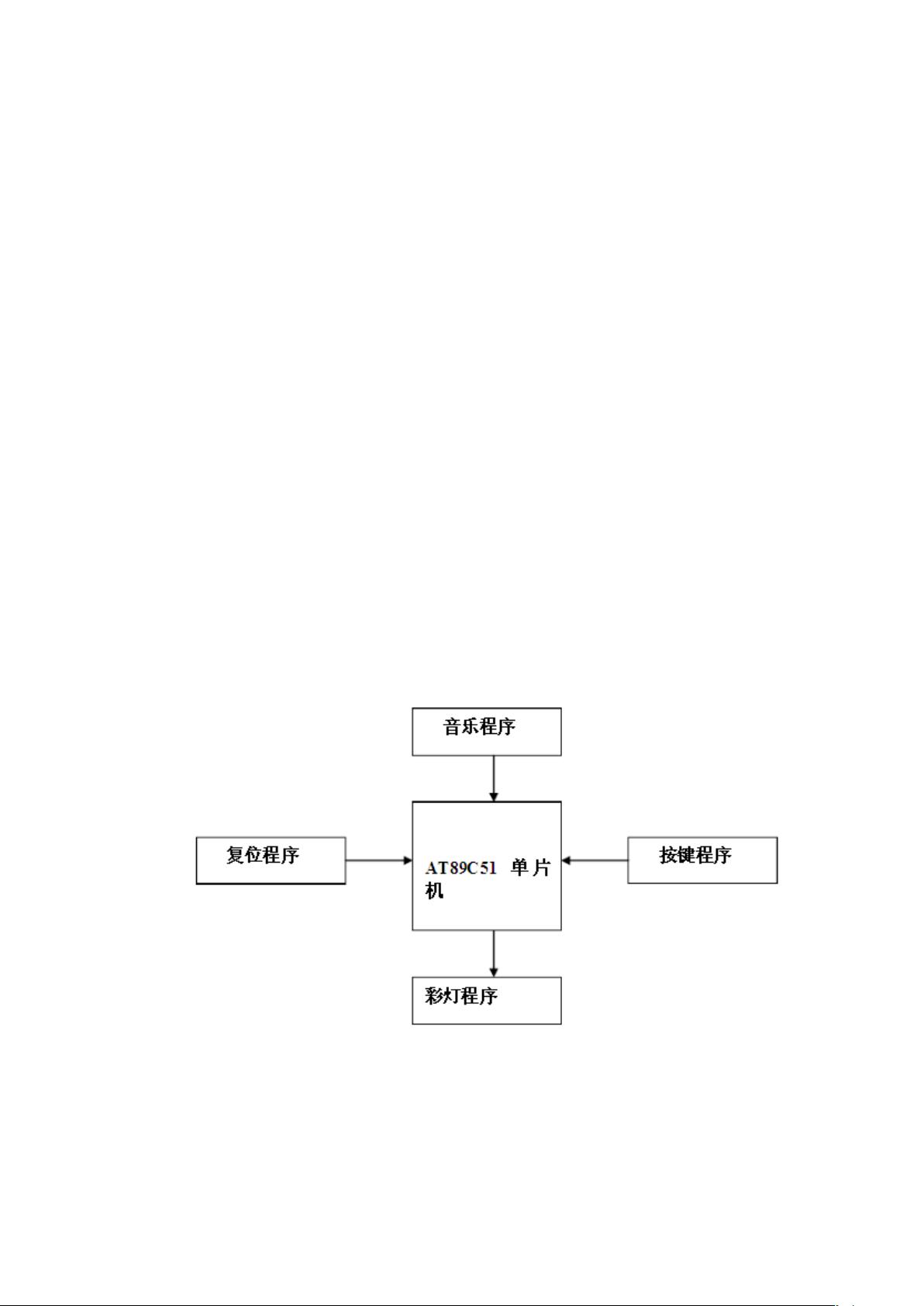

2.3 彩灯总体控制框图:

..

-

. . word.zl-

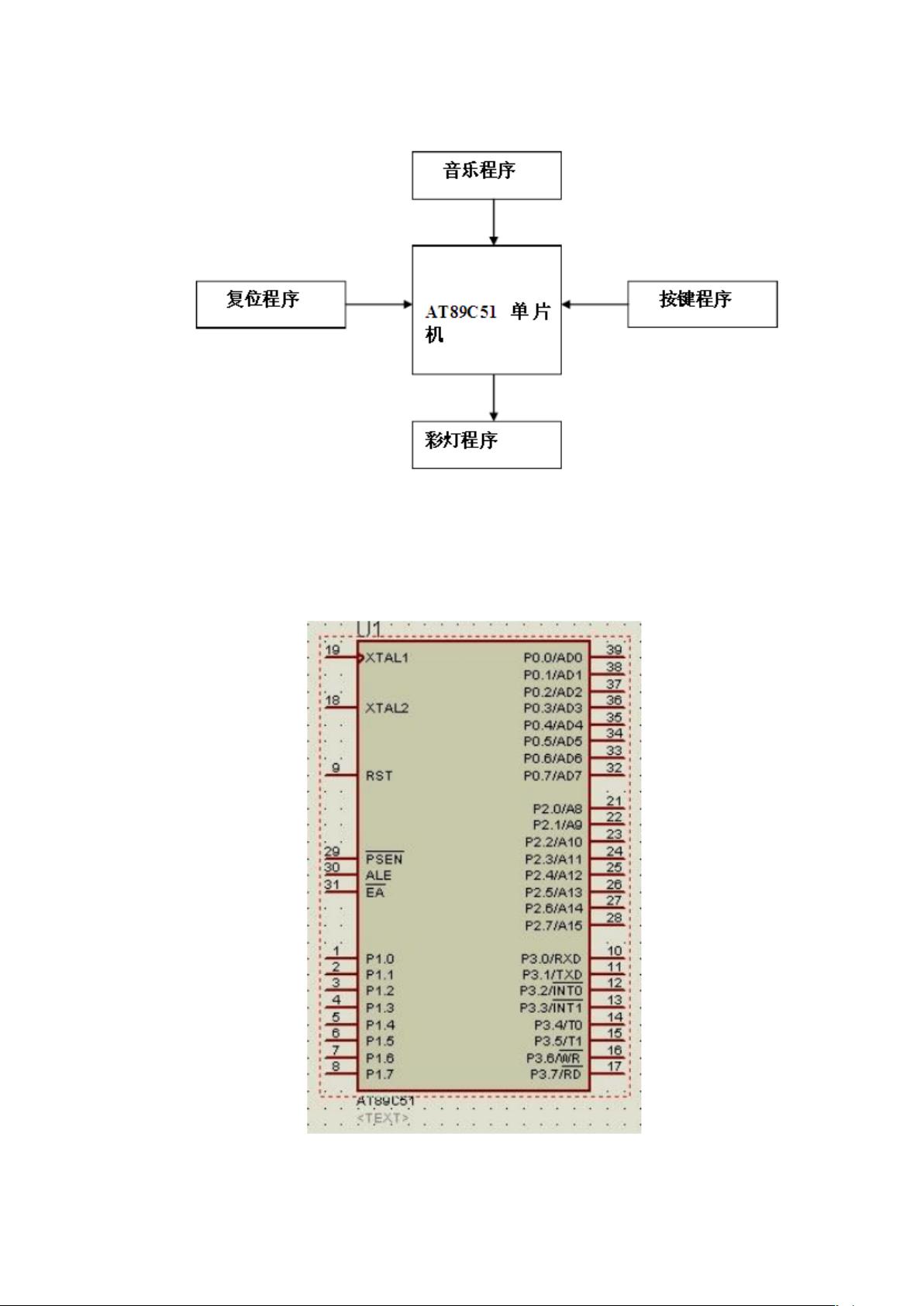

3.2 AT89C51 单片机硬件构造:

AT89C51 是 一 种 带 4K 字 节 闪 存 可 编 程 可 擦 除 只 读 存 储 器

〔FPEROM—Flash Programmable and Erasable Read Only Memory〕的单片机芯片,它采用静

态 CMOS 工艺制造 8 位微处理器,最高工作频率位 24MHZ。AT89C5 外形及引脚排列如下

图:

管脚说明:

..

-

. . word.zl-

RST:复位输入。当振荡器复位器件时,要保持 RST 脚两个机器周期的高电平时间。

P0 口:P0 口为一个 8 位漏级开路双向 I/O 口,每脚可吸收 8TTL 门电流。当 P1 口的管脚第

一次写 1 时,被定义为高阻输入。P0 能够用于外部程序数据存储器,它可以被定义为数据/

地址的第八位。在 FIASH 编程时,P0 口作为原码输入口,当 FIASH 进展校验时,P0 输出

原码,此时 P0 外部必须被拉高。

P1 口:P1 口是一个部提供上拉电阻的 8 位双向 I/O 口,P1 口缓冲器能接收输出 4TTL 门

电流。P1 口管脚写入 1 后,被部上拉为高,可用作输入,P1 口被外部下拉为低电平时,将

输出电流,这是由于部上拉的缘故。在 FLASH 编程和校验时,P1 口作为第八位地址接收。

P2 口:P2 口为一个部上拉电阻的 8 位双向 I/O 口,P2 口缓冲器可接收,输出 4 个 TTL 门

电流,当 P2 口被写“1”时,其管脚被部上拉电阻拉高,且作为输入。并因此作为输入时,

P2 口的管脚被外部拉低,将输出电流。这是由于部上拉的缘故。P2 口当用于外部程序存储

器或 16 位地址外部数据存储器进展存取时,P2 口输出地址的高八位。在给出地址“1”时,

它利用部上拉优势,当对外部八位地址数据存储器进展读写时,P2 口输出其特殊功能存放

器的容。P2 口在 FLASH 编程和校验时接收高八位地址信号和控制信号。

P3 口:P3 口管脚是 8 个带部上拉电阻的双向 I/O 口,可接收输出 4 个 TTL 门电流。当 P3

口写入“1”后,它们被部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,

P3 口将输出电流〔ILL〕这是由于上拉的缘故。

ALE/PROG:当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。

在 FLASH 编程期间,此引脚用于输入编程脉冲。在平时,ALE 端以不变的频率周期输出正

脉冲信号,此频率为振荡器频率的 1/6。因此它可用作对外部输出的脉冲或用于定时目的。

然而要注意的是:每当用作外部数据存储器时,将跳过一个 ALE 脉冲。如想制止 ALE 的输

出可在 SFR8EH 地址上置 0。此时, ALE 只有在执行 MOVX,MOVC 指令是 ALE 才起作用。

另外,该引脚被略微拉高。如果微处理器在外部执行状态 ALE 制止,置位无效。

PSEN:外部程序存储器的选通信号。在由外部程序存储器取指期间,每个机器周期两次

PSEN 有效。但在访问外部数据存储器时,这两次有效的 PSEN 信号将不出现。

EA/VPP:当 EA 保持低电平时,那么在此期间外部程序存储器

〔0000H-FFFFH〕,不管是否有部程序存储器。注意加密方式 1 时,EA 将部锁定为 RESET;

当 EA 端保持高电平时,此间部程序存储器。 XTAL1 和 XTAL2:反向振荡放大器的输入

及部时钟工作电路的输入。

3.3 系统的硬件构成及功能描述:

控制系统硬件设计电路图如下图:

剩余13页未读,继续阅读

资源评论

智慧安全方案

- 粉丝: 3615

- 资源: 59万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功