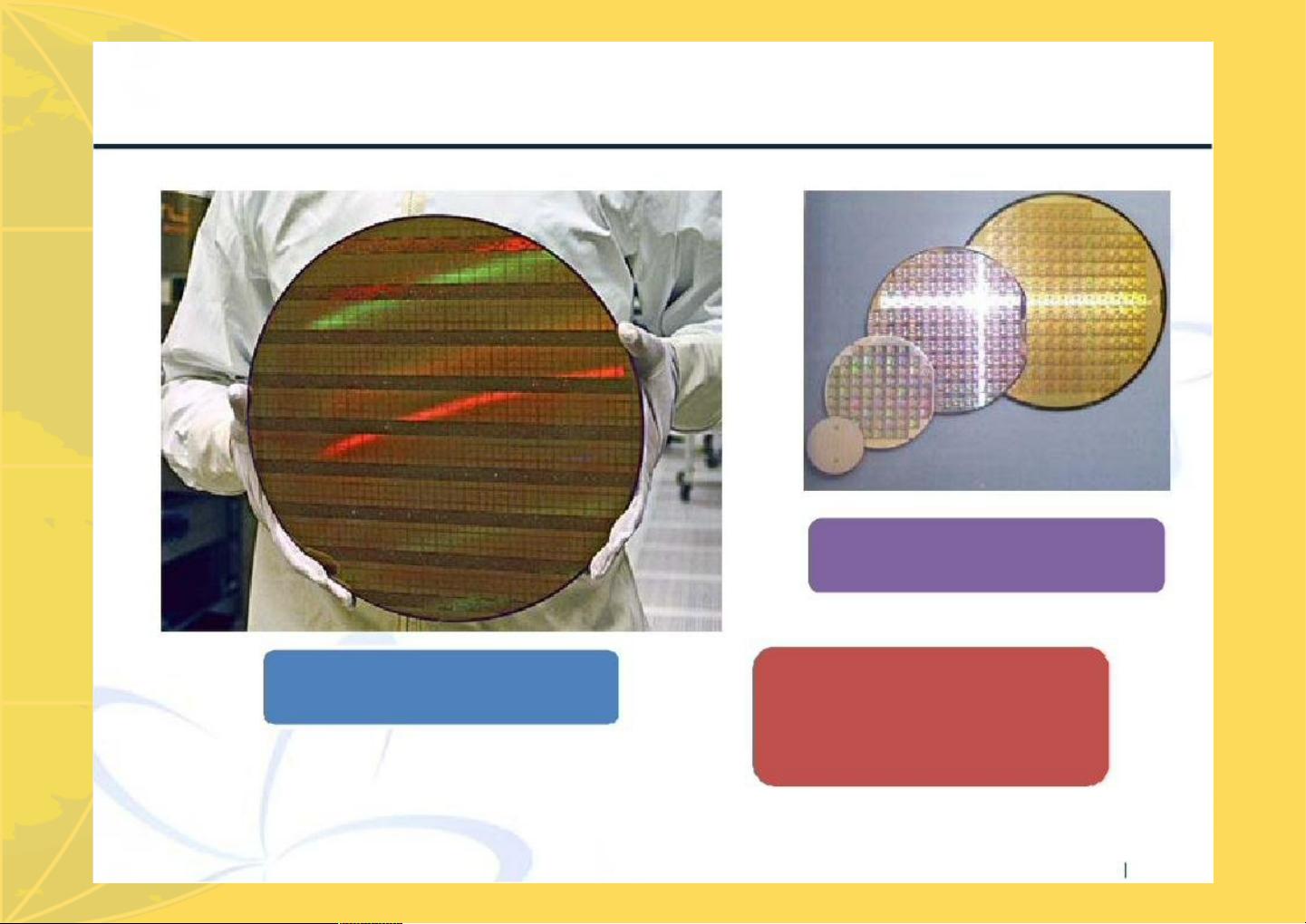

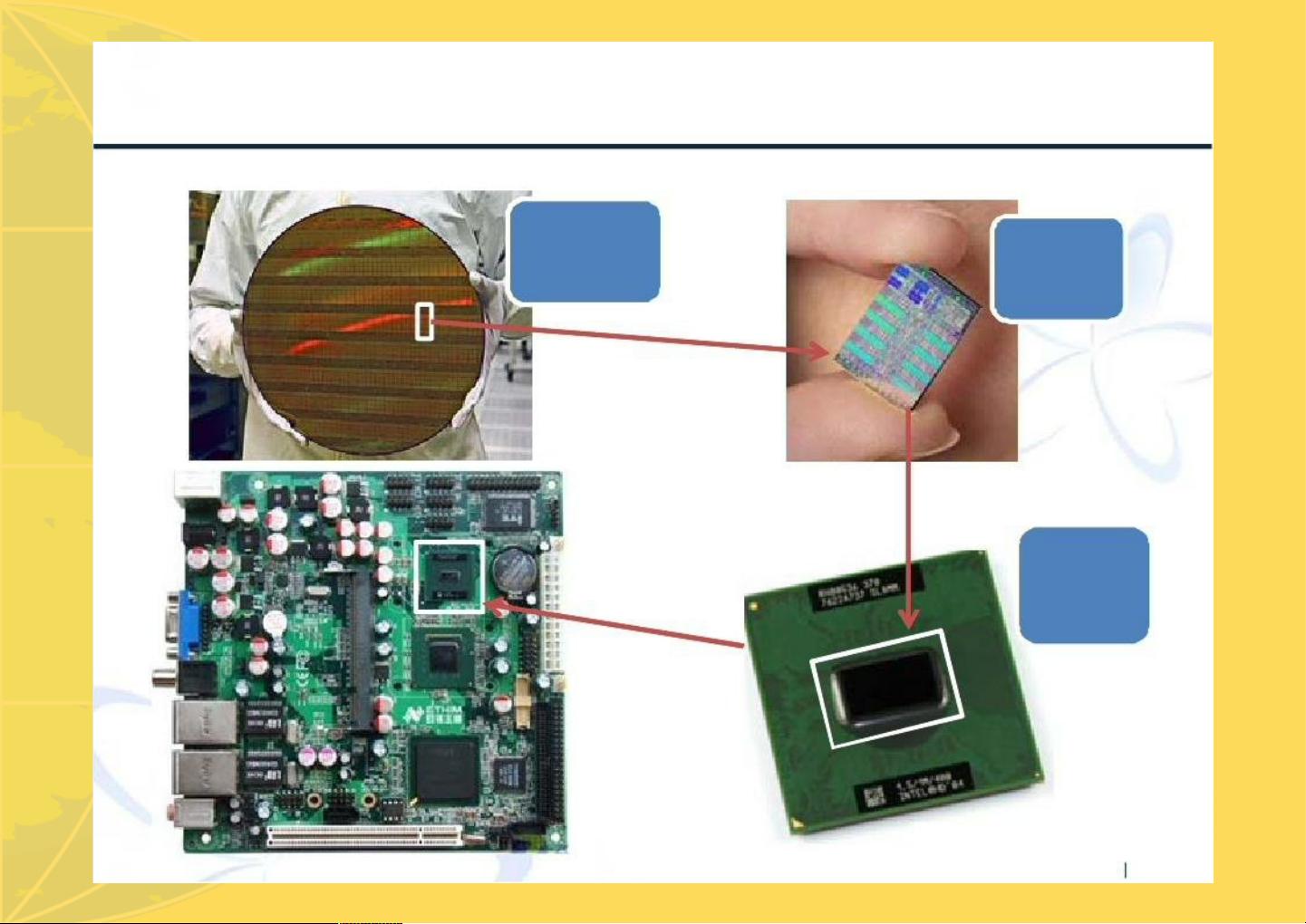

在电子技术领域,系统芯片(System-on-Chip, SoC)和片上通信结构是现代集成电路设计中的核心概念。本文将深入探讨这些主题,旨在理解芯片的制造与封装过程,系统芯片的定义与特点,以及系统总线和片上总线在构建复杂集成电路中的作用。 我们来看芯片的制造和封装。制造过程通常始于晶圆的生产,晶圆是由硅等半导体材料制成的圆形薄片,常见尺寸有2、4、6、8英寸以及目前主流的12英寸,未来甚至可能发展到18英寸。芯片制造包括多个步骤,如光刻、掺杂、蚀刻等,最终将电路图案转移到晶圆上,形成一个个微小的裸片Die。接着,Die经过切割、微连接技术和封装工艺,如引线键合、倒装片技术,将它们封装成我们常见的集成电路芯片。封装技术多样,如TSOP(薄型小尺寸封装)、QFP(四侧引脚扁平封装)、PGA(引脚网格阵列)和BGA(球栅阵列),每种封装方式都有其适用场景和优势。 系统芯片(SoC)是将处理器、内存、接口和其他逻辑组件集成在一个单一芯片上的设计。随着微电子技术的进步,SoC的集成度不断提高,使得在单一芯片上可以集成数百乃至数千的处理单元和存储单元。例如,现代的微处理器通常包含了CPU、内存控制器、显卡控制器等组件,形成了一个完整的计算平台。 系统总线和片上总线是SoC内部通信的关键。系统总线是连接计算机系统各个主要部件的公共通信路径,例如传统的北桥和南桥芯片,分别负责CPU与内存、I/O设备之间的数据交换。而片上总线则是在SoC内部,用于连接不同功能模块,如处理器核、存储器和外设接口。随着技术的发展,越来越多的系统开始采用单芯片解决方案,如单芯片计算机,以减少延迟并提高效率。 在片上通信结构的新发展中,分布式译码技术成为解决大量处理单元和存储单元之间高效通信的关键。分布式译码通过将地址空间分配给不同的模块,减少了对中央总线资源的需求,提高了系统的并行处理能力。此外,不同总线标准如AHB(Advanced High-performance Bus)和PCI(Peripheral Component Interconnect)也扮演着重要角色,它们提供了灵活的数据传输机制和模块间的通信规范。 未来,随着摩尔定律的延续,单个芯片内的处理和存储单元将继续增多,对片上通信结构提出更高的要求。这涉及到如何优化总线协议、提高带宽、降低延迟以及确保系统的可扩展性和可靠性。因此,对系统总线和片上通信结构的研究将持续推动集成电路技术的创新和发展。

剩余53页未读,继续阅读

- 粉丝: 3815

- 资源: 59万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功