没有合适的资源?快使用搜索试试~ 我知道了~

ADS1263/1262是TI公司生产的32位ADC,这是全中文版用户手册。

资源推荐

资源详情

资源评论

具有可编程增益放大器 (PGA) 和电压基准的 ADS126x 32 位、38kSPS、精密模

数转换器 (ADC)

1 特性

• 32 位精密 Δ-Σ ADC

• 24 位辅助 Δ-Σ ADC (ADS1263)

• 数据速率:2.5SPS 至 38400SPS

• 差分输入,CMOS PGA

• 11 个多功能模拟输入

• 高精度架构:

– 温漂:1nV/°C

– 增益漂移:0.5ppm/°C

– 噪声:7nV

RMS

(2.5SPS,增益 = 32)

– 线性度:3ppm

• 2.5V 内部电压基准:

– 温漂:2ppm/°C

• 50Hz 和 60Hz 抑制

• 单周期稳定转换

• 双传感器激励电流源

• 内部故障监测器

• 内部 ADC 测试信号

• 8 个通用输入/输出

2 应用

• 工厂自动化和控制:

– 模拟输入模块

– 温度控制器

– 称重模块

• 仪表:

– 过程分析

– 实验室和现场仪表

– 称重秤

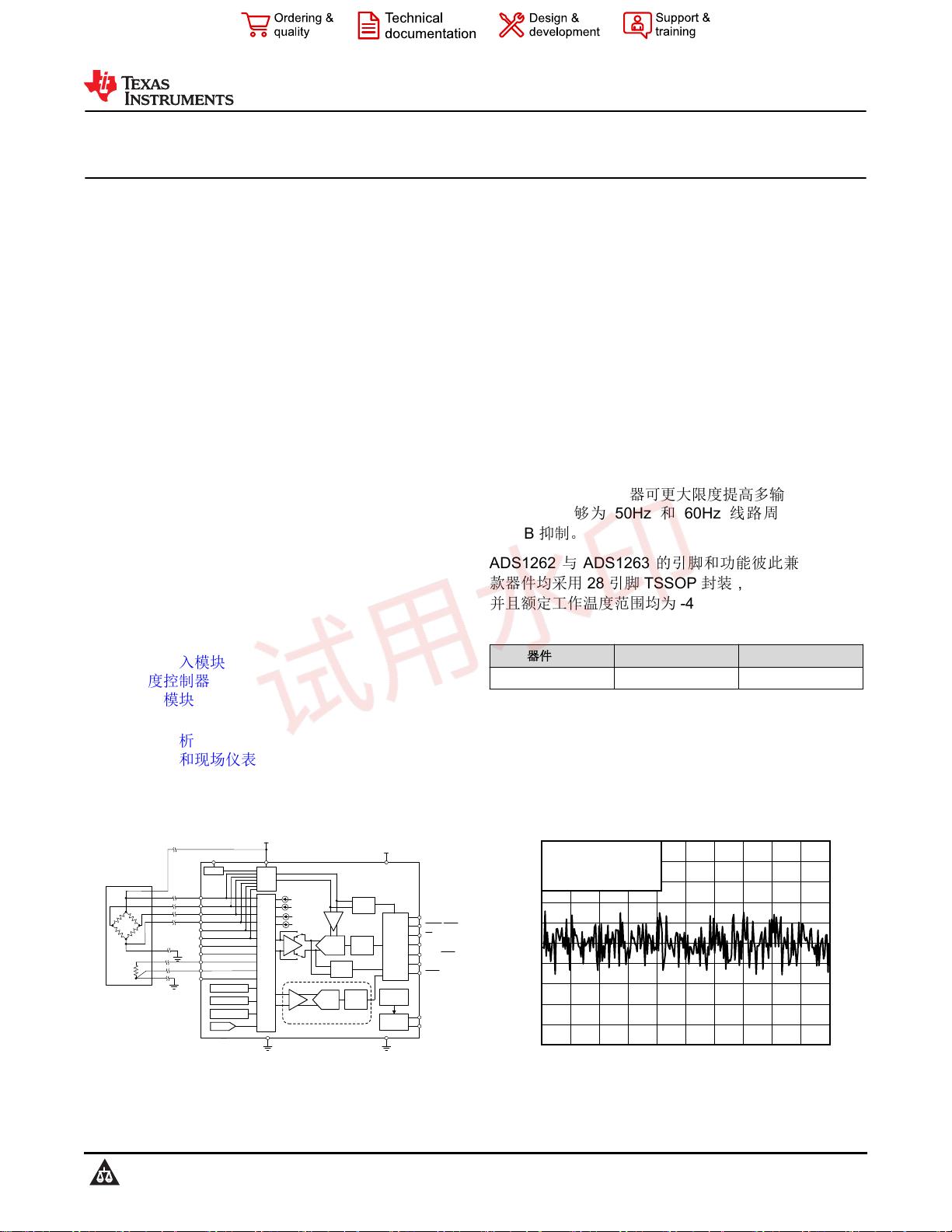

3 说明

ADS1262 和 ADS1263 (ADS126x) 是具有集成 PGA、

电压基准和内部故障监视器的低噪声、低漂移、

38.4kSPS、Δ-Σ ADC。ADS1263 集成了一个 24 位

辅助 Δ-Σ ADC,适用于后台测量。这种支持传感器的

ADC 提供了一套完备的高精度、单芯片测量解决方

案,可满足要求极为严苛的传感器应用需求,其中包括

称重秤、应变计传感器、热电偶和电阻式温度器件

(RTD)。

ADC 由低噪声 CMOS PGA(增益范围为 1 至 32)、

Δ-Σ 调制器以及可编程数字滤波器组成。模拟前端

(AFE) 非常灵活,其包含两个传感器激励电流源,非常

适合直接进行 RTD 测量。

单周期稳定数字滤波器可更大限度提高多输入转换吞吐

量,同时能够为 50Hz 和 60Hz 线路周期干扰提供

130dB 抑制。

ADS1262 与 ADS1263 的引脚和功能彼此兼容。这两

款器件均采用 28 引脚 TSSOP 封装,

并且额定工作温度范围均为 -40°C 至 +125°C。

器件信息

(1)

器件型号 封装

封装尺寸(标称值)

ADS126x TSSOP (28) 9.70mm x 4.40mm

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

PGA

+3.3 V

Bridge

Pt 100

PGA

Sensor Test

+Sen

Sen±

+Sig

Sig±

Exc±

+Exc

AVDD

AVSS

DIN

RESET/PWDN

ADCû

24-Bit

Oscillator

Internal

Test V

Excitation

Dual Sensor

Filter

Digital

ADS1263 Only

AIN9

AIN8

AIN7

AIN6

AIN5

AIN4

AIN3

2.5-V Ref

Mux

Ref

DGND

DVDD

+5 V

ADS1263

ADS1262

Temp Sensor

Level Shift

GPIO

AINCOM

AIN2

AIN1

AIN0

Buf

Alarm

Signal

Alarm

Ref

REFOUT

XTAL1/CLKIN

XTAL2

Mux

Clock

START

DRDY

SCLK

DOUT/DRDY

CS

Control

and

Interface

Serial

Filter

Digital

Mux

Input

PGA

ADCû

32-Bit

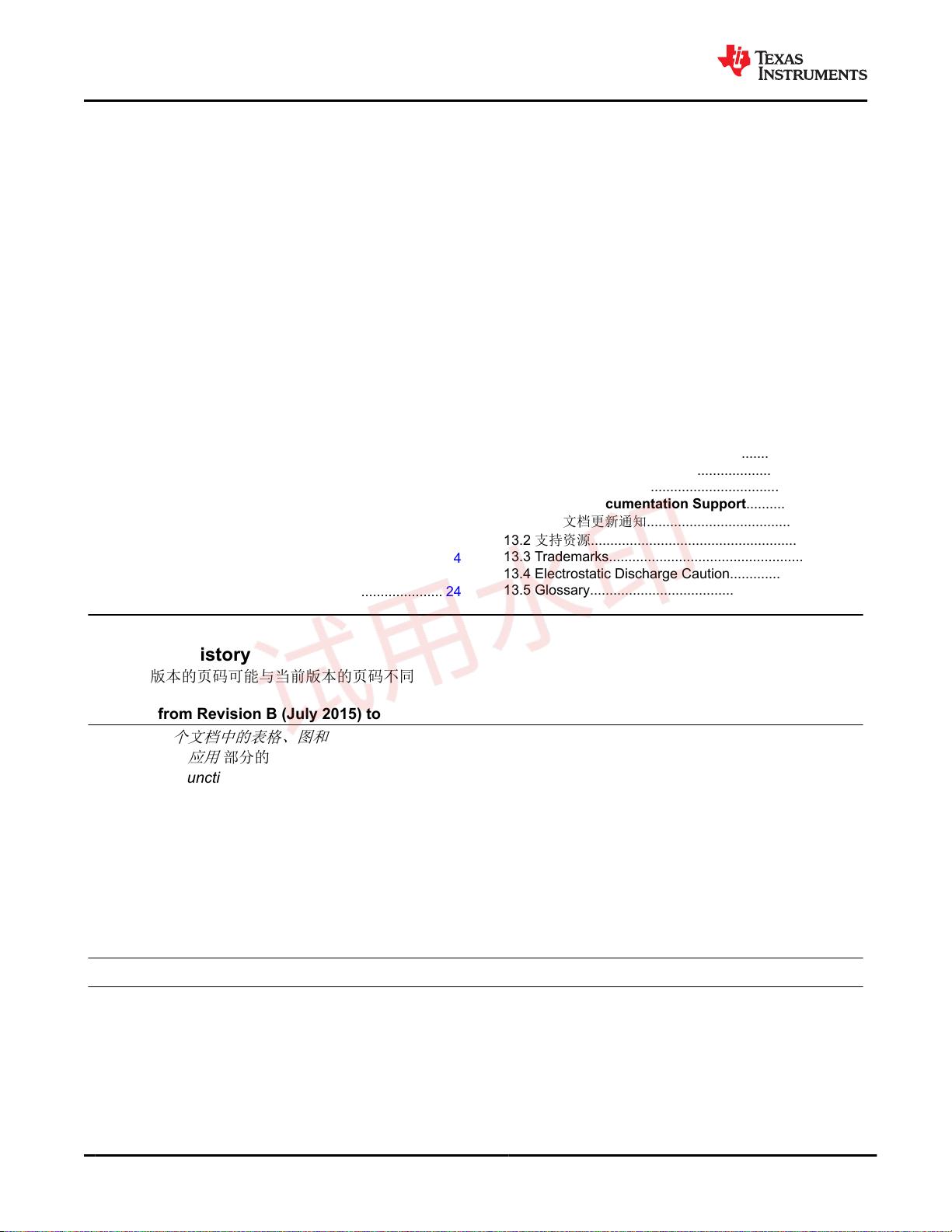

温度补偿电桥测量

P-P

VPNoise = 0.16

Data Rate = 20 SPS

78 mVrInput Range =

D017

0.25

0.2

0.15

0.1

0.05

0

-0.05

-0.1

-0.15

-0.2

-0.25

9 10876543210

V)PADC Output (

Time (s)

ADC 转换噪声

ADS1262, ADS1263

ZHCSDN4C – FEBRUARY 2015 – REVISED MAY 2021

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。有关适用的官方英文版本的最新信息,请访问

www.ti.com,其内容始终优先。TI 不保证翻译的准确性和有效性。在实际设计之前,请务必参考最新版本的英文版本。

English Data Sheet: SBAS661

Table of Contents

1 特性................................................................................... 1

2 应用................................................................................... 1

3 说明................................................................................... 1

4 Revision History.............................................................. 2

5 Device Comparison......................................................... 4

6 Pin Configuration and Functions...................................4

7 Specifications.................................................................. 5

7.1 Absolute Maximum Ratings........................................ 5

7.2 ESD Ratings............................................................... 5

7.3 Recommended Operating Conditions.........................6

7.4 Thermal Information....................................................6

7.5 Electrical Characteristics.............................................7

7.6 Timing Requirements: Serial Interface......................10

7.7 Switching Characteristics: Serial Interface................10

7.8 Timing Diagrams....................................................... 10

7.9 Typical Characteristics.............................................. 12

8 Parameter Measurement Information.......................... 23

8.1 Offset Temperature Drift Measurement.....................23

8.2 Gain Temperature Drift Measurement.......................23

8.3 Common-Mode Rejection Ratio Measurement.........23

8.4 Power-Supply Rejection Ratio Measurement........... 24

8.5 Crosstalk Measurement (ADS1263)......................... 24

8.6 Reference-Voltage Temperature-Drift

Measurement.............................................................. 24

8.7 Reference-Voltage Thermal-Hysteresis

Measurement.............................................................. 24

8.8 Noise Performance................................................... 25

9 Detailed Description......................................................30

9.1 Overview................................................................... 30

9.2 Functional Block Diagram......................................... 31

9.3 Feature Description...................................................32

9.4 Device Functional Modes..........................................62

9.5 Programming............................................................ 86

9.6 Register Maps...........................................................89

10 Application and Implementation.............................. 107

10.1 Application Information......................................... 108

10.2 Typical Application................................................ 115

10.3 What To Do and What Not To Do..........................120

10.4 Initialization Setup.................................................121

11 Power Supply Recommendations............................123

11.1 Power-Supply Decoupling.....................................123

11.2 Analog Power-Supply Clamp................................ 124

11.3 Power-Supply Sequencing....................................124

12 Layout.........................................................................124

12.1 Layout Guidelines................................................. 124

12.2 Layout Example.................................................... 126

13 Device and Documentation Support........................127

13.1 接收文档更新通知................................................. 127

13.2 支持资源................................................................127

13.3 Trademarks........................................................... 127

13.4 Electrostatic Discharge Caution............................127

13.5 Glossary................................................................127

4 Revision History

注:以前版本的页码可能与当前版本的页码不同

Changes from Revision B (July 2015) to Revision C (May 2021) Page

•

更新了整个文档中的表格、图和交叉参考的编号格式

........................................................................................ 1

• 添加了指向

应用

部分的链接................................................................................................................................1

• Changed Functional Block Diagram to correct XTAL1/CLKIN pin name.......................................................... 31

• Added discussion to Internal Reference section regarding 10 μF (max) REFOUT capacitor ability to

decrease reference noise................................................................................................................................. 42

• Changed IDAC Block Diagram and text to include 2500 μA setting............................................................... 50

• Added last paragraph to Pulse Conversion Mode section to explain operation in chop mode.........................63

• Changed EBh to AFh in the example checksum computation in the Checksum Mode section....................... 73

• Changed text in GPIO Data Register section regarding GPIO data read when programmed as an output... 104

• Changed calculation of V

REFMIN

to use gain = 8 in Detailed Design Procedure application section...............116

• Changed title of What To Do and What Not To Do from Do's and Don'ts ......................................................120

Changes from Revision A (May 2015) to Revision B (July 2015) Page

• 将 ADS1263 从产品预发布更改为量产数据,并在整个数据表中添加了 ADS1263 和 ADC2 的文本和规格.......1

• 更改了整个数据表中的文本,使之更加清晰....................................................................................................... 1

• Added condition line to Absolute Maximum Ratings table..................................................................................5

• Added Crosstalk section to Electrical Characteristics table................................................................................7

• Added 图 7-32 ..................................................................................................................................................12

• Added 图 7-36 ..................................................................................................................................................12

• Changed legend in 图 7-45 ..............................................................................................................................12

ADS1262, ADS1263

ZHCSDN4C – FEBRUARY 2015 – REVISED MAY 2021

www.ti.com.cn

2 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: ADS1262 ADS1263

• Added missing gain term in FSR definition of 方程式 8 ................................................................................... 25

• Changed text in fourth paragraph of Noise Performance section to clarify conditions to achieve maximum

ENOB................................................................................................................................................................25

• Changed bit names from PGAH and PGAL to PGAH_ALM and PGAL_ALM, respectively, in PGA Absolute

Output-Voltage Monitor section........................................................................................................................ 40

• Changed 图 9-12 to show correct name of bit 4............................................................................................... 41

• Changed RMUX to RMUXP in second paragraph of ADC Reference Voltage section.................................... 41

• Changed text in last paragraph of ADC Reference Voltage section to show correct name of bit 4..................41

• Changed text in External Reference section to clarify external reference inputs, polarity reversal switch,

reference input current, and external reference buffer..................................................................................... 42

• Changed text in Power-Supply Reference section to clarify use of power-supply reference in critical

applications.......................................................................................................................................................42

• Added ADC1 Modulator section....................................................................................................................... 42

• Changed text in last paragraph of Sensor-Excitation Current Sources (IDAC1 and IDAC2) section to clarify

settling time in IDAC rotation mode.................................................................................................................. 50

• Changed text in General-Purpose Input/Output (GPIO) section regarding GPIO data readback when

programmed as an output.................................................................................................................................53

• Changed 图 9-27 ............................................................................................................................................. 53

• Changed TSIGP and TSIGN to TDACP and TDACN, respectively, in the last paragraph of the Test DAC

(TDAC) section................................................................................................................................................. 54

• Changed text in Test DAC (TDAC) section allowing for any common-mode value instead of 0 V................... 54

• Added note (1) to 图 9-30 ................................................................................................................................ 58

• Changed t

h(DRSP)

value of 16 from max to min................................................................................................. 62

• Added stop-start sequence text to restart conversions in Continuous Conversion Mode section.................... 62

• Deleted software polling text from Data Ready ( DRDY) section..................................................................... 68

• Added Conversion Data Software Polling section............................................................................................ 68

• Added text to clarify data reset at conversion restart........................................................................................69

• Added text to Read Data Direct (ADC1) section to clarify conversion restart...................................................69

• Changed 图 9-43 to show complete list of CRC bit settings............................................................................. 69

• Changed text in Read Data by Command section to clarify software polling................................................... 70

• Changed 图 9-44 to show complete list of CRC bit settings............................................................................. 70

• Added text to Offset Calibration Registers section regarding offset calibration disabled in chop mode...........77

• Added new step 1 to Calibration Command Procedure section....................................................................... 80

• Added text to WREG Command section regarding conversion restart.............................................................88

• Changed text in 2nd paragraph of Register Map section................................................................................. 89

• Changed Group Update column of 表 9-34 ..................................................................................................... 89

• Added software polling to 图 10-16 ................................................................................................................121

www.ti.com.cn

ADS1262, ADS1263

ZHCSDN4C – FEBRUARY 2015 – REVISED MAY 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

3

Product Folder Links: ADS1262 ADS1263

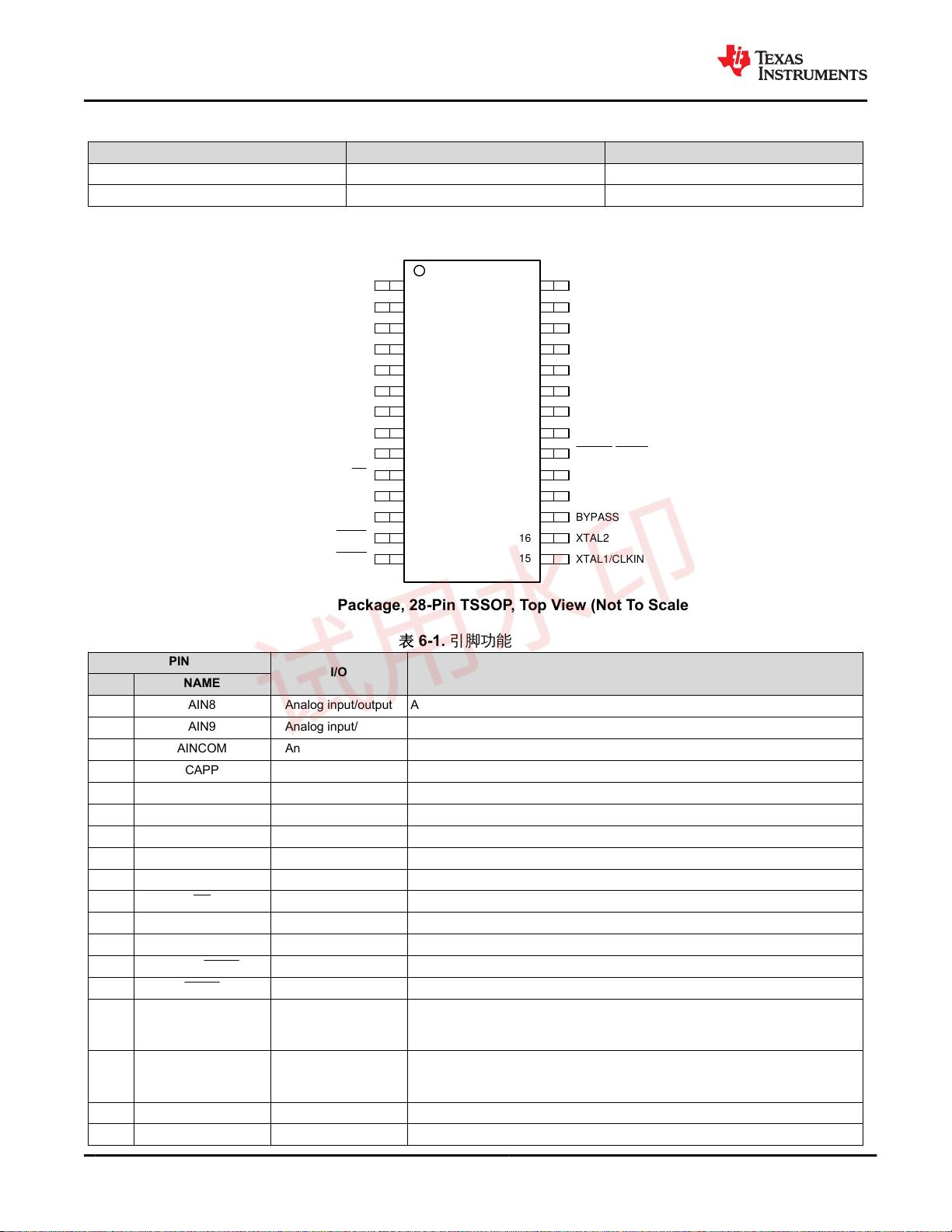

5 设备比较

产品 输入

辅助24-BIT ADC

ADS1262 11 No

ADS1263 11 Yes

6 引脚配置和功能

15

16

17

18

19

20

21

22

23

24

25

26

27

28

14

13

12

11

10

9

8

7

6

5

4

3

2

1

XTAL2

XTAL1/CLKIN

BYPASS

DGND

DVDD

RESET/PWDN

AIN0

AIN1

AIN2

AIN3

DRDY

DOUT/DRDY

DIN

SCLK

CS

START

REFOUT

AVSS

AVDD

CAPN

AIN4

AIN5

AIN6

AIN7

CAPP

AINCOM

AIN9

AIN8

图 6-1. PW Package, 28-Pin TSSOP, Top View (Not To Scale)

表 6-1. 引脚功能

PIN

I/O

说明

NO. NAME

1 AIN8 Analog input/output Analog input 8, IDAC1, IDAC2, GPIO5

2 AIN9 Analog input/output Analog input 9, IDAC1, IDAC2, GPIO6

3 AINCOM Analog input/output Analog input common, IDAC1, IDAC2, GPIO7, VBIAS

4 CAPP Analog output PGA output P: connect a 4.7-nF C0G dielectric capacitor from CAPP to CAPN

5 CAPN Analog output PGA output N: connect a 4.7-nF C0G dielectric capacitor from CAPP to CAPN

6 AVDD Analog Positive analog power supply

7 AVSS Analog Negative analog power supply

8 REFOUT Analog Output Internal reference voltage output, connect 1-µF capacitor to AVSS

9 START Digital Input Start conversion control

10 CS Digital Input Serial interface chip select (active low)

11 SCLK Digital Input Serial interface shift clock

12 DIN Digital Input Serial interface data input

13 DOUT/DRDY Digital output Serial interface data output and data ready indicator (active low)

14 DRDY Digital output Data ready indicator (active low)

15 XTAL1/CLKIN Digital Input

1) Internal oscillator: Connect to DGND

2) External clock: Connect clock input

3) Crystal oscillator: Connect to crystal and crystal load capacitor

16 XTAL2 Digital Input

1) Internal oscillator: No connection (float)

2) External clock: No connection (float)

3) Crystal oscillator: Connect to crystal and crystal load capacitor

17 BYPASS Analog Output 2-V sub-regulator external bypass; connect 1-µF capacitor to DGND

18 DGND Digital Digital ground

ADS1262, ADS1263

ZHCSDN4C – FEBRUARY 2015 – REVISED MAY 2021

www.ti.com.cn

4 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: ADS1262 ADS1263

表 6-1. Pin Functions (continued)

PIN

I/O

说明

NO. NAME

19 DVDD Digital Digital power supply

20 RESET/PWDN Digital input Reset (active low); hold low to power down the ADC

21 AIN0 Analog input/output Analog input 0, REFP1, IDAC1, IDAC2

22 AIN1 Analog input/output Analog input 1, REFN1, IDAC1, IDAC2

23 AIN2 Analog input/output Analog input 2 ,REFP2, IDAC1, IDAC2

24 AIN3 Analog input/output Analog input 3, REFN2, IDAC1, IDAC2, GPIO0

25 AIN4 Analog input/output Analog input 4, REFP3, IDAC1, IDAC2, GPIO1

26 AIN5 Analog input/output Analog input 5, REFN3, IDAC1, IDAC2, GPIO2

27 AIN6 Analog input/output Analog input 6, IDAC1, IDAC2, GPIO3, TDACP

28 AIN7 Analog input/output Analog input 7, IDAC1, IDAC2, GPIO4, TDACN

7 规格

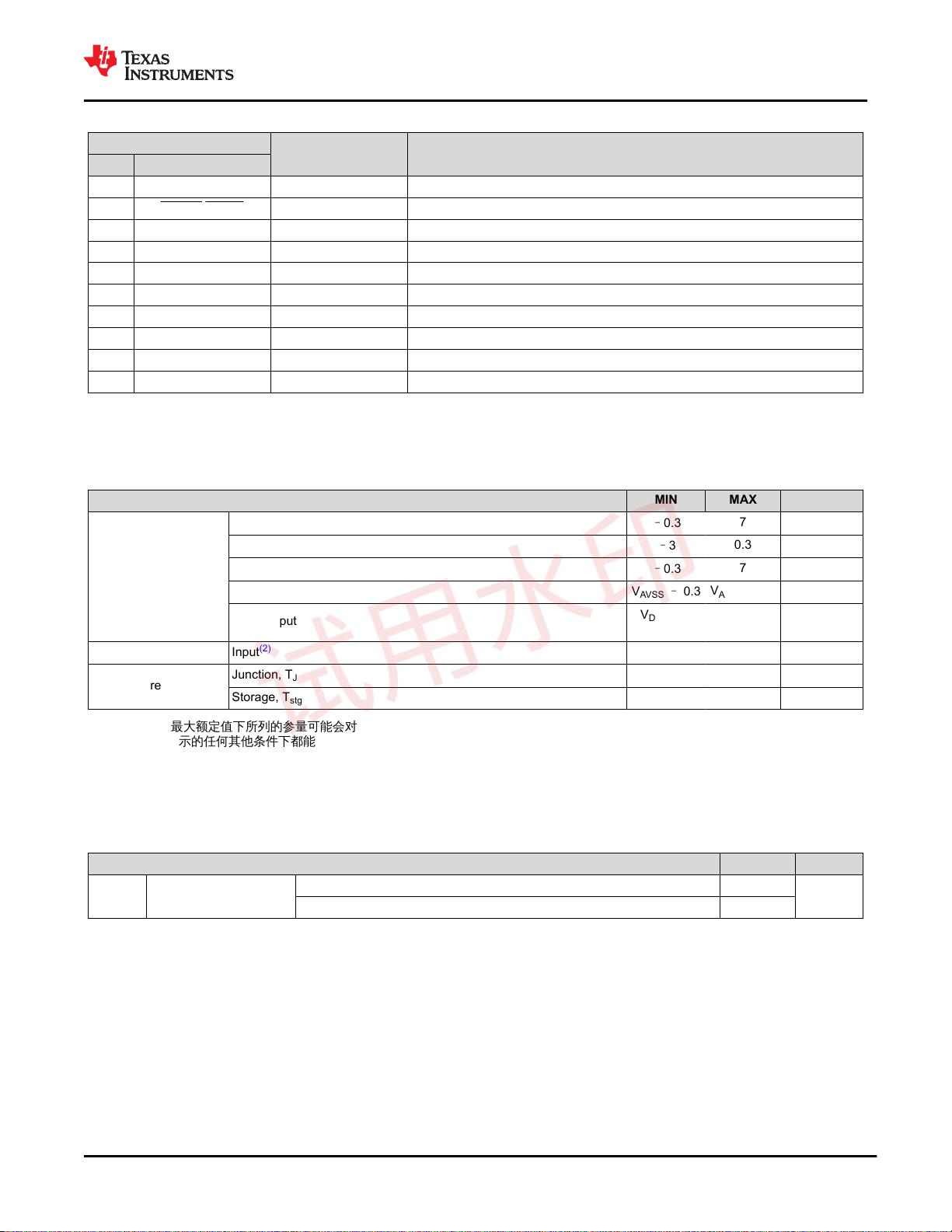

7.1 绝对最大额定值

工作在自由空气温度范围内(除非另有说明)

(1)

MIN MAX UNIT

Voltage

AVDD to AVSS

–0.3

7 V

AVSS to DGND

–3

0.3 V

DVDD to DGND

–0.3

7 V

Analog input

V

AVSS

– 0.3

V

AVDD

+ 0.3 V

Digital input

V

DGND

–

0.3

V

DVDD

+ 0.3 V

Current Input

(2)

–10

10 mA

Temperature

Junction, T

J

–50

150 °C

Storage, T

stg

-60 150 °C

(1)

(2)

输入引脚与电源轨采用二极管钳位连接。如果模拟输入电压超过 VAVDD + 0.3 V 或低于 VAVSS- 0.3 V,或者数字输入电压超过

VDVDD + 0.3 V 或低于 VDGND- 0.3 V,则将输入电流限制在 10 mA

超过绝对最大额定值下所列的参量可能会对设备造成永久性损坏。这些仅是参量额定值,并不意味着设备在这些条件下或超出 "建议工作

条件 "下所示的任何其他条件下都能正常工作。长期暴露在绝对最大额定条件下可能会影响器件的可靠性。

或以下。

7.2 ESD 额定值

VALUE UNIT

V

(ESD)

静电放电

人体模型 (HBM),符合 ANSI/ESDA/JEDEC JS-001 标准

(1)

±2000

V

带电器件模型 (CDM),符合 JEDEC 规范 JESD22-C101

(2)

±500

(1)

(2)

JEDEC 文件 JEP155 指出,500-V HBM 允许使用标准 ESD 控制流程进行安全制造.

JEDEC 文件 JEP157 指出,250-V CDM 允许使用标准 ESD 控制流程进行安全制造.

www.ti.com.cn

ADS1262, ADS1263

ZHCSDN4C – FEBRUARY 2015 – REVISED MAY 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

5

Product Folder Links: ADS1262 ADS1263

剩余135页未读,继续阅读

资源评论

yangzhibin68

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功