Devicetree Specification

Release v0.3

devicetree.org

13 February 2020

CONTENTS

1 Introduction 3

1.1 Purpose and Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.2 Relationship to IEEE™ 1275 and ePAPR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.3 32-bit and 64-bit Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.4 Definition of Terms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 The Devicetree 6

2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2 Devicetree Structure and Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2.1 Node Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2.2 Generic Names Recommendation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.2.3 Path Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.2.4 Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3 Standard Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3.1 compatible . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3.2 model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3.3 phandle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3.4 status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3.5 #address-cells and #size-cells . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3.6 reg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.7 virtual-reg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.8 ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.9 dma-ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3.10 name (deprecated) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3.11 device_type (deprecated) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.4 Interrupts and Interrupt Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.4.1 Properties for Interrupt Generating Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.4.2 Properties for Interrupt Controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.4.3 Interrupt Nexus Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.4.4 Interrupt Mapping Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.5 Nexus Nodes and Specifier Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.5.1 Nexus Node Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.5.2 Specifier Mapping Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3 Device Node Requirements 26

3.1 Base Device Node Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.2 Root node . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.3 /aliases node . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.4 /memory node . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.5 /chosen Node . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.6 /cpus Node Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.7 /cpus/cpu

*

Node Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.7.1 General Properties of /cpus/cpu

*

nodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.7.2 TLB Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

i

3.7.3 Internal (L1) Cache Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.7.4 Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.8 Multi-level and Shared Cache Nodes (/cpus/cpu

*

/l?-cache) . . . . . . . . . . . . . . . . . . . . 36

3.8.1 Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4 Device Bindings 38

4.1 Binding Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.1.1 General Principles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.1.2 Miscellaneous Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2 Serial devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.2.1 Serial Class Binding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.2.2 National Semiconductor 16450/16550 Compatible UART Requirements . . . . . . . . . . . . . 40

4.3 Network devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.3.1 Network Class Binding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.3.2 Ethernet specific considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.4 Power ISA Open PIC Interrupt Controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4.5 simple-bus Compatible Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5 Flattened Devicetree (DTB) Format 44

5.1 Versioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.2 Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.3 Memory Reservation Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.3.1 Purpose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.3.2 Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.4 Structure Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.4.1 Lexical structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.4.2 Tree structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

5.5 Strings Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.6 Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6 Devicetree Source (DTS) Format (version 1) 50

6.1 Compiler directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.2 Labels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.3 Node and property definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.4 File layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Bibliography 54

Index 56

ii

Devicetree Specification, Release v0.3

Copyright

Copyright 2008,2011 Power.org, Inc.

Copyright 2008,2011 Freescale Semiconductor, Inc.

Copyright 2008,2011 International Business Machines Corporation.

Copyright 2016,2017 Linaro, Ltd.

Copyright 2016,2017 Arm, Ltd.

The Linaro and devicetree.org word marks and the Linaro and devicetree.org logos and related marks are trademarks and

service marks licensed by Linaro Ltd. Implementation of certain elements of this document may require licenses under

third party intellectual property rights, including without limitation, patent rights. Linaro and its Members are not, and

shall not be held, responsible in any manner for identifying or failing to identify any or all such third party intellectual

property rights.

The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks

and service marks licensed by Power.org. Implementation of certain elements of this document may require licenses under

third party intellectual property rights, including without limitation, patent rights. Power.org and its Members are not, and

shall not be held, responsible in any manner for identifying or failing to identify any or all such third party intellectual

property rights.

THIS SPECIFICATION PROVIDED “AS IS” AND WITHOUT ANY WARRANTY OF ANY KIND, INCLUD-

ING, WITHOUT LIMITATION, ANY EXPRESS OR IMPLIED WARRANTY OF NON-INFRINGEMENT, MER-

CHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL LINARO OR ANY MEM-

BER OF LINARO BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, EXEMPLARY, PUNITIVE, OR CON-

SEQUENTIAL DAMAGES, INCLUDING, WITHOUT LIMITATION, LOST PROFITS, EVEN IF ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES.

Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

Linaro, Ltd

Harston Mill,

Royston Road,

Harston CB22 7GG

Attn: Devicetree.org Board Secretary

License Information

Licensed under the Apache License, Version 2.0 (the “License”); you may not use this file except in compliance with the

License. You may obtain a copy of the License at

http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an “AS

IS” BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License

for the specific language governing permissions and limitations under the License.

CONTENTS 1

Devicetree Specification, Release v0.3

Acknowledgements

The devicetree.org Technical Steering Committee would like to thank the many individuals and companies that contributed

to the development of this specification through writing, technical discussions and reviews.

We want to thank the power.org Platform Architecture Technical Subcommittee who developed and published ePAPR.

The text of ePAPR was used as the starting point for this document.

Significant aspects of the Devicetree Specification are based on work done by the Open Firmware Working Group which

developed bindings for IEEE-1275. We would like to acknowledge their contributions.

We would also like to acknowledge the contribution of the PowerPC and ARM Linux communities that developed and

implemented the flattened devicetree concept.

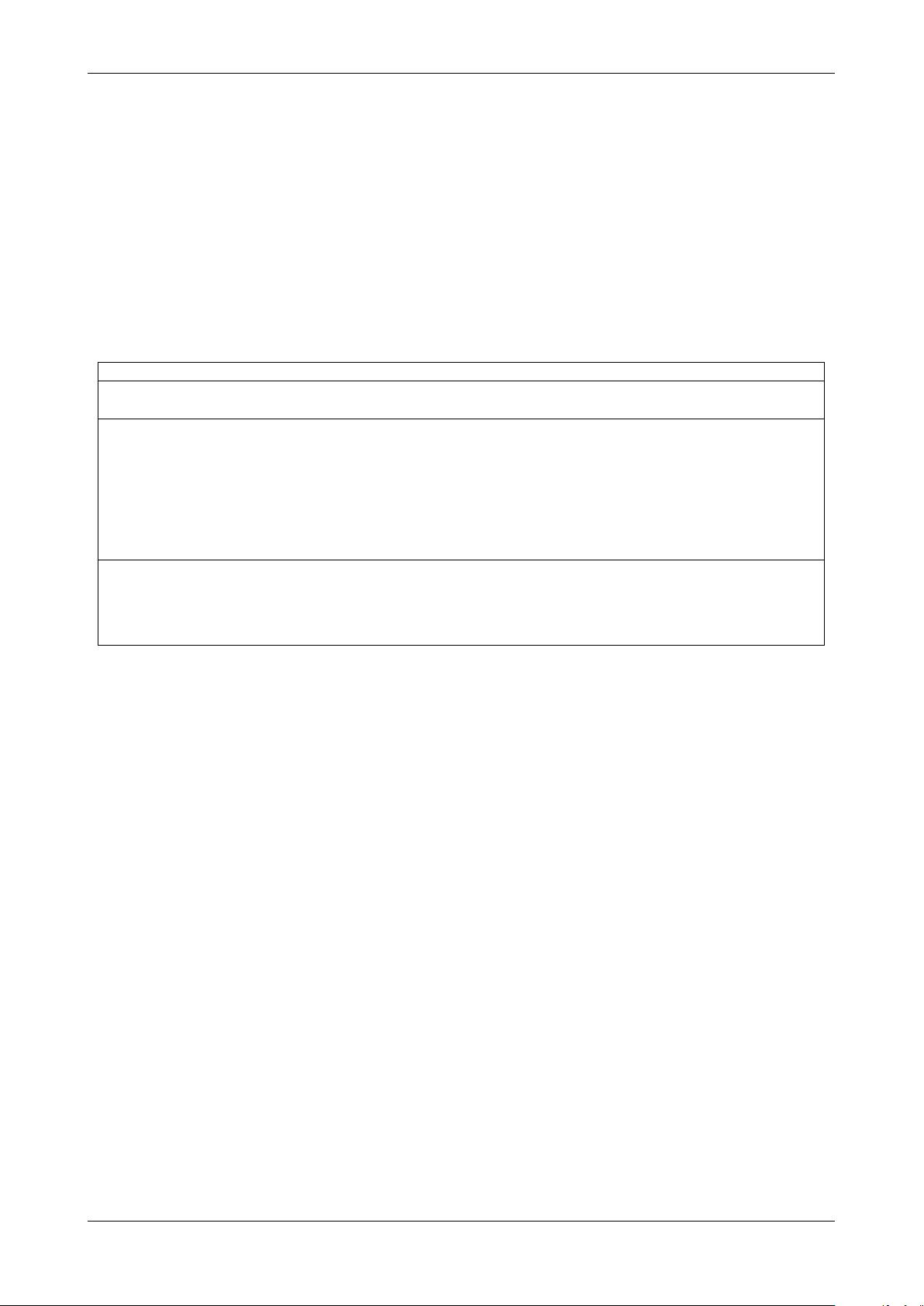

Table 1: Revision History

Revision Date Description

0.1 2016-MAY-24 Initial prerelease version. Imported ePAPR text into reStructured Text format and

removed Power ISA specific elements.

0.2 2017-DEC-20

• Added more recommended generic node names

• Added interrupts-extended

• Additional phy times

• Filled out detail in source language chapter

• Editorial changes

• Added changebar version to release documents

0.3 2020-FEB-13

• Added more recommended generic node names

• Document generic nexus binding

• codespell support and spelling fixes

CONTENTS 2

评论0