没有合适的资源?快使用搜索试试~ 我知道了~

LD3320语音控制器

温馨提示

试读

24页

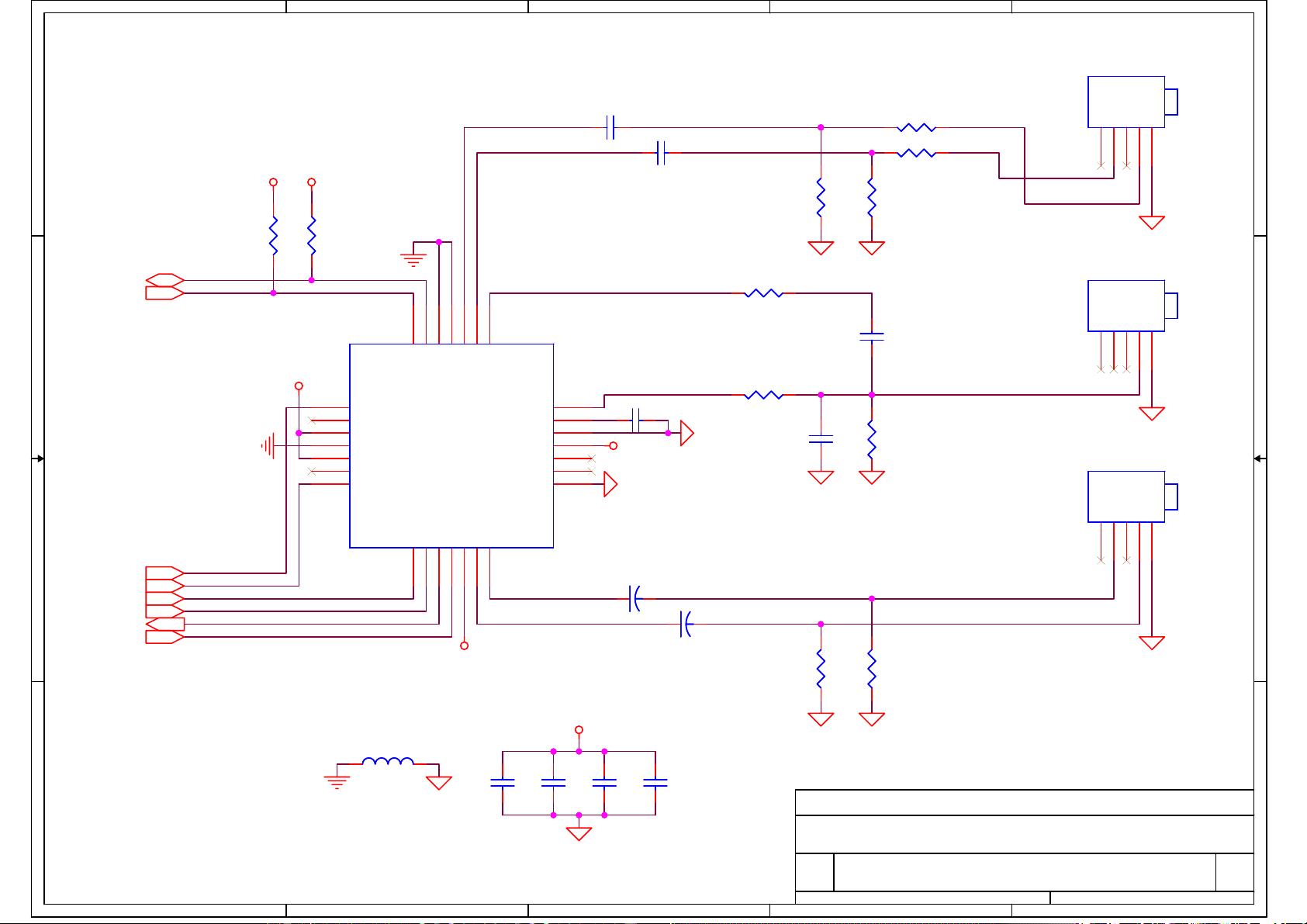

主要是基于STC89L08的单片机来控制LD3220的语音控制方案,具体程序可以向我所取。

资源推荐

资源详情

资源评论

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet

of

COVER PAGE 2.0

ALTERA DE2

B

124Sunday, July 23, 2006

Title

Size Document Number Rev

Date: Sheet

of

COVER PAGE 2.0

ALTERA DE2

B

124Sunday, July 23, 2006

Title

Size Document Number Rev

Date: Sheet

of

COVER PAGE 2.0

ALTERA DE2

B

124Sunday, July 23, 2006

13 ~ 17

TOP 01 ~ 03

04 ~ 04

20 ~ 20

PAGE

05 ~ 06

12 ~ 12

SCHEMATIC

TERASIC CYCLONE II EP2C35 Development & Education BOARD

18 ~ 19

CONTENT

COVER PAGE , TOP

AUDIO WM8731

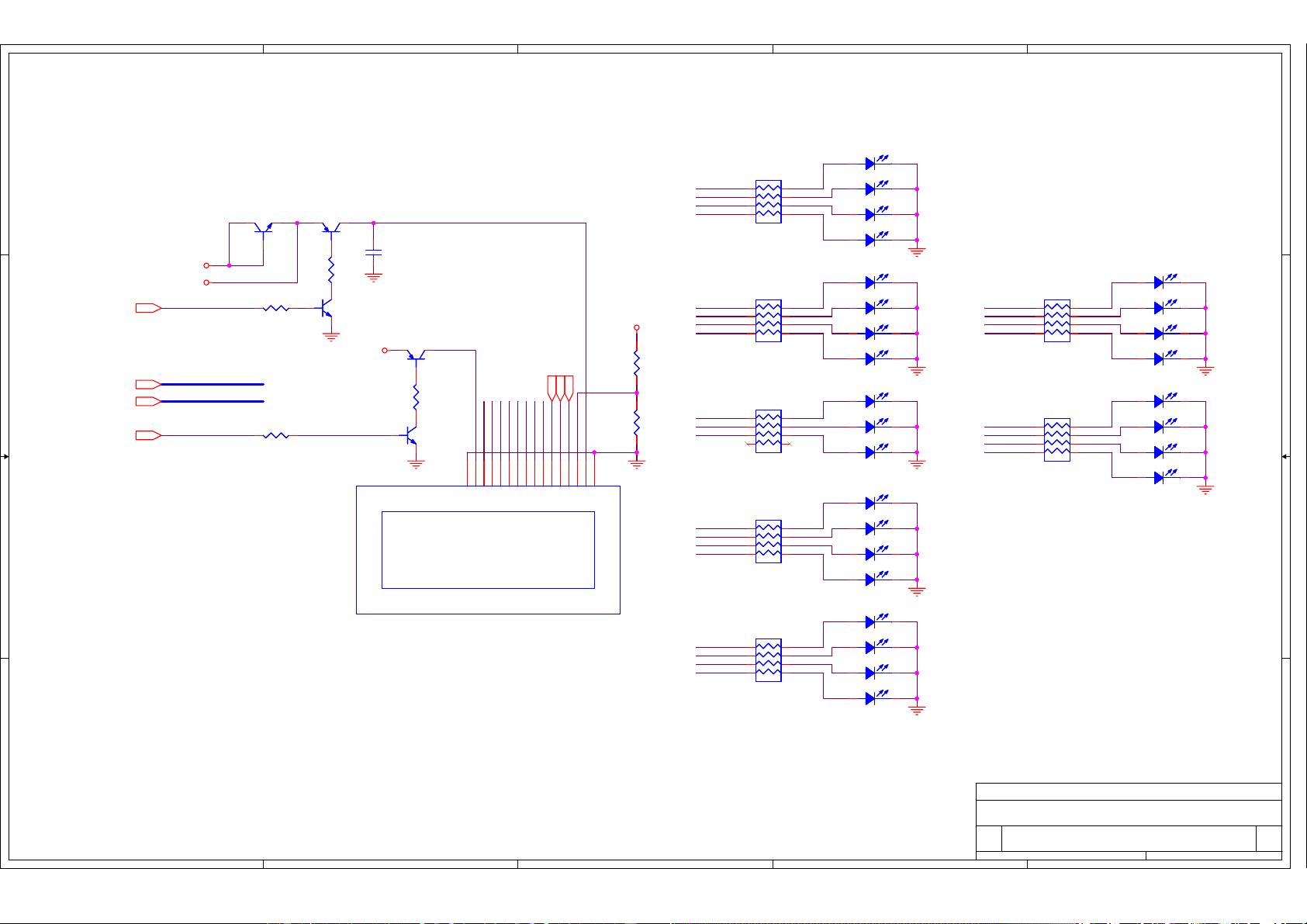

DISPLAY LCD , LED , 7SEGMENT

EP2C35 EP2C35 BANK1..BANK8 , POWER , CONFIG 07 ~ 11

ETHERNET DM9000A

IN/OUT CLOCK , PS2 , RS232 , KEY , SWITCH , CONNECT

MEMORY SRAM , DRAM , FLASH , SD CARD

POWER POWER

USB BLASTER USB BLASTER 21 ~ 21

22 ~ 22

23 ~ 24

USB DEVICE USB DEVICE

VIDEO ADV7181 , ADV7123

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet

of

PLACEMENT 2.0

ALTERA DE2

B

224Sunday, July 23, 2006

Title

Size Document Number Rev

Date: Sheet

of

PLACEMENT 2.0

ALTERA DE2

B

224Sunday, July 23, 2006

Title

Size Document Number Rev

Date: Sheet

of

PLACEMENT 2.0

ALTERA DE2

B

224Sunday, July 23, 2006

SW0

SW1

SW2

SW3

SW4

SW5

SW6

SW7

SW8

SW9

SW10

SW11

SW12

SW13

SW14

SW15

SW16

SW17

USB

BLASTER

ISP1362

USB

DEVICE

USB

HOST

FT245

LCD MODULE

LINE

IN

LINE

OUT

MIC

IN

WM8731

TV

DECODER

VGA

OUTPUT

RJ45 PS2

KEYBORAD

RS232DC

9V

SD CARD

ADV7181 ADV7123 DM9000A

M3128

EPCS16

EP2C35

FLASHSRAMSDRAM

GPIO_1

GPIO_0

LEDR0

LEDR1

LEDR2

LEDR3

LEDR4

LEDR5

LEDR6

LEDR7

LEDR8

LEDR9

LEDR10

LEDR11

LEDR12

LEDR13

LEDR14

LEDR15

LEDR16

LEDR17

KEY0

KEY1

KEY2

KEY3

HEX0

HEX1

HEX2

HEX3

HEX4

HEX5

HEX6

HEX7

LEDG0

LEDG1

LEDG2

LEDG3

LEDG4

LEDG5

LEDG6

LEDG7

LEDR8

IrDA

EXT CLK

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

AUD_BCLK

AUD_DACDAT

AUD_DACLRCK

LED[5..26]

AUD_ADCLRCK

I2C_SCLK

AUD_XCK

UART_TXD

PS2_CLK

LED[0..4]

IRDA_TXD

ENET_CMD

ENET_IOR

ENET_CS

ENET_IOW

ENET_INT

ENET_D[0..15]

25MHZ

ENET_RESET

AUD_BCLK

AUD_DACDAT

AUD_ADCLRCK

AUD_DACLRCK

I2C_SCLK

AUD_XCK

AUD_ADCDAT

I2C_SDAT

HEX0_D[0..6]

HEX1_D[0..6]

HEX2_D[0..6]

HEX3_D[0..6]

HEX4_D[0..6]

HEX5_D[0..6]

HEX6_D[0..6]

HEX7_D[0..6]

LCD_D[0..7]

LCD_BLON

LCD_ON

LCD_WR

LCD_EN

LCD_RS

LED[0..26]

PS2_DAT

KEY[0..3]

GPIO_B[0..71]

SW[0..17]

IRDA_RXDIRDA_TXD

EXT_CLOCK

50MHZ

PS2_CLK

UART_TXD UART_RXD

FLASH_A[0..21]

DRAM_CLK

DRAM_CKE

DRAM_BA0

DRAM_BA1

SD_DAT

DRAM_WE

DRAM_CAS

DRAM_RAS

DRAM_CS

SRAM_A[0..17]

SD_DAT3

SD_CMD

SD_CLK

FLASH_CE

FLASH_OE

DRAM_D[0..15]

DRAM_LDQM

DRAM_UDQM

NCSO

ASDO

DCLK

TDI

TMS

TCK

NCONFIG

NCE

CONF_DONE

NSTATUS

LINK_D0

LINK_D1

LINK_D2

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_WE

OTG_OE

OTG_RESET

OTG_DACK0

OTG_DACK1

OTG_CS

OTG_A1

OTG_A0

DATA0

TDO

LINK_D3

12MHZ

12MHZ

OTG_LSPEED

OTG_FSPEED

OTG_D[0..15]

SRAM_D[0..15]

DRAM_A[0..11]

SRAM_WE

SRAM_CE

SRAM_OE

SRAM_UB

SRAM_LB

FLASH_D[0..7]

FLASH_RESET

FLASH_WE

TD_D[0..7]

TD_HS

27MHz

TD_VS

TD_RESET

I2C_SDATI2C_SCLK

VGA_BLANK

VGA_SYNC

VGA_CLOCK

VGA_HS

VGA_VS

VGA_R[0..9]

VGA_G[0..9]

VGA_B[0..9]

FLASH_D[0..7]

50MHZ

UART_RXD

PS2_DAT

SW[0..2]

EXT_CLOCK

SW[3..5]

SW[6..9]

KEY[0..3]

GPIO_B[0..71]

SW[10..17]

IRDA_RXD

FLASH_CE

FLASH_OE

FLASH_RESET

FLASH_WE

FLASH_A[0..21]

AUD_ADCDAT

I2C_SDAT

ENET_CMD

ENET_RESET

25MHZ

ENET_CS

ENET_IOR

ENET_IOW

ENET_INT

ENET_D[0..15]

HEX6_D[0..6]

HEX4_D[0..6]

HEX5_D[0..6]

HEX7_D[0..6]

LCD_EN

LCD_WR

LCD_ON

LCD_BLON

LCD_RS

LCD_D[0..7]

HEX3_D[0..6]

HEX2_D[0..6]

HEX1_D[0..6]

HEX0_D[0..6]

SRAM_CE

SRAM_WE

SRAM_OE

SRAM_UB

SRAM_LB

SRAM_A[0..17]

DRAM_CS

DRAM_BA1

DRAM_CAS

DRAM_CLK

DRAM_A[0..11]

DRAM_LDQM

DRAM_UDQM

DRAM_BA0

DRAM_RAS

DRAM_CKE

DRAM_WE

DRAM_D[0..15]

SRAM_D[0..15]

SD_CLK

SD_CMD

SD_DAT3

SD_DAT

NCONFIG

TMS

TDI

CONF_DONE

NSTATUS

NCE

TCK

ASDO

DCLK

NCSO

TDO

DATA0

LINK_D3

LINK_D0

LINK_D1

LINK_D2

VGA_CLOCK

VGA_BLANK

VGA_SYNC

VGA_VS

VGA_HS

TD_RESET

VGA_B[0..9]

VGA_R[0..9]

VGA_G[0..9]

OTG_DACK1

OTG_DACK0

OTG_DREQ1

OTG_INT1

OTG_INT0

OTG_DREQ0

OTG_D[0..15]

OTG_RESET

OTG_LSPEED

OTG_FSPEED

OTG_CS

OTG_A0

OTG_A1

OTG_OE

OTG_WE

TD_HS

TD_VS

27MHz

TD_D[0..7]

TD_CLK27

TD_CLK27

Title

Size Document Number Rev

Date: Sheet

of

TOP LEVEL 2.0

ALTERA DE2

B

324Wednesday, August 02, 2006

Title

Size Document Number Rev

Date: Sheet

of

TOP LEVEL 2.0

ALTERA DE2

B

324Wednesday, August 02, 2006

Title

Size Document Number Rev

Date: Sheet

of

TOP LEVEL 2.0

ALTERA DE2

B

324Wednesday, August 02, 2006

USB DEVICE PAGE 22

OTG_WE

OTG_OE

OTG_RESET

OTG_DACK0

OTG_DACK1

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_CS

OTG_A1

OTG_A0 OTG_D[0..15]

OTG_LSPEED

OTG_FSPEED

12MHZ

VIDEO PAGE 23-24

VGA_BLANK

VGA_R[0..9]

VGA_G[0..9]

VGA_B[0..9]

VGA_SYNC

VGA_CLOCK

VGA_HS

VGA_VS

TD_D[0..7]

TD_HS

TD_VS

TD_RESET

I2C_SDATI2C_SCLK

27MHz

TD_CLK27

ETHERNET PAGE 12

ENET_RESET

25MHZ

ENET_CMD

ENET_IOR

ENET_IOW

ENET_CS

ENET_INT

ENET_D[0..15]

INPUT PAGE 13-17

GPIO_B[0..71]

PS2_CLK PS2_DAT

SW[0..17]

UART_TXD UART_RXD

KEY[0..3]

50MHZ

EXT_CLOCK

IRDA_TXD IRDA_RXD

MEMORY PAGE 18-19

FLASH_RESET

FLASH_WE

FLASH_A[0..21]

FLASH_CE

FLASH_OE

FLASH_D[0..7]

DRAM_A[0..11]

DRAM_LDQM

DRAM_UDQM

DRAM_CLK

DRAM_CKE

DRAM_BA0

DRAM_BA1

DRAM_D[0..15]

DRAM_WE

DRAM_CAS

DRAM_RAS

DRAM_CS

SRAM_A[0..17]

SRAM_D[0..15]

SRAM_WE

SRAM_CE

SRAM_OE

SD_DATSD_CMD

SD_CLK

SRAM_UB

SRAM_LB

SD_DAT3

EP2S35 PAGE 7-11

NCONFIG

TDI

TMS

TDO

CONF_DONE

NSTATUS

TCK

NCE

ASDO

DCLK

NCSO

DATA0

LED[5..26]

SW[10..17]

GPIO_B[0..71]

FLASH_A[0..21]

FLASH_D[0..7]

SD_DAT

SD_CLK

SD_CMD

HEX6_D[0..6]

HEX4_D[0..6]

HEX7_D[0..6]

HEX5_D[0..6]

KEY[0..3]

SW[6..9]

SRAM_CE

SRAM_WE

SRAM_A[0..17]

SRAM_D[0..15]

SRAM_OE

FLASH_CE

FLASH_OE

FLASH_RESET

FLASH_WE

VGA_B[0..9]

VGA_CLOCK

VGA_R[0..9]

VGA_G[0..9]

VGA_BLANK

VGA_SYNC

TD_D[0..7]

ENET_D[0..15]

VGA_VS

VGA_HS

TD_RESET

TD_HS

TD_VS

27MHz

ENET_RESET

25MHZ

ENET_CMD

ENET_INT

LINK_D2

ENET_IOR

ENET_IOW

ENET_CS

SD_DAT3

LINK_D3

AUD_XCK

AUD_BCLK

AUD_DACDAT

AUD_DACLRCK

AUD_ADCLRCK

AUD_ADCDAT

I2C_SCLK

I2C_SDAT

UART_RXD

UART_TXD

PS2_CLK

PS2_DAT

SW[3..5]

LCD_D[0..7]

LCD_WR

LCD_EN

LCD_RS

LCD_BLON

LCD_ON

OTG_DREQ1

OTG_DREQ0

OTG_DACK1

OTG_DACK0

OTG_RESET

OTG_INT1

OTG_INT0

HEX3_D[0..6]

HEX2_D[0..6]

HEX1_D[0..6]

HEX0_D[0..6]

OTG_CS

OTG_OE

OTG_WE

OTG_A0

OTG_A1

OTG_D[0..15]

SW[0..2]

LED[0..4]

DRAM_UDQM

DRAM_LDQM

DRAM_D[0..15]

DRAM_BA1

DRAM_CS

DRAM_BA0

DRAM_RAS

DRAM_CKE

DRAM_CAS

DRAM_CLK

DRAM_WE

DRAM_A[0..11]

50MHZ

EXT_CLOCK

SRAM_UB

SRAM_LB

IRDA_TXD

IRDA_RXD

OTG_LSPEED

OTG_FSPEED

LINK_D0

LINK_D1

TD_CLK27

PWR PAGE 20

USB BLASTER PAGE 21

DATA0

NCSO

DCLK

ASDO

TDO

TMS

TDI

NCONFIG

TCK

CONF_DONE

NCE

NSTATUS

LINK_D3

LINK_D0

LINK_D1

LINK_D2

12MHZ

DISPLAY PAGE 5-6

HEX0_D[0..6]

HEX1_D[0..6]

HEX2_D[0..6]

HEX3_D[0..6]

HEX4_D[0..6]

HEX5_D[0..6]

HEX6_D[0..6]

HEX7_D[0..6]

LCD_BLON

LCD_ON

LCD_WR

LCD_D[0..7]

LCD_EN

LCD_RS

LED[0..26]

AUDIO PAGE 4

AUD_BCLK

AUD_DACDAT

AUD_ADCLRCK

AUD_DACLRCK

AUD_ADCDAT

I2C_SDATI2C_SCLK

AUD_XCK

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

AUD_BCLK

AUD_DACDAT

AUD_ADCLRCK

AUD_DACLRCK

AUD_ADCDAT

I2C_SDAT

I2C_SCLK

AUD_XCK

AGND AGND

AGNDAGND

AGNDAGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

VCC33VCC33

A_VCC33

A_VCC33

A_VCC33

A_VCC33

Title

Size Document Number Rev

Date: Sheet

of

AUDIO 2.0

ALTERA DE2

A

424Tuesday, July 25, 2006

Title

Size Document Number Rev

Date: Sheet

of

AUDIO 2.0

ALTERA DE2

A

424Tuesday, July 25, 2006

Title

Size Document Number Rev

Date: Sheet

of

AUDIO 2.0

ALTERA DE2

A

424Tuesday, July 25, 2006

I2C ADDRESS READ IS 0x34

I2C ADDRESS WRITE IS 0x35

LINE IN

MIC IN

LINE OUT

BC3

0.1U

BC3

0.1U

R8 680R8 680

C1 1UC1 1U

TC1 100U/6.3VTC1 100U/6.3V

C2 1UC2 1U

R7 330R7 330

BC4

0.1U

BC4

0.1U

R11

47K

R11

47K

C4

1000P

C4

1000P

C3

1U

C3

1U

L

1

R

2

GND

3

NCR

4

NCL

5

J1

PHONE JACK P

J1

PHONE JACK P

L

1

R

2

GND

3

NCR

4

NCL

5

J2

PHONE JACK B

J2

PHONE JACK B

BC2

0.1U

BC2

0.1U

R10

47K

R10

47K

R9

47K

R9

47K

R6

4.7K

R6

4.7K

R1

2K

R1

2K

R5

4.7K

R5

4.7K

BC1

0.1U

BC1

0.1U

R2

2K

R2

2K

TC2 100U/6.3VTC2 100U/6.3V

BCLK

7

HPVDD

12

XTO

2

DCVDD

3

MBIAS

21

MICIN

22

RLINEIN

23

LLINEIN

24

MODE

25

CSB

26

SDIN

27

SCLK

28

ROUT

17

AVDD

18

AGND

19

VMID

20

LOUT

16

HPGND

15

RHPOUT

14

LHPOUT

13

XTI/MCLK

1

DGND

4

ADCLRCK

11

ADCDAT

10

DBVDD

5

CLKOUT

6

DACDAT

8

DACLRCK

9

U1

WM8731

U1

WM8731

R4 4.7KR4 4.7K

L

1

R

2

GND

3

NCR

4

NCL

5

J3

PHONE JACK G

J3

PHONE JACK G

R3 4.7KR3 4.7K

C5 10UC5 10U

L1 BEADL1 BEAD

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

LED10

LED11

LED13

LED12

LED16

LED17

LED15

LED14

LED9

LED8

LED2

LED3

LED1

LED0

LED7

LED6

LED4

LED5

LED18

LED20

LED21

LED19

LED22

LED23

LED24

LED25

LED26

LCD_D2

LCD_VCC

LCD_D0

LCD_D6

LCD_D7

LCD_D1

LCD_D4

LCD_BL

LCD_D3

LCD_D5

LCD_CONT

LCD_BLON

LCD_ON

LCD_D[0..7]

LCD_EN

LCD_RS

LED[0..26]

LCD_WR

VCC43

VCC43

VCC43

VCC5

Title

Size Document Number Rev

Date: Sheet

of

LCD AND LED 2.0

ALTERA DE2

B

524Tuesday, July 25, 2006

Title

Size Document Number Rev

Date: Sheet

of

LCD AND LED 2.0

ALTERA DE2

B

524Tuesday, July 25, 2006

Title

Size Document Number Rev

Date: Sheet

of

LCD AND LED 2.0

ALTERA DE2

B

524Tuesday, July 25, 2006

1

2

3

4 5

6

7

8

RN6

330

RN6

330

R16

1K

R16

1K

1

2

3

4 5

6

7

8

RN1

330

RN1

330

LEDR4 LEDRLEDR4 LEDR

GND

1

VCC

2

CONT

3

RS

4

WR

5

EN

6

D0

7

D1

8

D2

9

D3

10

D4

11

D5

12

D6

13

D7

14

BL

15

GND

16

2 X 16 DIGIT LCD

U2

LCD-2x16

2 X 16 DIGIT LCD

U2

LCD-2x16

LEDG1 LEDGLEDG1 LEDG

Q5

8050

Q5

8050

R17

47

R17

47

LEDR5 LEDRLEDR5 LEDR

LEDR6 LEDRLEDR6 LEDR

LEDR7 LEDRLEDR7 LEDR

R15

680

R15

680

1

2

3

4 5

6

7

8

RN7

330

RN7

330

R14 680R14 680

Q3

8050

Q3

8050

Q4 8550Q4 8550

LEDG6 LEDGLEDG6 LEDG

LEDG0 LEDGLEDG0 LEDG

LEDR1 LEDRLEDR1 LEDR

LEDG3 LEDGLEDG3 LEDG

LEDR9 LEDRLEDR9 LEDR

C6

1U

C6

1U

LEDR8 LEDRLEDR8 LEDR

Q2 8550Q2 8550

1

2

3

4 5

6

7

8

RN2

330

RN2

330

LEDG8 LEDGLEDG8 LEDG

Q1 8050Q1 8050

LEDR3 LEDRLEDR3 LEDR

1

2

3

4 5

6

7

8

RN3

330

RN3

330

LEDR14 LEDRLEDR14 LEDR

LEDG5 LEDGLEDG5 LEDG

LEDR15 LEDRLEDR15 LEDR

LEDR16 LEDRLEDR16 LEDR

LEDR17 LEDRLEDR17 LEDR

LEDG2 LEDGLEDG2 LEDG

LEDR0 LEDRLEDR0 LEDR

1

2

3

4 5

6

7

8

RN4

330

RN4

330

R13 680R13 680

LEDR10 LEDRLEDR10 LEDR

R12

680

R12

680

LEDR11 LEDRLEDR11 LEDR

LEDR12 LEDRLEDR12 LEDR

1

2

3

4 5

6

7

8

RN5

330

RN5

330

LEDG7 LEDGLEDG7 LEDG

LEDR13 LEDRLEDR13 LEDR

LEDR2 LEDRLEDR2 LEDR

LEDG4 LEDGLEDG4 LEDG

剩余23页未读,继续阅读

资源评论

fendou123kaixin2015-05-23参加了一个比赛,很有借鉴价值

fendou123kaixin2015-05-23参加了一个比赛,很有借鉴价值

xymbmcu

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功