低功耗的设计与实现方法22CMOS电路低功耗设计的基本方法和途径.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

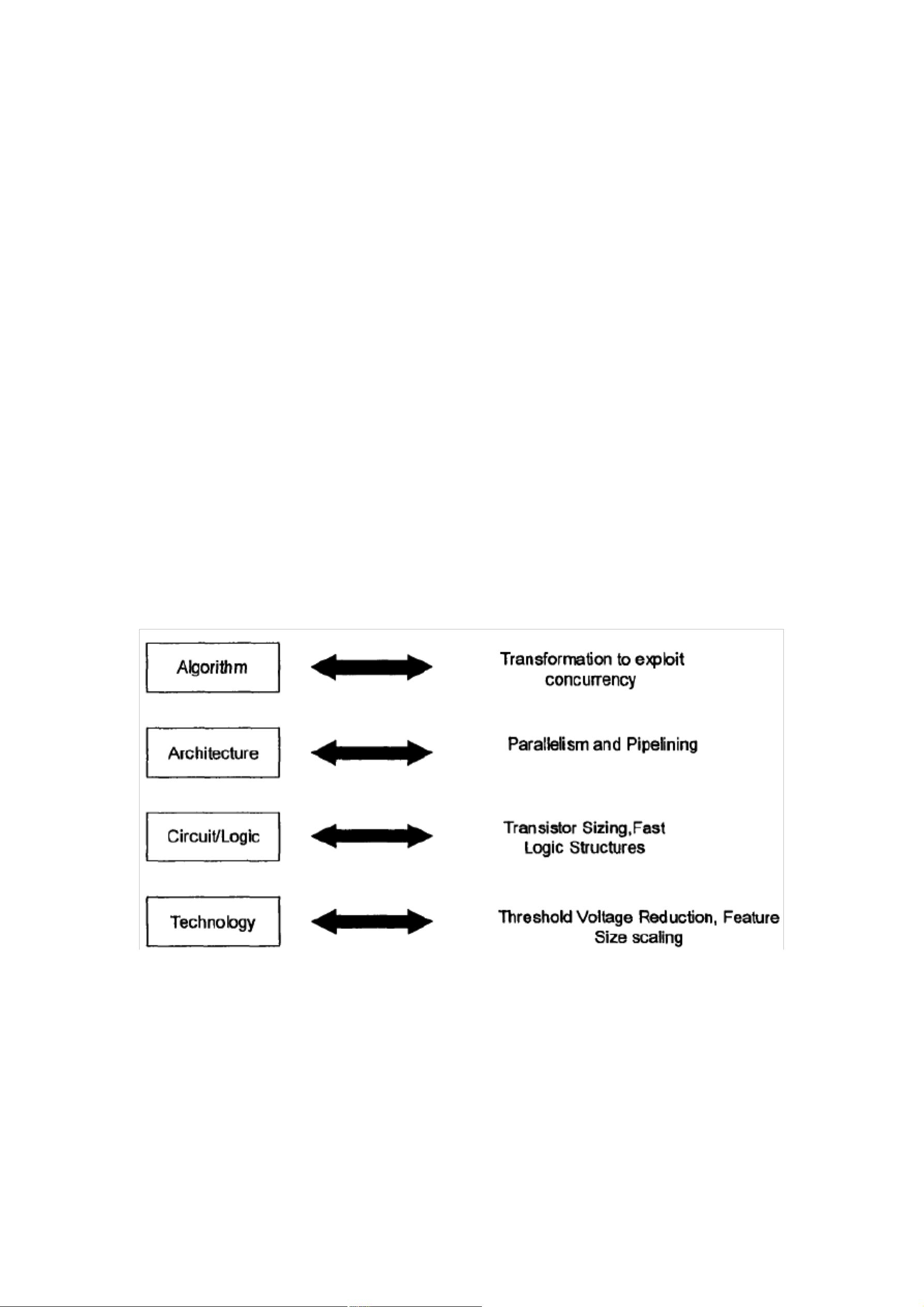

低功耗设计是现代电子设备,特别是集成电路(IC)设计的关键考虑因素。随着技术的进步,22nm CMOS工艺已成为实现高效能和低功耗的重要手段。本文将探讨22nm CMOS电路中低功耗设计的基本方法和途径。 降低工作电压是降低功耗的有效策略。根据公式P = C * V^2 * f * α,功耗与工作电压的平方成正比,因此减少Vdd可以显著减少功耗。然而,降低电压会增加电路的延迟,影响性能。设计者需要在速度和功耗之间找到平衡,通常保证工作电压在0.13V至0.11V之间,以避免漏电流的急剧增加。 降低负载电容也是减小功耗的重要途径。负载电容主要由器件的栅电容、节点电容和连线电容组成。随着工艺尺寸的减小,连线电容变得越来越重要。设计师可以通过选择小型器件、缩短连线长度以及优化物理布局来减少负载电容。 第三,减少开关活动性是另一种关键策略。开关活动性与功耗直接相关,包括数据频率f和开关活动率α。伪跳变,即无效的信号变化,会增加不必要的功耗。设计者可以优化逻辑设计,减少伪跳变的产生,或者通过更短的信号传播路径来限制其影响。 此外,低功耗设计还包括有效功率管理,例如使用门控技术关闭未使用的单元,以及在系统空闲时关闭电源。在选择逻辑单元和集成部件时,要考虑其对功耗、性能和面积的影响,寻求三者之间的平衡。并行设计和流水线技术可以在保持性能的同时,通过牺牲部分面积来优化功耗。 在工艺层面,低功耗技术包括降低阈值电压,减小晶体管尺寸,增加金属层数,以及采用特殊工艺,如绝缘体上硅(SOI)、多阈值电压器件、低温CMOS和新型栅氧化物材料等。这些技术有助于减少电源电压和开关电容,降低漏电流,从而实现更低的功耗。 版图优化则需要兼顾器件和互连的优化,确保在减少电容和提高效率的同时,不会引入额外的耦合寄生电容,进一步影响整体功耗。 低功耗22nm CMOS设计涉及多个层面,包括电压、负载电容、开关活动性和工艺优化。通过综合运用这些策略,设计者能够实现高性能且低能耗的集成电路,满足日益增长的能源效率需求。

- 粉丝: 6761

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功