7、systemverilog语法和验证相关流程.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

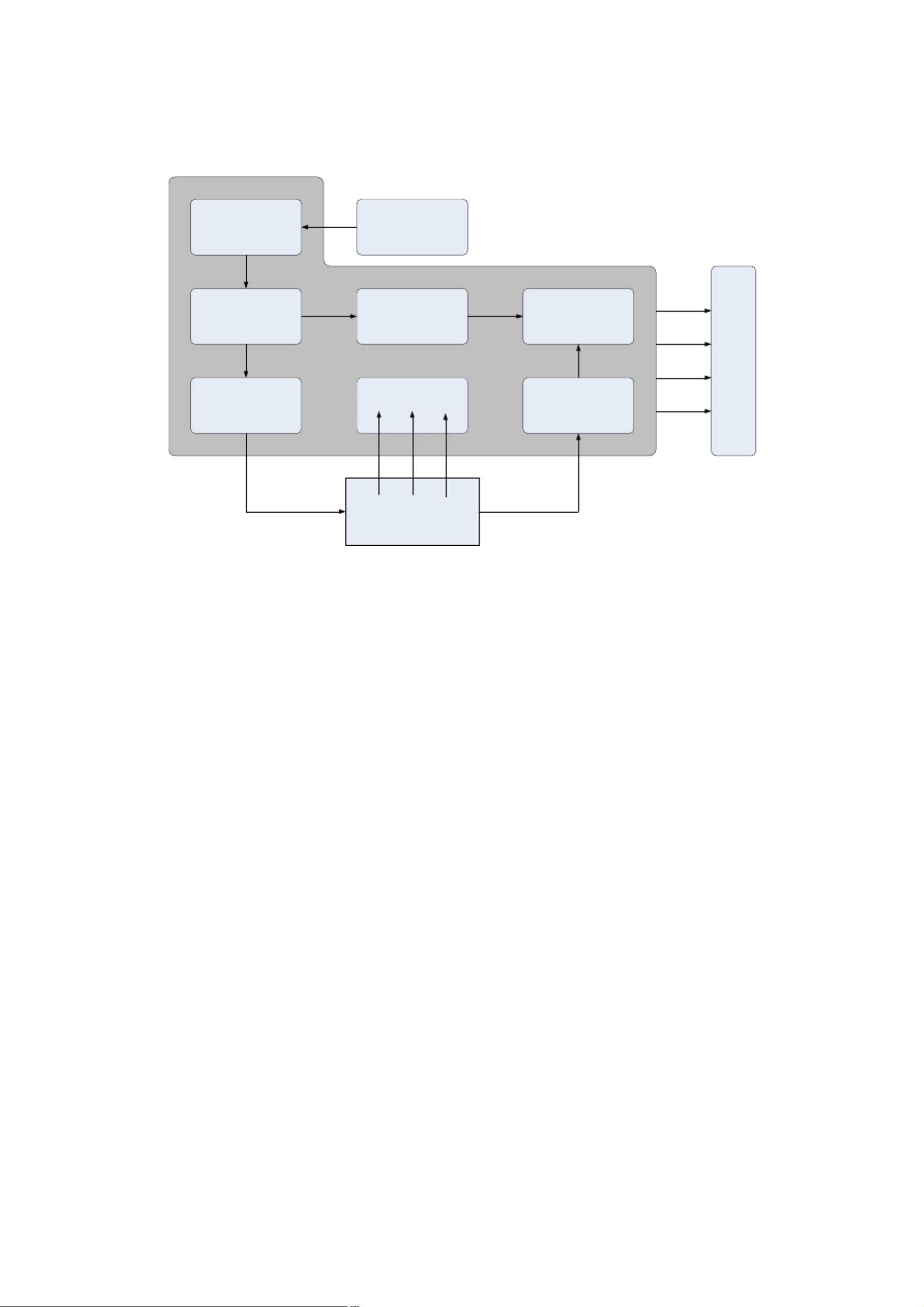

SystemVerilog是一种强大的硬件描述和验证语言,它在Verilog的基础上进行了大幅度的扩展,增加了许多高级特性,使得设计和验证的效率大大提高。本文件主要涵盖了SystemVerilog的语法和验证流程,以下是相关知识点的详细说明: 1. **验证环境构成**: - **测试平台发生器**:用于生成测试用例,将高级描述的测试行为转化为具体的激励。 - **代理(Proxy)**:作为数据传输的桥梁,将测试平台生成的数据分配给待测设计(DUT)。 - **记分板(Scoreboard)**:存储并比较数据,通常与检测器结合,用于验证DUT输出是否符合预期。 - **驱动层(Driver)**:根据测试用例处理数据,产生驱动DUT的激励。 - **监测器(Monitor)**:捕获DUT的输出,传递给记分板进行比较。 - **断言(Assert)**:用于检查设计中的条件,发现潜在错误,需要设计者和验证者的合作来有效使用。 - **覆盖率统计**:包括功能覆盖率、代码覆盖率和自定义覆盖点,衡量验证进度。 2. **SystemVerilog的扩展**: - **C语言数据类型**:增强了数据类型的表达能力,如结构体、数组等。 - **接口(Interface)**:提供了一种模块间连接的高级抽象,简化了模块间的互连,允许在接口中包含各种元素,如信号、变量、任务、函数等。 - **接口示例**:定义接口`interface chip_bus`,包含信号`read_request`、`read_grant`、`address`和`data`,并在模块中使用接口`RAM`和`CPU`,方便地引用接口中的信号。 3. **全局声明和语句**: - SystemVerilog支持全局声明,这意味着变量或常量可以在整个设计范围内可见,这在多模块协同验证中特别有用。 - 另外,SystemVerilog引入了任务(task)和函数(function),允许编写更复杂的控制逻辑和数据处理。 4. **验证流程**: - **环境构建**:搭建包括代理、记分板、驱动层和监测器在内的验证环境。 - **测试用例设计**:创建能够覆盖设计功能的各种测试情况。 - **激励生成**:测试平台发生器根据测试用例生成激励序列。 - **运行验证**:驱动层驱动DUT,监测器收集DUT的响应,记分板进行比较,断言检查设计内部状态。 - **覆盖率分析**:通过覆盖率工具检查验证的全面性,并根据需求逐步提高覆盖率。 5. **调试与优化**: - 验证过程中,断言和覆盖率工具对于调试和优化设计至关重要,它们可以帮助定位错误,提高验证质量。 SystemVerilog通过提供更丰富的语法和验证机制,极大地提升了IC验证的效率和质量。理解并熟练运用这些概念和工具,是现代IC设计和验证工程师必备的技能。

剩余11页未读,继续阅读

- 粉丝: 6746

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于SpringBoot和Redis的秒杀系统.zip

- yolo数据集.txt

- (源码)基于RabbitMQ的消息队列系统.zip

- (源码)基于SpringBoot框架的Guns后台管理系统.zip

- (源码)基于GoogleCloudIoT的云端烟雾机控制系统CloudSmoker.zip

- JAVA的SpringBoot 高校宿舍管理系统源码带视频和文档数据库 MySQL源码类型 WebForm

- (源码)基于Python的火车票自动购买系统.zip

- 人工智能-大模型-一个智能问答系统,能够自动将用户的自然语言问题转换成 SQL 查询,并以可视化形式展示结果

- trumtime安装所需的全部资源以及步骤

- (源码)基于JavaWeb的宿舍管理系统.zip

信息提交成功

信息提交成功