数字系统设计实验报告计数器、累加器.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

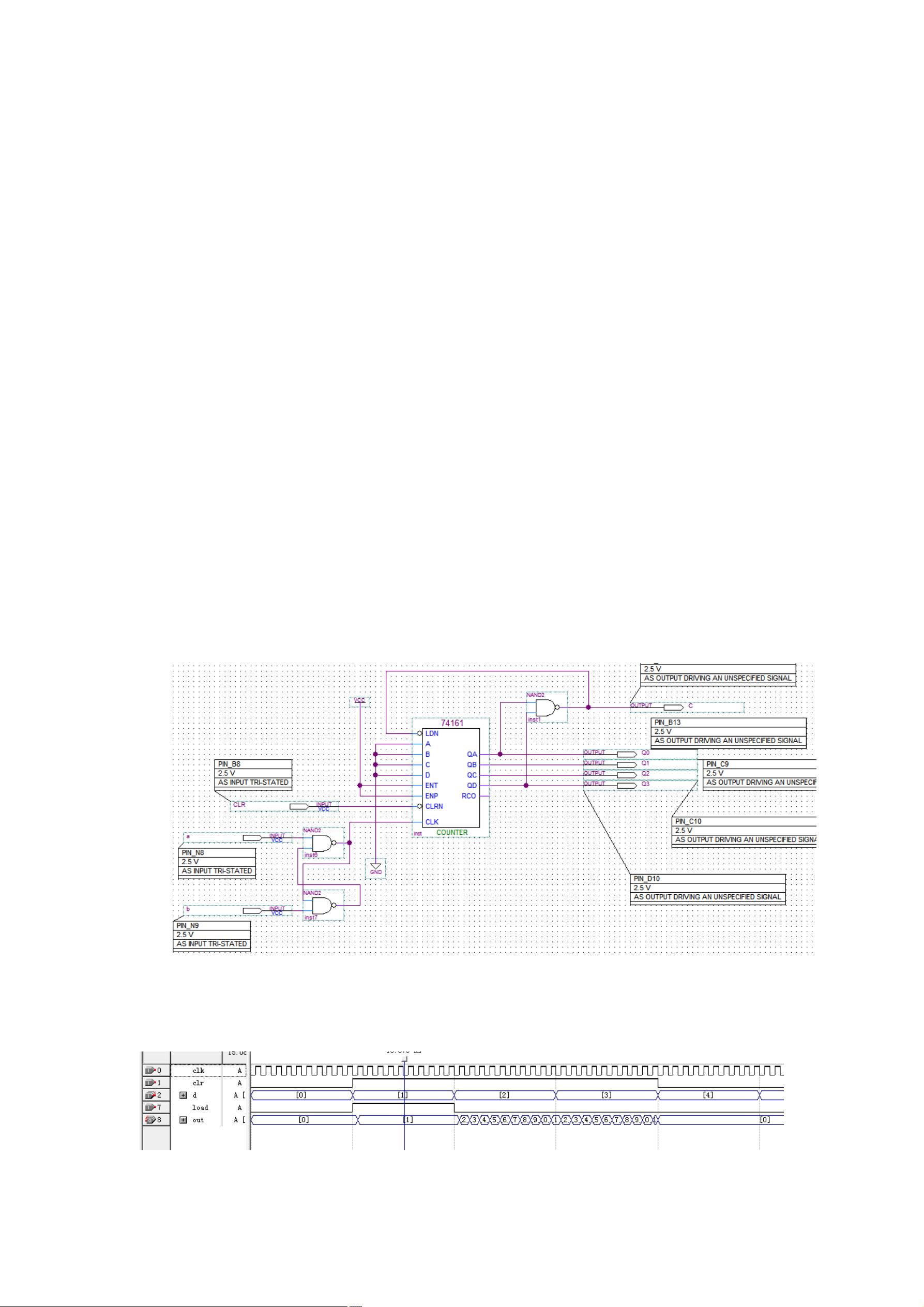

在数字系统设计中,计数器和累加器是两种重要的基本组件,广泛应用于各种数字逻辑电路中。这篇实验报告详细介绍了如何设计和实现这两种组件,主要涉及Verilog HDL语言以及图形化设计方法。 计数器是用于计数的数字电路,可以按照预设的顺序依次改变其状态。在实验五中,学生被要求设计一个十进制计数器。十进制计数器是指在每次时钟脉冲到来时,计数值会增加1,直到达到9后再回到0,形成0到9的循环。设计计数器通常分为两步:图形法设计和Verilog HDL语言设计。图形法设计通过连接门电路来实现计数逻辑,而Verilog HDL则是一种硬件描述语言,可以更抽象地描述计数器的行为。在Verilog中,计数器需要指定计数模式(如加法计数)、触发条件(时钟上升沿)、复位(异步清零,低电平有效)和置数(同步置数,高电平有效)等特性。完成设计后,需要通过仿真验证其正确性,再进行硬件下载和在线测试。 累加器则是另一种关键的数字电路,它在每次时钟脉冲到来时,将当前值与输入信号相加并保存结果。在实验六中,学生需要设计一个8位的累加器,这涉及到全加器和寄存器的设计。全加器是一个能同时处理两个二进制位的加法和进位的电路,而寄存器则是用于存储数据的电路。在文本输入方式下,学生先设计了8位全加器(add8_8.v)和8位寄存器(reg8.v),然后在原理图输入方式下组合这两个模块,构建出累加器电路(add8.bdf)。同样,完成设计后,需要进行功能仿真和硬件测试。 通过这两个实验,学生不仅复习了计数器和累加器的基本工作原理,还掌握了图形法和Verilog HDL语言的设计方法,加深了对设计流程的理解,同时也熟悉了数字系统实验开发箱的使用。此外,实验中遇到的问题,如试验箱的抖动,通过在原理图上添加去抖电路解决,体现了在实际设计中对电路稳定性的重视。在波形仿真时,去除去抖电路以便于观察和分析,展示了在不同阶段根据需求调整设计的灵活性。 这个实验报告涵盖了数字系统设计中的重要概念和技术,包括计数器和累加器的原理、Verilog HDL编程、原理图设计、仿真验证以及硬件测试等,为学生提供了宝贵的实践经验,有助于他们理解和应用数字系统设计的基础知识。

- 粉丝: 6756

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功