大规模可编程逻辑器件综合实验 实验报告

姓名 班级 学号 实验日期 年 月 日

计数器的设计

一、实验目的

1、熟练掌握原理图设计电路的方法。

2、掌握调用元件图形符号的方法。

3、用原理图方法设计我们所需的各种计数器。

二、实验原理

两个二进制(十进制)的可逆计数器串行就可以组成一个 0-255(0-99)的可逆计数器。具体连接方

法就是把低位计数器的进位输出送到高位计数器的时钟输入,其它的连接就与这个具体几进制计数器的端

口决定。这是一个最基本的方法,在数字电子课程中已经学过。

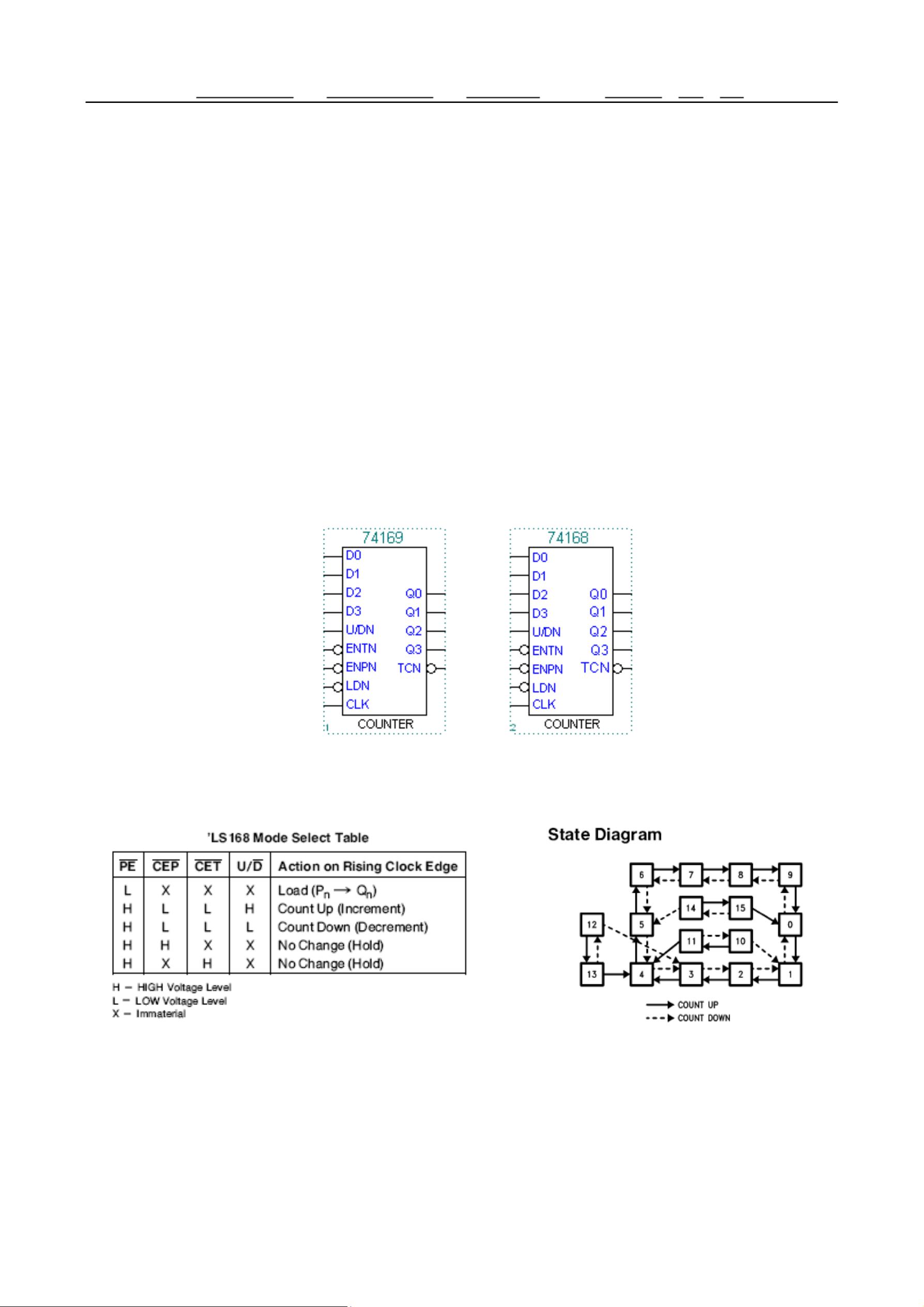

对于二进制可逆计数器可用一个 74169(十进制可逆计数器 74168)得到。如果只要求加法计数器则

有 74160(可预置 BCD 异步清除计数器)、74161(可予制四位二进制异步清除计数器)、74162(可预置 BCD

同步清除计数器)、74163(可予制四位二进制同步清除计数器)等几种计数器可以根据情况选用。

74168 和 74169 符号见下图:

74168 的状态图和 74169 的时序图如下,供设计参考

74169 时序图:

5

评论0

最新资源