8. 经 统 计 , 某 机 器 14 条 指 令 的 使 用 频 度 分 别 为 :

0.01,0.15,0.12,0.03,0.02,0.04,0.02,0.04,0.01,0.13,0.15,

0.14,0.11,0.03。分别求出用等长码、Huffman 码、只有两种码长的扩

展操作码 3 种编码方式的操作码平均码长。解: 等长操作码的平均码长

=4 位;Huffman 编码的平均码长=3.38 位;只有两种码长的扩展操作码的

平均码长=3.4 位。9.若某机要求:三地址指令 4 条,单地址指令 255 条,

零地址指令 16 条。设指令字长为 12 位.每个地址码长为 3 位。问能否以

扩展操作码为其编码?如果其中单地址指令为 254 条呢?说明其理由。答:①

不能用扩展码为其编码。 ∵指令字长 12 位,每个地址码占 3 位;

∴三地址指令最多是 2^(12-3-3-3)=8 条, 现三地址指令需 4

条, ∴可有 4 条编码作为扩展码, ∴单地址指令最多为 4×2^3

×2^3=2^8=256 条, 现要求单地址指令 255 条,∴可有一条编码作

扩展码 ∴零地址 指令最多为 1 ×2^3=8 条 不满足题目要求

∴不可能以扩展码为其编码。 ②若单地址指令 254 条,可以用

扩展码为其编码。 ∵依据①中推导,单地址指令中可用 2 条编码作为

扩展码 ∴零地址指令为 2×2^3=16 条,满足题目要求

note:

三地址指令格式: 操作码地址码地址码地址码

3 位 3 位 3 位 3 位

单地址指令格式: 操作码地址码

9 位 3 位 所以前面 9 位由于三地址指令用了最前面 3 位,还有中间 6

位可作为编码(也就是总共可以有 9 位作为单地址指令的指令操作码的编

码)。减去 3 地址指令的 4 条,有 4*2^6=256 条,但由于韪目要求要有

255 条,所以剩下一个编码,已经用了 9 位的全部编码,最后零地址指令

(全部 12 位都可作为操作码的编码)还有 1*2^3=8(这是 12 位编码中最

后三位的)若只要求 254 种,则可以有(256-254)*2^3=16 条 10.某机

指令字长 16 位。设有单地址指令和双地址指令两类。若每个地址字段为 6

位.且双地址指令有 X 条。问单地址指令最多可以有多少条?答: 单地址

指令最多为(16-X)×2^6 P.S.双地址指令最多是

2^(16-6-6)=2^4=16 条, 现双地址指令有 X 条, ∴可有(16-X)条

编码作为扩展码, ∴单地址指令最多为(16-X)×2^6=256 条 11.何

谓指令格式的优化?简要列举包括操作码和地址码两部分的指令格式优化

可采用的各种途径和思路。答:指令格式的优化指如何用最短位数表示指令

的操作信息和地址信息,使程序中指令的平均字长最短。 ①操作码的

优化 采用 Huffman 编码和扩展操作码编码。 ②对地址码的优化:

采用多种寻址方式; 采用 0、1、2、3 等多种地址制; 在同

种地址制再采用多种地址形式,如寄存器-寄存器型、寄存器-主存型、主

存-主存型等; 在维持指令字在存储器按整数边界存储的前提下,使用

多种不同的指令字长度。12.某模型机 9 条指令使用频率为:

ADD(加)30% SUB(减)24% JOM(按负转移) 6%

STO(存) 7% JMP(转移)7% SHR(右移) 2%

CIL(循环) 3%CLA(清加) 20% STP(停机) 1%

要求有两种指令字长,都按双操作数指令格式编排,采用扩展操作码,并

限制只能有两种操作码码长。设该机有若干通用寄存器,主存为 16 位宽,

按字节编址,采用按整数边界存储。任何指令都在一个主存周期中取得,

短指令为寄存器-寄存器型,长指令为寄存器-主存型,主存地址应能变址

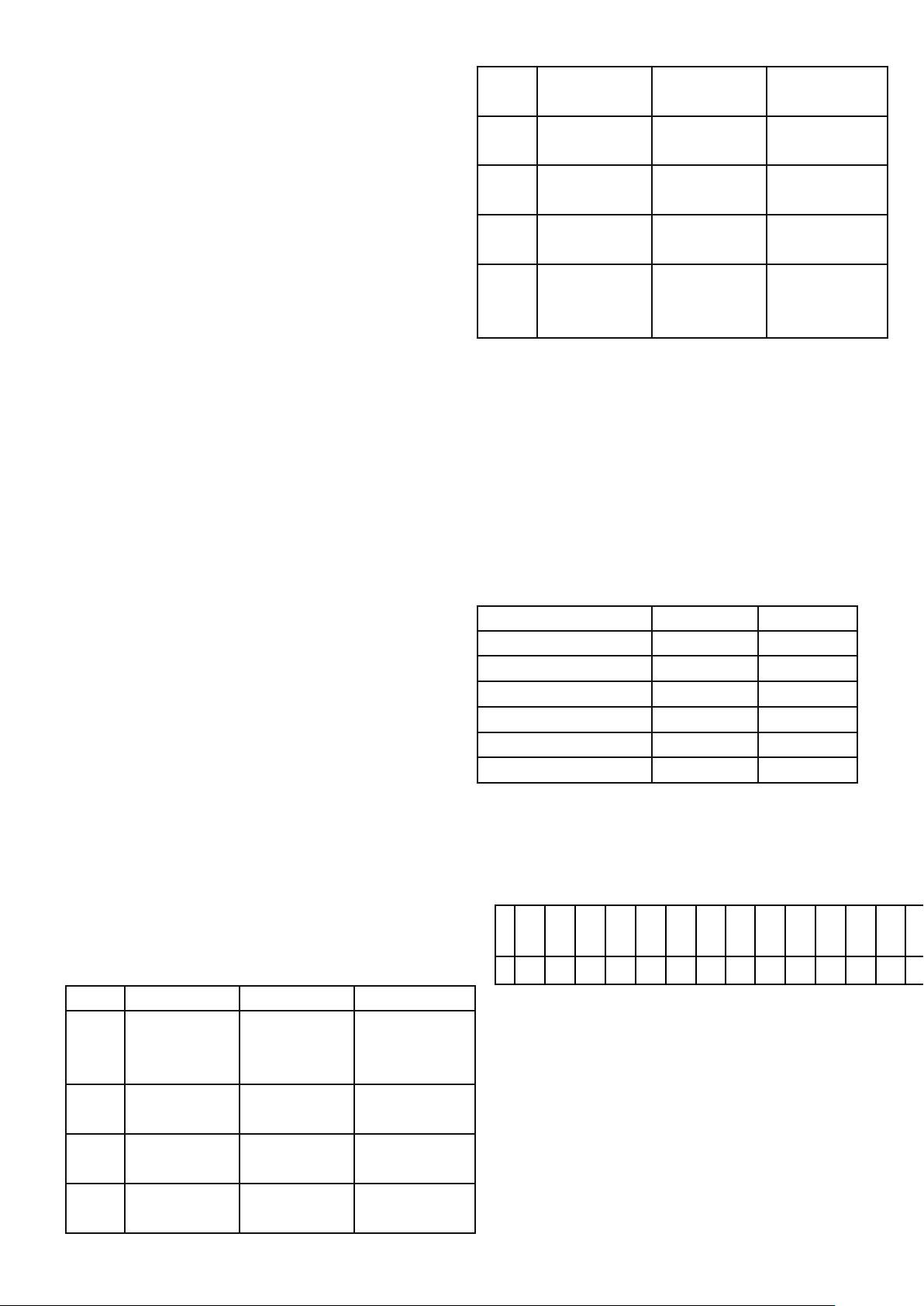

寻址。(1)仅根据使用频率,不考虑其它要求,设计出全 Huffman 操作码,

计算其平均码长;(2)考虑题目全部要求,设计优化实用的操作形式,并计

算其操作码的平均码长;(3)该机允许使用多少可编址的通用寄存器?(4)

画出该机两种指令字格式,标出各字段之位数;(5)指出访存操作数地址寻

址的最大相对位移量为多少个字节?解: 第(1)和(2)中 Huffman 和

扩展操作码的编码及平均码长如下表:

10

00

01

1100

1101

1110

11110

111110

111111

00

01

10

11000

11001

11010

11011

11100

11101

(3)8 个。 (4)两种指令格式如下图所示:

2 位 3 位 3 位

OP R1 R2

操作码 寄存器 1 寄存器 2

5 位 3 位 3 位 5 位

OP R1 X d

操作码 寄存器 1 变址寄存器 相对位移

主存逻辑地址

(5)访存操作数地址寻址的最大相对位移量为 32 个字节。13.设计

RISC 机器的一般原则及可采用的基本技术有那些?答:一般原则: (1)

确定指令系统时,只选择使用频度很高的指令及少量有效支持操作系统,高

级语言及其它功能的指令; (2)减少寻址方式种类,一般不超过两种;

(3)让所有指令在一个机器周期完成; (4)扩大通用寄存器个数,

一般不少于 32 个,尽量减少访存次数; (5)大多数指令用硬联实现,

少数用微程序实现; (6)优化编译程序,简单有效地支持高级语言实

现。 基本技术: (1)按 RISC 一般原则设计,即确定指令系统时,

选最常用基本指令,附以少数对操作系统等支持最有用的指令,使指令精简。

编码规整,寻址方式种类减少到 1、2 种。 (2)逻辑实现用硬联和微程

序相结合。即大多数简单指令用硬联方式实现,功能复杂的指令用微程序实

现。 (3)用重叠寄存器窗口。即:为了减少访存,减化寻址方式和指

令格式,简单有效地支持高级语言中的过程调用,在 RISC 机器中设有大量

寄存嚣,井让各过程的寄存器窗口部分重叠。 (4)用流水和延迟转移

实现指令,即可让本条指令执行与下条指令预取在时间上重叠。另外,将转

移指令与其前面的一条指令对换位置,让成功转移总是在紧跟的指令执行之

后发生,使预取指令不作废,节省一个机器周期。 (5)优化设计编译

系统。即尽力优化寄存器分配,减少访存次数。不仅要利用常规手段优化编

译,还可调整指令执行顺序,以尽量减少机器周期等。14.简要比较 CISC

机器和 RISC 机器各自的结构特点,它们分别存在哪些不足和问题?为什么

说今后的发展应是 CISC 和 RISC 的结合?答:CISC 结构特点:机器指令系

统庞大复杂。 RISC 结构特点:机器指令系统简单,规模小,复杂度低。

CISC 的问题: (1)指令系统庞大,一般 200 条以上; (2)

指令操作繁杂,执行速度很低; (3)难以优化生成高效机器语言程序,

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功