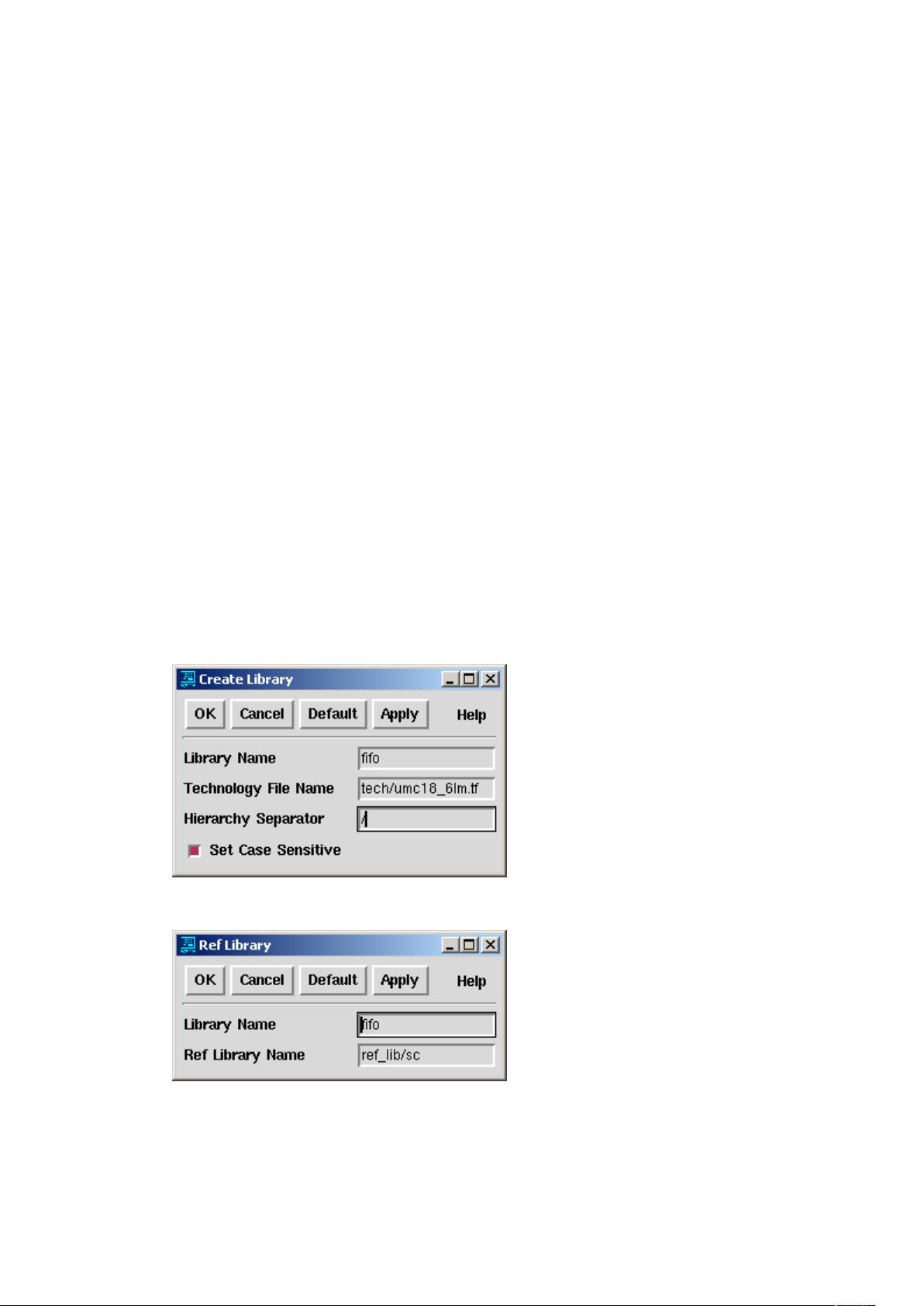

【DC、Astro设计流程入门】是一篇针对电子设计自动化(EDA)领域的文章,主要介绍了DC(Design Compiler)和Astro工具的使用流程,适用于初学者。DC是Synopsys公司的逻辑综合工具,而Astro则是一个布局布线工具,它们在集成电路设计中扮演着重要的角色。 **逻辑综合**是设计流程的第一部分,它将硬件描述语言(如Verilog或VHDL)编写的源代码转换成门级网表。在DC中,这一过程涉及到以下步骤: 1. **数据准备**:将stand cell、pad和RAM的数据库(db)复制到syn/library,源代码.v文件复制到syn/source,dc的setup文件(.synopsys_dc.setup)放入syn目录,综合脚本(包括约束脚本)放入syn/scripts,并创建syn/output和syn/reports目录以存放结果。 2. **运行Design Compiler**:进入syn目录,使用tcl模式启动DC,通过`dc_shell -t`命令调用`scripts/run.tcl`脚本来执行综合。在`run.tcl`和`cons.tcl`中可查看详细设置。 3. **数据分析**:综合完成后,`syn/output`目录下产生sdf(时序延迟文件)和sdc(标准约束文件),供后续仿真和布局布线使用。`syn/reports`下有面积和时序报告。例如,如果最大slack为-0.51ns,相对于8ns时钟周期较小,说明设计可以进入布局布线阶段。 在综合时,一些关键设置包括: - 使用slow库作为目标库。 - 设置stand cell为target_library,sc、io、ram及synthetic_library为link_library。 - 用pad模型模拟输入输出的驱动和负载。 - input_delay设为时钟周期的60%,output_delay约为30%。 - 设定pad和ram对应的cell为don’t_touch,以保持其位置不变。 - 在严格的约束条件下,-0.51ns的slack是可以接受的布局布线起点。 **布局布线**是设计流程的第二部分,主要在P-R目录下进行: 1. **数据准备**:将stand cell、pad和RAM的Milkyway库拷贝到P-R/ref_lib,布局布线脚本放至P-R/script,工艺相关文件至P-R/star_rcxt和P-R/tech,层次定义文件至P-R/map,并创建P-R/design_data和P-R/report目录。还需将综合后的`syn/output`下的fifo_mapped.v和fifo_mapped.sdc文件复制到P-R/design_data。 2. **布局布线**: - 使用Astro创建Milkyway设计库。启动Astro,通过Tools -> Data Prep,然后Library -> Create...,指定Technology File Name并创建库。接着,通过Library -> Add Ref...添加参考库,如ref_lib/sc。 布局布线过程还需要进一步设置和优化,确保满足时序和面积目标。Astro提供了丰富的工具和选项来调整布局、布线策略,以达到最佳性能。在完成布局布线后,新的时序报告和面积报告将在P-R/report目录下生成,供设计师评估设计性能。 DC和Astro设计流程涉及多个步骤,包括数据准备、综合、分析以及布局布线,每个步骤都需要对设计参数进行精确控制,以实现高性能、低功耗和小面积的目标。理解并熟练掌握这些工具和流程对于集成电路设计者至关重要。

剩余16页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于51单片机开发板设计的六位密码锁

- course_s5_linux应用程序开发篇.pdf

- course_s4_ALINX_ZYNQ_MPSoC开发平台Linux驱动教程V1.04.pdf

- course_s0_Xilinx开发环境安装教程.pdf

- 多边形框架物体检测20-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- course_s1_ALINX_ZYNQ_MPSoC开发平台FPGA教程V1.01.pdf

- course_s3_ALINX_ZYNQ_MPSoC开发平台Linux基础教程V1.05.pdf

- rwer456456567567

- AXU2CGB-E开发板用户手册.pdf

- 数据库设计与关系理论-C.J.+Date.epub

信息提交成功

信息提交成功