DM642_FPGA_HardDisk

需积分: 0 86 浏览量

更新于2011-04-14

收藏 3.04MB PDF 举报

根据给定文件的信息,我们可以提炼出以下相关的IT知识点:

### 1. DM642与FPGA在硬盘存储中的应用

- **DM642简介**:DM642是德州仪器(Texas Instruments)推出的一款高性能数字信号处理器(Digital Signal Processor, DSP),广泛应用于视频处理领域。它具有强大的数据处理能力,支持多种多媒体编解码标准,适用于数字视频录像机(DVR)、视频会议系统等场景。

- **FPGA概述**:FPGA(Field-Programmable Gate Array)即现场可编程门阵列,是一种集成有大量基本电路单元(如触发器、查找表等)的半导体芯片,用户可以根据需要通过软件编程来实现不同的逻辑功能。在本项目中,FPGA用于管理和控制DM642与硬盘之间的数据传输。

### 2. StreamDrive项目概述

- **目标**:StreamDrive项目的目标是利用DM642的EDMA(Enhanced Direct Memory Access)控制器将数据流式传输到硬盘驱动器(HDD)。同时,通过FPGA实现高效的数据缓存管理方案,提高数据吞吐量,减少CPU负载。

- **方法**:

- 使用FPGA作为中间件,管理DM642与HDD之间的数据传输。

- 采用Ultra DMA模式替代传统的PIO模式,显著提升HDD与DSP之间的数据传输速度。

- 通过测试结果展示使用EDMA后CPU利用率的降低情况。

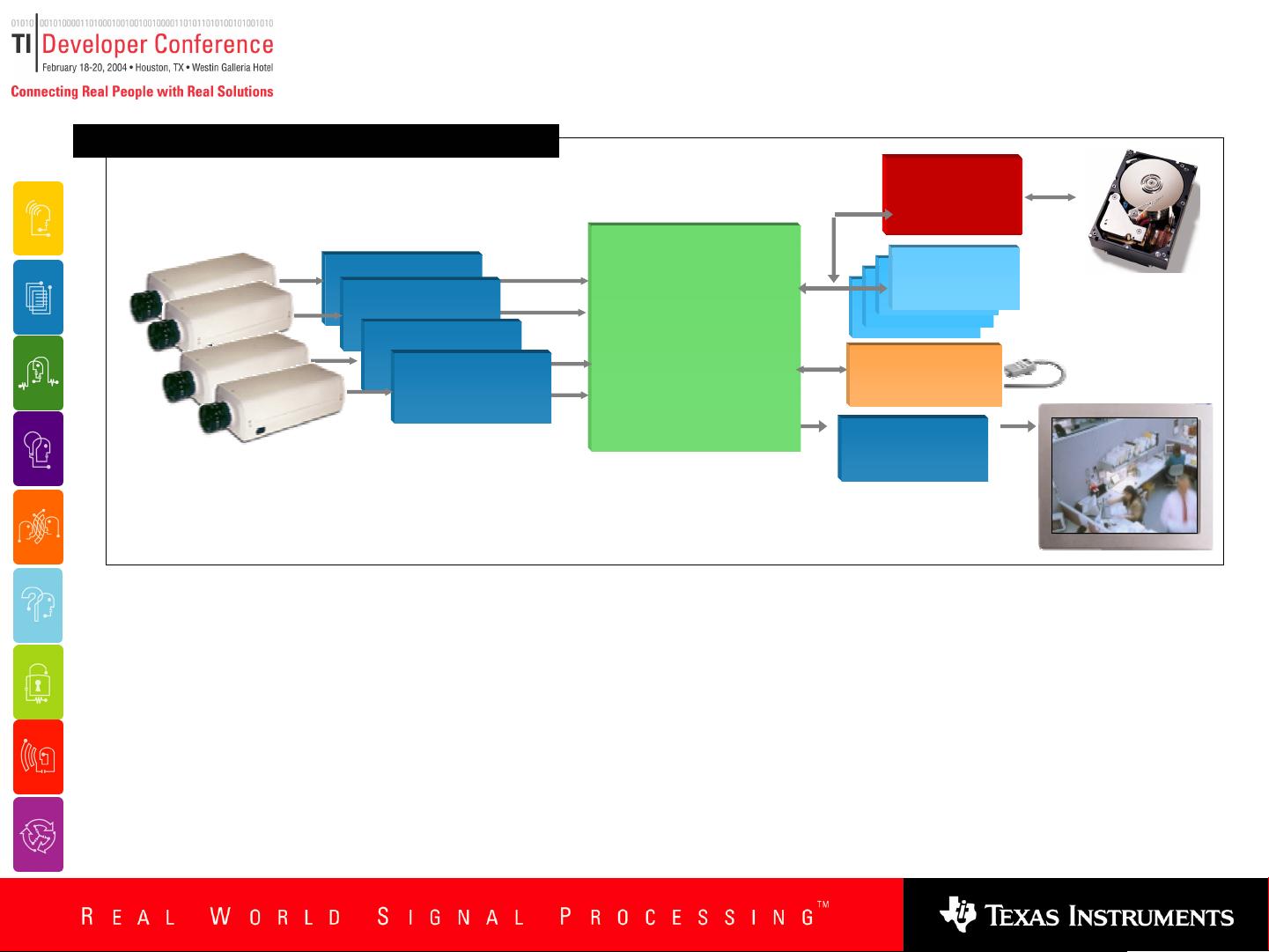

### 3. 数字视频录像机(DVR)示例

- **架构**:DVR通常包括多个视频输入端口、DM642处理器、SDRAM内存、FPGA以及硬盘等组件。其中,FPGA通过EMIF接口与硬盘进行数据交互。

- **功能**:DVR可以接收多路视频流,DM642负责视频压缩与临时存储,而FPGA则用于数据流的高速传输。

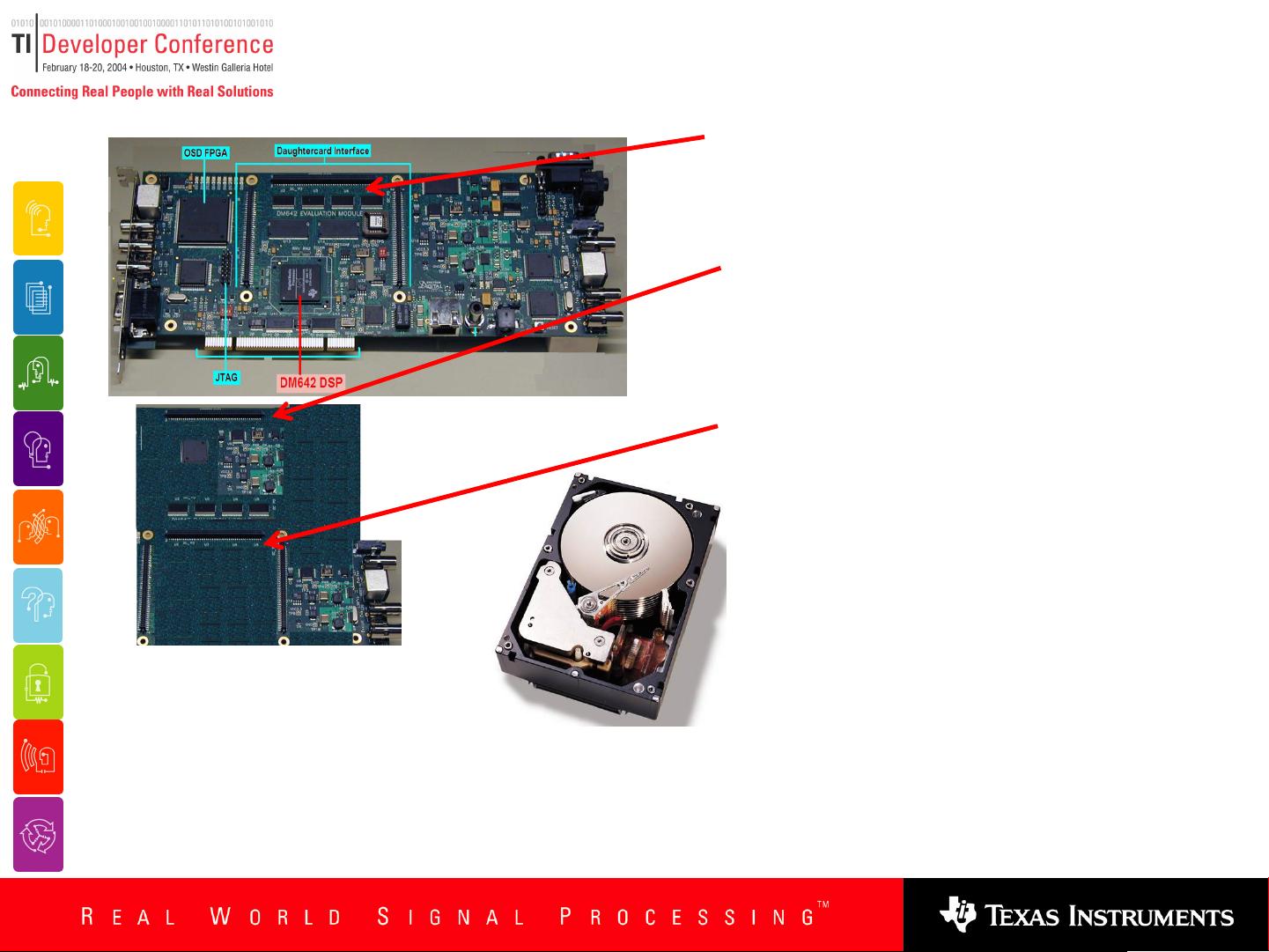

### 4. DM642 EVM/HDD开发系统

- **硬件结构**:DM642评估模块(EVM)配备有一个带有三个连接器的扩展槽,用于连接硬盘扩展板。硬盘通过扩展板上的连接器与DM642 EVM相连。

- **通信机制**:DM642 EVM通过16位EMIF接口与硬盘进行通信。FPGA主要负责构建FIFO(First In First Out)模块,用以接受来自EMIF接口的512字节数据包,并将其存储到硬盘中。此外,还设计了基于双反馈的VHDL状态机,用于创建C64x EDMA引擎与硬盘Ultra DMA模式之间的通信协议。

### 5. FPGA VHDL设计与实现

- **设计思路**:FPGA中包含的主要模块是FIFO,用于缓存数据包。此外,还需要设计一个基于VHDL的状态机来协调FIFO模块与HDD之间的数据交换。

- **实现细节**:FIFO模块的设计需考虑数据的先进先出特性,确保数据的完整性。而状态机的设计则需考虑与EDMA引擎的同步性,以及如何高效地利用Ultra DMA模式的特点来提高整体系统的性能。

### 6. 性能分析与测试

- **测试数据**:通过对使用EDMA后的CPU利用率进行统计分析,验证了FPGA+FIFO+Ultra DMA模式的有效性。同时,还提供了单视频解码算法下的PIO模式与Ultra DMA模式的数据吞吐量对比图,展示了不同模式下数据传输效率的差异。

- **结果总结**:通过一系列测试数据表明,在使用FPGA+FIFO+Ultra DMA模式时,不仅能够有效降低CPU的负载,还能显著提高数据传输速率,进而提升了整个系统的实时性和稳定性。

通过结合DM642 DSP、FPGA以及高效的硬盘数据传输模式,StreamDrive项目实现了高性能的视频数据流式传输系统,对于提升数字视频处理系统的实时性和稳定性具有重要意义。

xiaoyuanloveu

- 粉丝: 1

- 资源: 15

最新资源

- 红色喜庆吉祥结婚礼邀请函快闪模板.pptx

- 欧式风格白金简约婚礼邀请函快闪模板.pptx

- 西式浪漫小清新婚礼快闪邀请函模板.pptx

- 国民经济行业分类与国际标准行业分类(ISIC+Rev.4)的对照和匹配(供参考).docx

- 内核级后门RootKit技术总揽pdf版最新版本

- 经典网页游戏 传奇烈火战神一键端(单机+外网)可运营1.6GB

- 疫苗发布和接种预约-JAVA-基于springBoot疫苗发布和接种预约系统(毕业论文+开题)

- C语言复习资料文件,循环语句

- Web安全实践完整版推荐最新版本

- 图书管理-JAVA-基于springBoot图书管理系统设计与实现(毕业论文)

- TG1 线性优化策略.avi

- 小西黑客安全教程CHM版比较经典的基础教程最新版本

- 流浪宠物管理-JAVA-基于springBoot的流浪宠物管理系统的设计与实现(毕业论文+开题)

- https://upload.csdn.net/creation/uploadResources?spm=1000.2115.3001.5355

- 黑客零起点教程CHM版最新版本

- 让Cheat Engine 7.5支持luasocket