瞎搞Time_Quest_和无责任的笔记_第一章

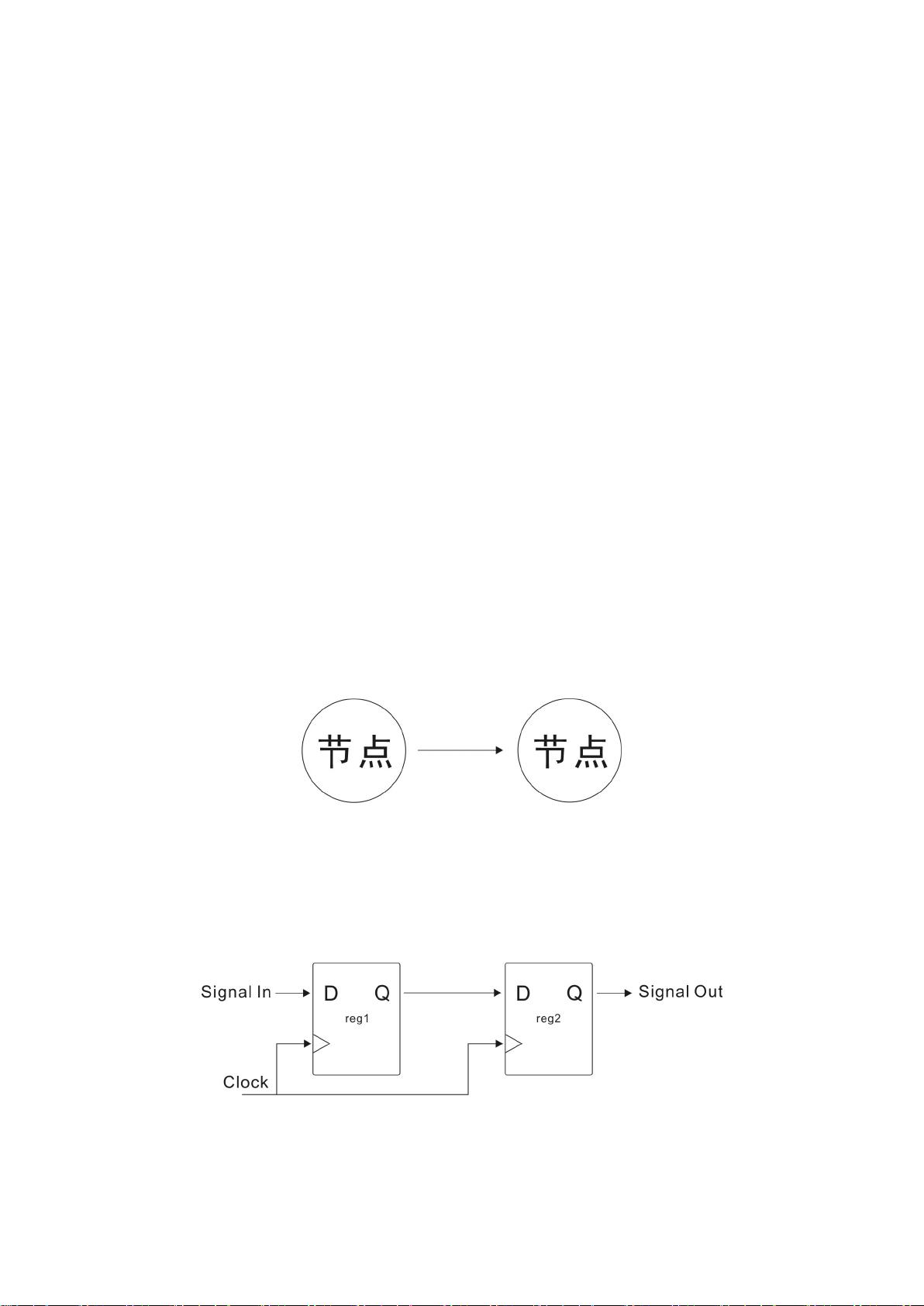

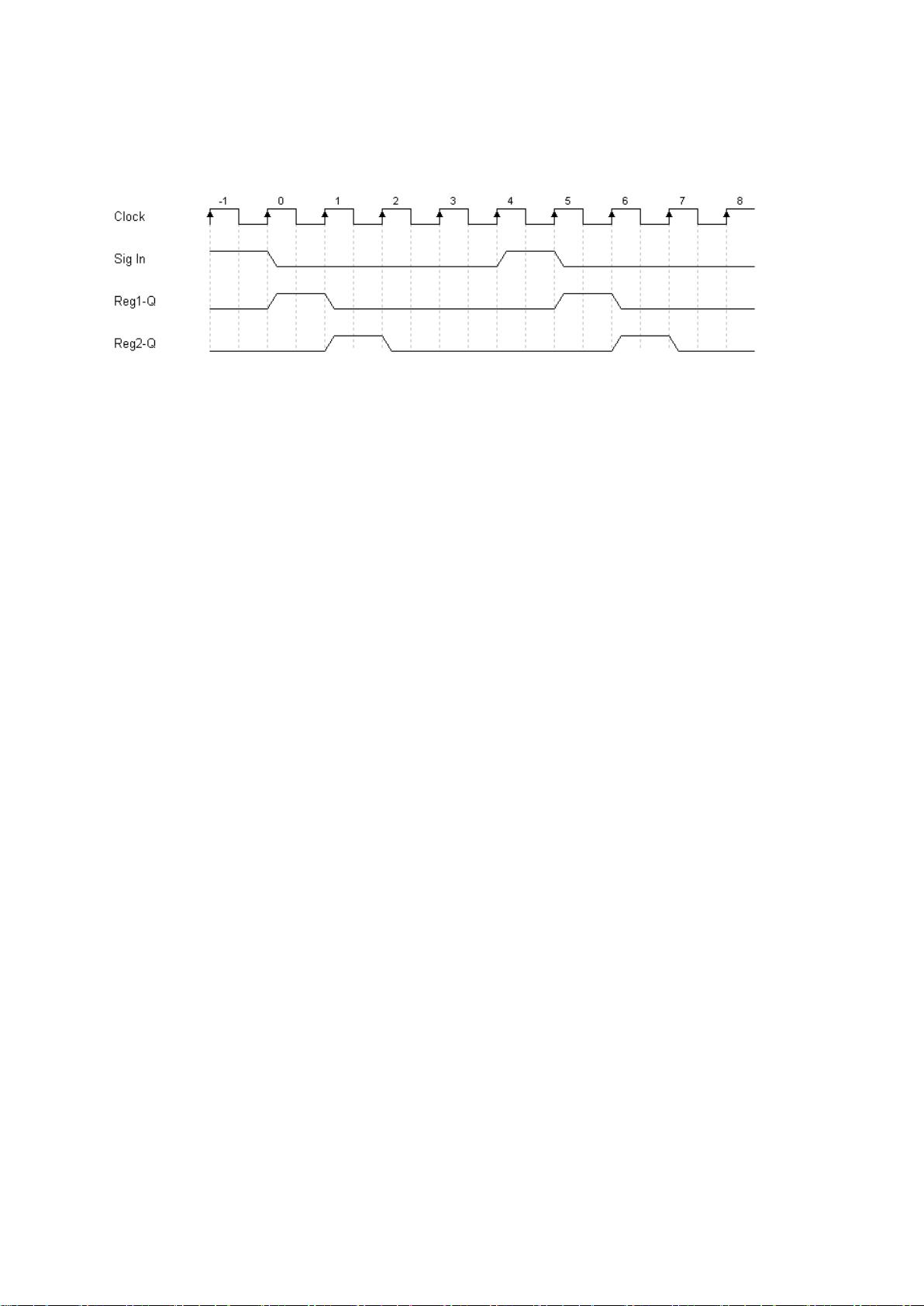

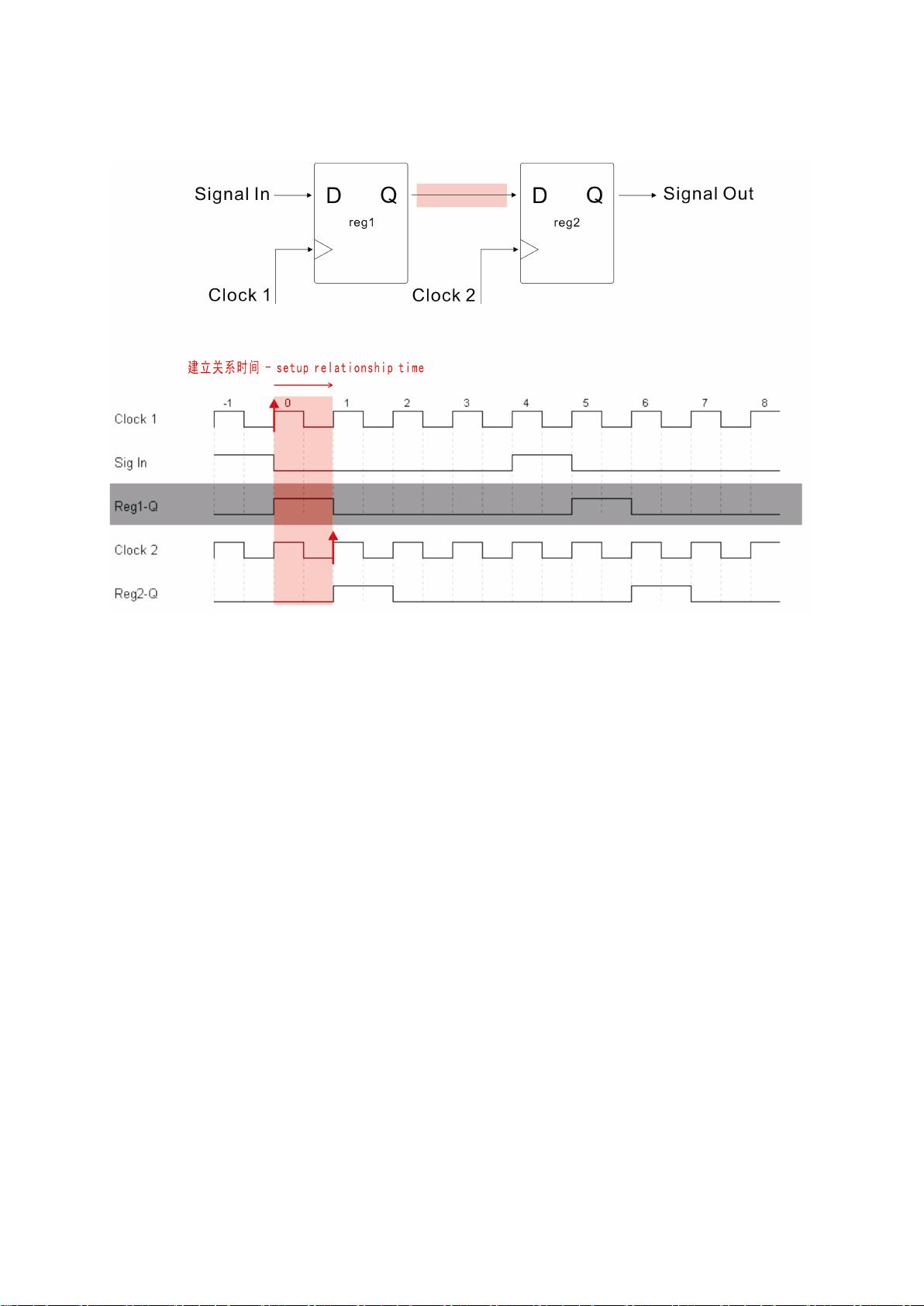

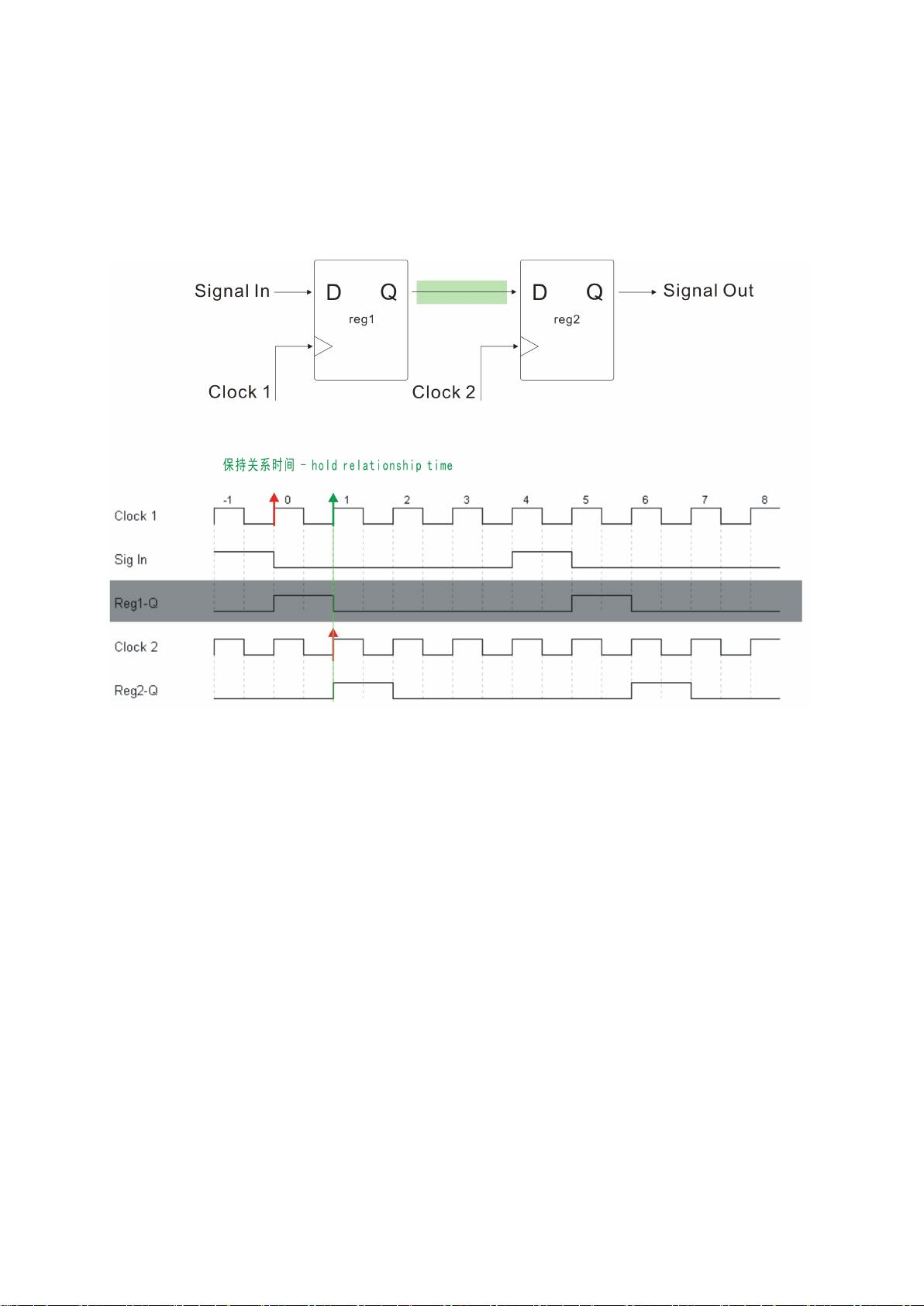

根据提供的文件信息,我们可以从中提炼出关于TimeQuest和静态时序分析的相关知识点。以下是对文件中提到概念的详细解释: 1. TimeQuest工具简介: TimeQuest是Altera公司(现为Intel旗下)Quartus II软件包中的一个工具,专门用于进行FPGA设计中的时序分析。它是一个用来确保设计满足时序要求的工具,通过分析信号在物理路径上的传输延迟,确保数据可以在时钟周期内稳定地传输。 2. 时序分析的基本概念: 时序分析是指在数字电路中,通过一系列计算和分析来确保信号在电路中的传输和处理满足时序要求的过程。TimeQuest中的时序分析关注的是物理路径上的延迟,与Verilog HDL中描述的模块间通信时序不同。Verilog HDL的时序更多关注逻辑功能的时序关系,而TimeQuest则关注信号实际在物理路径上的传播和接收。 3. 静态时序分析(STA): 静态时序分析是一种常用的时序验证方法,它通过分析电路的所有可能的路径来确定电路中最长和最短的路径延迟,以及相应的建立时间和保持时间是否满足时序要求。TimeQuest使用静态时序分析技术来评估电路设计的时序质量。 4. TimeQuest时序分析模型的基础: TimeQuest时序分析模型的基础单位是由两个节点构成的路径。这些节点通常可以被理解为寄存器,尽管这不是严格的定义。在TimeQuest模型中,信号从一个寄存器传输到另一个寄存器,并且需要消耗一个时钟周期的时间。TimeQuest分析模型的核心关注点在于数据从一个寄存器发送到另一个寄存器的路径延迟和时间要求。 5. 建立时间和保持时间: 在TimeQuest模型中,建立时间和保持时间是关键的时序参数。建立时间(Setup Time)是指在时钟信号的触发边沿到来之前,数据必须稳定出现在寄存器输入端的时间。保持时间(Hold Time)是指数据必须在寄存器输入端保持稳定的时间,以防止数据在时钟沿触发后发生改变。这两者对于确保数据在寄存器间正确传输至关重要。 6. 理想时序: 理想时序是指没有物理延迟的时序,即数据在没有经过任何逻辑门和连线延迟的情况下,从一个寄存器传输到另一个寄存器。理想时序为实际时序分析提供了一个参考框架,通过对比理想情况和实际电路中的时序,可以更容易地识别和修正时序问题。 7. 实际时序与理想时序的关系: 在实际的时序分析中,TimeQuest工具会将理想时序与实际电路的时序进行对比,来判断电路是否满足时序要求。由于存在物理延迟,实际电路的时序会比理想时序复杂得多。TimeQuest通过计算实际路径上的延迟,并与建立时间和保持时间的规格进行比较,来确保电路设计的可靠性。 8. TimeQuest分析模型的细节: TimeQuest分析模型不仅关注单个寄存器对寄存器的传输,还关注连续的数据传输过程中,一个寄存器输出到另一个寄存器输入之间的路径。这包括了时钟信号的分配、数据的传输路径以及寄存器之间的实际延迟时间。TimeQuest通过这种方式来确保整个电路在时钟周期内正确运行。 总结来说,TimeQuest是一个用于时序分析的工具,它通过静态时序分析技术来确保数字电路设计的时序完整性和稳定性。其分析模型关注的是寄存器之间的数据传输和时钟信号的关系,以及建立时间和保持时间是否得到满足。理想时序作为一种参考基准,帮助分析实际时序中的问题。通过对这些概念的理解和掌握,设计师能够有效地使用TimeQuest工具来优化FPGA设计的时序特性。

剩余27页未读,继续阅读

ximingri2017-12-03比较好的时序资料,可以看一下

ximingri2017-12-03比较好的时序资料,可以看一下 Tiy1232014-01-22很好,通俗易懂

Tiy1232014-01-22很好,通俗易懂

- 粉丝: 1

- 资源: 22

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 人和箱子检测2-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 清华大学2022年秋季学期 高等数值分析课程报告

- GEE错误集-Cannot add an object of type <Element> to the map. Might be fixable with an explicit .pdf

- 清华大学2022年秋季学期 高等数值分析课程报告

- 矩阵与线程的对应关系图

- 人体人员检测46-YOLO(v5至v9)、COCO、Darknet、TFRecord数据集合集.rar

- GEMM优化代码实现1

- java实现的堆排序 含代码说明和示例.docx

- 资料阅读器(先下载解压) 5.0.zip

- 人、垃圾、非垃圾检测18-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

信息提交成功

信息提交成功