没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

本文是作者在华为工作期间写的一篇对DDR3全面的总结,当时有好几年经常接触DDR3的设计与测试,期间总结了大量的知识点,于是业余时间汇总起来写成本文,因为DDR3属于业界通用的器件,其中知识也不涉及到公司秘密,所以分享出来供大家参考。 文章摘要: DDR,在PC、手机、通信设备等产品中广泛应用。而随着技术发展以及用户需求提高,内存不断升级,从SDRAM, DDR, DDR2、再到DDR3,现在DDR4也开始大规模应用。其特点就是速率、容量不断提高,而且性能、功耗方面也不断优化。内存技术是很多软件、硬件、逻辑、测试工程师们关注的重点。但由于其复杂程度较高,同时,英文资料复杂,理解困难,而中文资料能较全面详细描述DDR3的文献匾乏、零散。记得刚接触DDR3时真是一头雾水,一直在其表面徘徊很久。身边小伙伴也是同感。 作者所从事的硬件领域常常接触DDR,在这方面有一些难忘的经历,期间也积累了一些知识。出于经验传承的目的,特写下本文。内存已经历多代,但很多知识是相通的,本文拿当前主流的DDR3作为重点去讲解。出于能力水平及篇幅原因,本文未能周全深入描述DDR3所有特性或者某些地方存在错误,还望读者谅解和指正。同时,本书在一些地方引用了其他文献中的图文,会在相应地方加以说明。在此,衷心希望本文能给能给想了解DDR3技术的同学提供帮助。 本文分为以下八章内容: 第一章 DDR3基础 第二章 DDR硬件设计 第三章 DDR3几个关键技术 第四章DDR3工作流程、参数详解 第五章 DDR3训练 第六章 DDR3信号完整性测试 第七章 DDR3问题案例 第八章 SDRAM、DDR、DDR2、DDR3、DDR4对比

资源推荐

资源详情

资源评论

1 / 100

《DDR3 基础与进阶》

冼启源 331697625@qq.com

引言

DDR,在 PC、手机、通信设备等产品中广泛应用。而随着技术发展以及用户需求

提高,内存不断升级,从 SDRAM, DDR, DDR2、再到 DDR3,现在 DDR4 也开始大规模应

用。其特点就是速率、容量不断提高,而且性能、功耗方面也不断优化。内存技术是

很多软件、硬件、逻辑、测试工程师们关注的重点。但由于其复杂程度较高,同时,

英文资料复杂,理解困难,而中文资料能较全面详细描述 DDR3 的文献匾乏、零散。记

得刚接触 DDR3 时真是一头雾水,一直在其表面徘徊很久。身边小伙伴也是同感。

作者所从事的硬件领域常常接触 DDR,在这方面有一些难忘的经历,期间也积累

了一些知识。出于经验传承的目的,特写下本文。内存已经历多代,但很多知识是相

通的,本文拿当前主流的 DDR3 作为重点去讲解。出于能力水平及篇幅原因,本文未能

周全深入描述 DDR3 所有特性或者某些地方存在错误,还望读者谅解和指正。同时,本

书在一些地方引用了其他文献中的图文,会在相应地方加以说明。在此,衷心希望本

文能给能给想了解 DDR3 技术的同学提供帮助。

2 / 100

目 录

引言 ...................................................................................................................................................... 1

目 录 .................................................................................................................................................. 2

第一章 DDR3 基础 ................................................................................................................................... 4

1.1 DDR3 简介 ............................................................................................................................... 4

1.2 DDR3 基本概念 ....................................................................................................................... 4

1.3 DDR3 容量计算 ....................................................................................................................... 6

1.4 DDR3 内部结构 ....................................................................................................................... 7

1.5 存储单元结构 ............................................................................................................................... 8

1.6 模式寄存器简介 ......................................................................................................................... 10

第二章 DDR 硬件设计 ........................................................................................................................... 15

2.1 DDR3 管脚描述 ........................................................................................................................... 15

2.2 DDR3 原理图设计 ....................................................................................................................... 16

2.3 DDR3 PCB 设计 .......................................................................................................................... 21

第三章 DDR3 几个关键技术 .................................................................................................................... 29

3.1 ODT .............................................................................................................................................. 29

3.2 Output Driver Impedance ............................................................................................................. 32

3.3 ZQ Calibration ........................................................................................................................... 33

3.4 DLL ........................................................................................................................................... 34

3.5 预冲电 ......................................................................................................................................... 35

3.6 刷新 .............................................................................................................................................. 38

3.7 突发传输 Burst............................................................................................................................. 40

3.8 DM 数据掩码 ............................................................................................................................ 41

3.9 Write Leveling ........................................................................................................................... 42

第四章 DDR3 工作流程、参数详解 ........................................................................................................ 45

4.1 DDR3 工作流程 ........................................................................................................................... 45

4.1.1 初始化流程 ...................................................................................................................... 45

4.1.2 命令集 .............................................................................................................................. 47

4.2 DDR3 重要性能参数详解 ........................................................................................................ 50

4.2.1 tRCD 参数 ......................................................................................................................... 51

4.2.2 CL 参数 ............................................................................................................................. 51

4.2.3 CWL 参数 ......................................................................................................................... 52

4.2.4 AL 参数 .......................................................................................................................... 54

4.2.5 tRP 参数 ......................................................................................................................... 55

4.2.6 tRFC 参数 ....................................................................................................................... 55

第五章 DDR3 训练 ................................................................................................................................... 58

5.1 DDR3 训练是什么 ....................................................................................................................... 58

5.2 DDR3 训练的基本思想 ............................................................................................................... 60

5.4 Write Leveling .............................................................................................................................. 61

5.5 Data Eye Training ......................................................................................................................... 61

3 / 100

5.6 Read DQS Gate Training .............................................................................................................. 63

第六章 DDR3 信号完整性测试 ............................................................................................................. 65

6.1 信号质量测试 ............................................................................................................................. 65

6.1.1 时钟信号质量测试 .......................................................................................................... 65

6.1.2 地址、控制、数据信号质量测试 ................................................................................... 70

6.1.3 复位信号质量测试 ........................................................................................................... 73

6.2 接口时序测试 ............................................................................................................................. 73

6.2.1 AC 与 CK 时序 ................................................................................................................. 73

6.2.2 DQ 与 DQS 时序............................................................................................................... 74

6.2.3 CK 与 DQS 时序 ............................................................................................................... 76

6.2.4 复位时序 .......................................................................................................................... 77

6.2.5 ODT 时序 .......................................................................................................................... 79

6.2.6 前导 Preamble/后导 Postable ........................................................................................... 80

6.2.7 刷新周期 .......................................................................................................................... 82

6.3 泰克 DDRA 软件简介 ................................................................................................................ 82

6.4 SSN 测试 ...................................................................................................................................... 84

6.5 时序裕量测试 ............................................................................................................................. 85

6.5.1 窗口扫描 .......................................................................................................................... 85

6.5.2 VREF 拉偏+高低温四角测试 .......................................................................................... 86

第七章 DDR3 问题案例 ......................................................................................................................... 87

第八章 SDRAM、DDR、DDR2、DDR3、DDR4 对比 ..................................................................... 88

8.1 SDRAM ..................................................................................................................................... 89

8.2 DDR SDRAM............................................................................................................................... 91

8.3 DDR2 SDRAM............................................................................................................................. 93

8.4 DDR3 SDRAM............................................................................................................................. 95

8.5 DDR4 SDRAM............................................................................................................................. 97

附录及后记 .............................................................................................................................................. 100

第一章 DDR3 基础

4 / 100

第一章 DDR3 基础

1.1 DDR3 简介

DDR3 是第三代 DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access

Memory),双倍数据速据速率同步动态随机存取存储器。DDR3 是在 DDR2 的基础上发展

而来,由 JEDEC 组织于 JEDEC-79E 中制定其标准。DDR3 内部配置有 8 个 BANK,容量最

大 8Gbit。DDR3 使用 8bit 预取结构,以获得高速操作,其最高数据速率达 2133Mbps。

另外新增了复位、WriteLeveling、动态 ODT 等功能,在应用上相比 DDR2 更灵活,而

且在能效上相比以往 DRAM 也有提高。跟其他 DRAM 一样,DDR3 在系统中的作用是数据

缓存。

1.2 DDR3 基本概念

DDR DRAM

译成双倍数据速据速率同步动态随机存取存储器。

双倍数据速率是指着其数据信号 DQ 由 DQS 时钟上升、下降沿采样来说的,即一个

时钟周期内传输两次数据。这也是与早期 SDR (Single Data Rate) SDRAM 的重要区

别,SDR SDRAM 在一个时钟周期内只传输一次数据,它是在时钟的上升沿采样的。

同步是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以时钟为基

准,由时钟边沿去采样即为同步。

而动态是指 DRAM 需要周期地刷新(给存储电容充电)从而使电容保存的信息不丢

失。DDR 至少 64ms 整体刷新一次。而 DDR 读取操作也会使存储电容的电量丢失(在后

面讲到存储单元结构时会解释),因此每次读操作后也需要有一个回写(刷新)操作。

随机访问是指的是当存储器中的消息被读取或写入时,所需要的时间与这段信息

所在的位置无关。相对的,读取或写入顺序访问(Sequential Access)存储设备中的

信息时,其所需要的时间与位置就会有关系。随机访问带来的特点就是读写速度快。

Bank

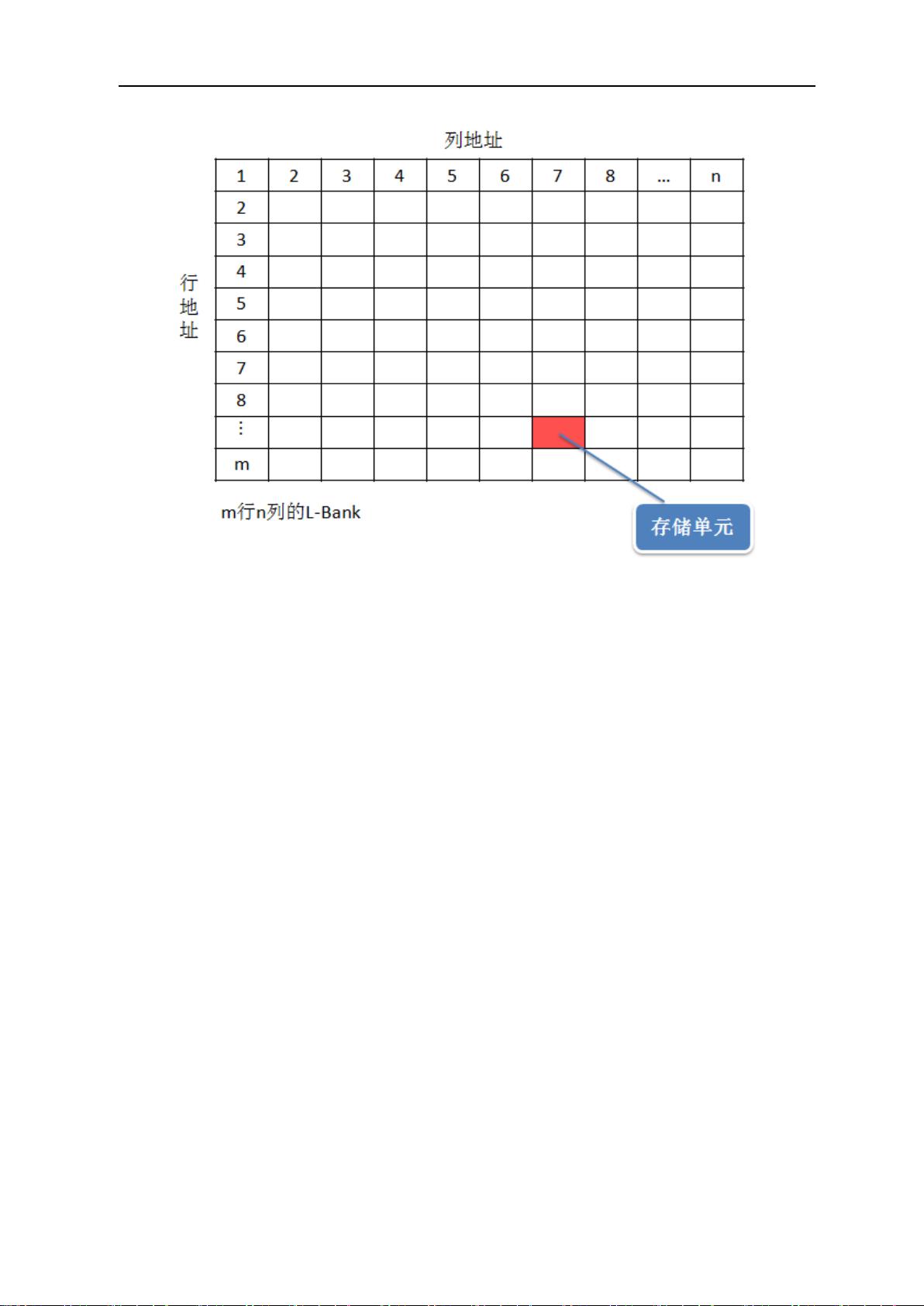

逻辑 BANK(Logical Bank,L-Bank): SDRAM 的内部是一个存储阵列。阵列就如同

表格一样,将数据“填”进去,你可以把它想象成一张表格。单一的 L-Bank 将会造成

非常严重的寻址冲突(在后文“增加 PHR 方法”中讲到),大幅降低内存效率,所以人

们在内部分割成多个 L-Bank。逻辑 BANK 是针对内存颗粒内部 Rank 说的。

第一章 DDR3 基础

5 / 100

图 1-1 m 行 n 列的 L-Bank 示意图

物理 BANK (Phisical Bank,P-Bank)

把一组内存颗粒集合起来,拼成处理器需要的数据位宽,这样的结构就是物理

BANK。也有资料把物理 BANK 叫做 RANK。传统内存系统为了保证 CPU 的正常工作,必

须一次传输完 CPU 在一个传输周期内所需要的数据。那时的内存必须要组织成 P-Bank

来与 CPU 打交道,所以会出现两根 32 位的内存搭配才能跟 64 位的奔腾 CPU 开机成功。

位宽

芯片位宽是指 DDR 颗粒数据线数量。而通常为了组成 P-Bank 所需的位宽,就需要

多颗芯片拼接使用。比如,如果需要组成 64bit,对于 16bit 芯片,需要 4 颗芯片。

对于 8bit 芯片,则就需要 8 颗了。

行/列地址

要指定 DDR3 的一个具体存储单元,除了需要指定具体 Bank 之外,还需要指定具

体 Bank 中的哪一行、哪一列。该任务就是行/列地址译码选择出来的。

DDR3 的行、列地址是复用管脚的,具体操作时先指定行地址(行地址与 Bank 地

址同一时钟周期选择的), 等待一定时间(tRCD)后.再指定列地址(列址指与读写命令同

一时钟周期)。具体操作在后面章节会讲。

剩余99页未读,继续阅读

资源评论

王同学的时间2021-04-11资料非常有用,华为内部资料,存储器phy接口写的很清晰

王同学的时间2021-04-11资料非常有用,华为内部资料,存储器phy接口写的很清晰 西兰花蛋花汤2023-01-06太感谢了,冼工对DDR3理解的非常系统和透彻,帮助很大。

西兰花蛋花汤2023-01-06太感谢了,冼工对DDR3理解的非常系统和透彻,帮助很大。

冼工

- 粉丝: 9

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Tensorflow的深度学习全部资料+详细文档+优秀项目.zip

- 基于tensorflow的人脸识别全部资料+详细文档+优秀项目.zip

- 基于Tensorflow的中文分词模型全部资料+详细文档+优秀项目.zip

- 基于tensorflow的智能作曲全部资料+详细文档+优秀项目.zip

- 基于Tensorflow的文本内容安全审核全部资料+详细文档+优秀项目.zip

- 基于tensorflow对Marcel静态手势库进行手势识别全部资料+详细文档+优秀项目.zip

- 基于tensorflow的中文文本分类(复旦中文语料)全部资料+详细文档+优秀项目.zip

- 基于TensorFlow的自动化行人检测(人体检测)和监控(视频监控)系统全部资料+详细文档+优秀项目.zip

- 基于Tensorflow和Flask的衣服识别小工具全部资料+详细文档+优秀项目.zip

- 基于tensorflow基于CTPN+Densenet实现的中文文本检测和识别全部资料+详细文档+优秀项目.zip

- 基于TensorFlow和Keras的智能垃圾分类系统,全部资料+详细文档+优秀项目.zip

- 基于tensorflow深度学习的中文的命名实体识别全部资料+详细文档+优秀项目.zip

- 基于TensorFlow进行的视频图像转化照片风格转换全部资料+详细文档+优秀项目.zip

- 企业数字化转化-非结构化数据解决方案 ppt

- 游戏人物检测29-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 基于TensorFlow实现CNN水果检测全部资料+详细文档+优秀项目.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功