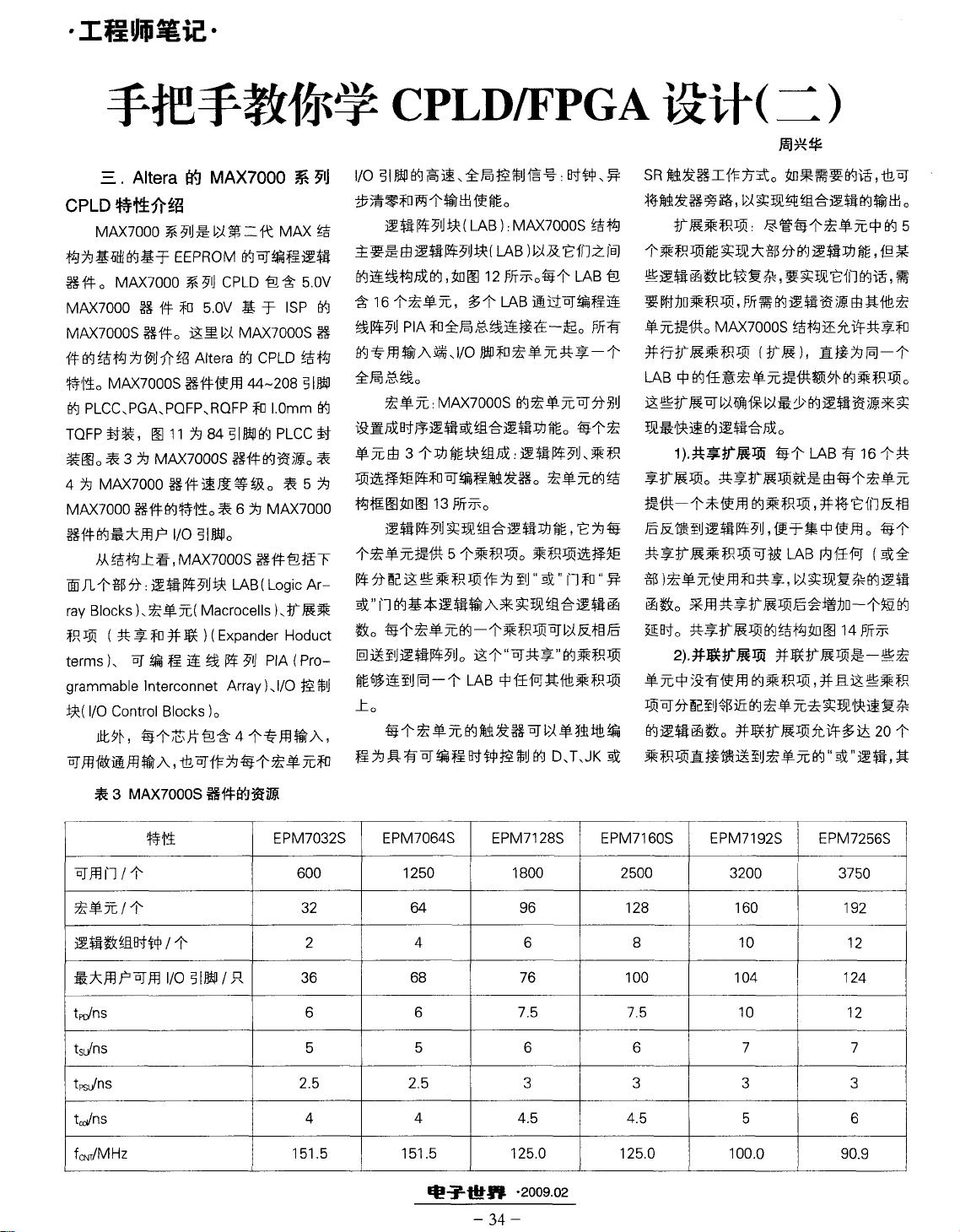

**CPLD/FPGA 学习精粹:深入探索 Altera 的 MAX7000 系列 CPLD** 在IT领域,尤其是电子工程与集成电路设计中,CPLD(复杂可编程逻辑器件)与FPGA(现场可编程门阵列)是不可或缺的关键技术。本文将重点解析Altera的MAX7000系列CPLD,这是一款基于EEPROM的可编程逻辑器件,以其强大的灵活性和可编程性,在电子系统设计中占据了一席之地。 ### MAX7000系列CPLD概述 MAX7000系列是基于第二代MAX结构,采用EEPROM作为存储介质的CPLD。该系列分为5.0V的MAX7000和5.0V的基于ISP(In-System Programming)的MAX7000S器件。其中,MAX7000S以其卓越的性能和广泛的封装选项,如PLCC、PGA、PQFP、RQFP和1.0mm的TQFP,成为了许多工程师的首选。 ### MAX7000S的结构特性 MAX7000S的内部结构复杂而精密,主要由以下几个关键组件构成: 1. **逻辑阵列块(LABs)**:这是MAX7000S的核心,每个LAB包含16个宏单元,多个LAB通过可编程连线阵列(PIA)和全局总线相互连接,形成一个高度集成的逻辑网络。 2. **宏单元(Macrocells)**:宏单元是实现时序逻辑和组合逻辑功能的基础,由逻辑阵列、乘积项选择矩阵和可编程触发器三个部分组成。每个宏单元可以独立配置为D、T、JK或SR触发器,以满足不同的设计需求。 3. **扩展乘积项**:为了处理更复杂的逻辑函数,MAX7000S提供了共享和并联扩展乘积项。共享扩展项利用未使用的乘积项增强LAB内的逻辑功能,而并联扩展项则直接为宏单元提供额外的乘积项,优化逻辑合成过程。 4. **可编程连线阵列(PIA)**:PIA负责连接不同的LAB和宏单元,实现灵活的信号路由,是实现CPLD高密度和高性能的关键。 5. **I/O控制块**:用于管理和控制芯片与外部系统的接口,包括时钟、异步清零和输出使能等全局控制信号。 ### MAX7000S的资源与性能 根据表3,MAX7000S系列CPLD提供了丰富的资源,如EPM7032S至EPM7256S型号分别拥有600至3750个可用门,32至192个宏单元,以及2至12个逻辑数组时钟。同时,表4显示了不同速度等级下的器件性能,例如,EPM7032S的速度等级从-5到-20不等,满足了从高速到低速的各种应用需求。 ### 结论 Altera的MAX7000系列CPLD,以其卓越的性能、丰富的资源和灵活的编程能力,为电子系统设计带来了前所未有的便利性和创新空间。无论是对于初学者还是资深工程师,掌握MAX7000系列CPLD的设计和应用,都将极大地提升他们在数字电路设计领域的专业技能和项目成功率。通过深入了解MAX7000S的结构特性与性能参数,工程师们可以更好地利用这一强大工具,创造出更加高效、稳定且功能丰富的电子系统。

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 会使用到的js文件词云图

- 会使用到的json数据

- 车辆、飞机、船检测12-YOLO(v5至v11)、COCO、CreateML、TFRecord、VOC数据集合集.rar

- 基于STM32单片机的WIFI输液控制APP系统.zip

- 基于STM32单片机的WIFI智能温室大棚APP系统设计.zip

- 基于Java的坦克游戏设计与实现

- 车辆、飞机、桥、人、船、储罐、风车检测25-YOLO(v5至v8)、COCO、CreateML数据集合集.rar

- 西门子EPOS效率倍增-伺服驱动功能库详解-简易非循环功能库之EPOS程序段读写.mp4

- windows鼠标美化

- 基于python-CNN深度学习识别10种蔬菜-含5000张以上的图片.zip

信息提交成功

信息提交成功