没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

80页

第六章、FPGA应用开发实例 4 6.1 如何克服FPGA I/O引脚分配挑战 4 6.2 用 Xilinx XtremeDSP 视频入门套件加速 FPGA 上的视频开发 10 6.3用 Spartan-3A DSP 器件实现汽车应用中的块匹配 14 6.4 利用 CoolRunner-II CPLD 设计 GPS 系统 20 6.5 利用赛灵思 EDK工具和IP设计多处理器SOC 23 6.6 利用JTAG链进行更为精确的系统级和芯片级功率分析和热分析 27 6.7 识别和解决赛灵思FPGA设计中的时序问题 34 第七章、FPGA设计百问 40 第八章、FPGA开发资源总汇 78 第九章、编委信息与后记 79 第十章、版权声明 80

资源推荐

资源详情

资源评论

《电子工程师创新设计必备宝典系列之FPGA开发全攻略》

FPGA开发全攻略

—

工程师创新设计宝典

下册

技巧篇

2009年2月 1.0版

2.

FPGA开发全攻略

—

工程师创新设计宝典

下册 技巧篇

前言

2008年,我参加了几次可编程器件供应商举办的技术研讨会,让我留下深刻印象的是

参加这些研讨会的工程师人数之多,简直可以用爆满来形容,很多工程师聚精会神地全天听

讲,很少出现吃完午饭就闪人的现象,而且工程师们对研讨会上展出的基于可编程器件的通

信、消费电子、医疗电子、工业等解决方案也有浓厚的兴趣,这和其他器件研讨会形成了鲜

明的对比。

Garnter和iSuppli公布的数据显示:2008年,全球半导体整体销售出现25年以来首次

萎缩现象,但是,可编程器件却还在保持了增长,预计2008年可编程逻辑器件(PLD)市场销

售额增长7.6%,可编程器件的领头羊美国供应商赛灵思公司2008年营业收入预计升6.5%!

在全球经济危机的背景下,这是非常骄人的业绩!也足见可编程器件在应用领域的热度没有

受到经济危机的影响!这可能也解释了为什么那么多工程师对可编程器件感兴趣吧。

在与工程师的交流中,我发现,很多工程师非常需要普及以FPGA为代表的可编程器

件的应用开发知识,也有很多工程师苦于进阶无门,缺乏专业、权威性的指导,在Google

上搜索后,我发现很少有帮助工程师设计的FPGA电子书,即使有也只是介绍一些概念性的

基础知识,缺乏实用性和系统性,于是,我萌生了出版一本指导工程师FPGA应用开发电子

书的想法,而且这个电子书要突出实用性,让大家都可以免费下载,并提供许多技巧和资源

信息,很高兴美国赛灵思公司对这个想法给予了大力支持,赛灵思公司亚太区市场经理张俊

伟小姐和高级产品经理梁晓明先生对电子书提出了宝贵的意见,并提供了大量FPGA设计资

源,也介绍了一些FPGA设计高手参与了电子书的编撰,很短的时间内,一个电子书项目团

队组建起来,北京邮电大学的研究生田耘先生和赛灵思公司上海办事处的苏同麒先生等人都

参与了电子书的编写,他们是有丰富设计经验的高手,在大家的共同努力下,这本凝结着

智慧的FPGA电子书终于和大家见面了!我希望这本电子书可以成为对FPGA有兴趣或正在

使用FPGA进行开发的工程师的手头设计宝典之一,也希望这个电子书可以对工程师们学习

FPGA开发和进阶有实用的帮助!如果可能,未来我们还将出版后续版本!

张国斌

电子书主编

2009年2月25日

3.

FPGA开发全攻略

—

工程师创新设计宝典

下册 技巧篇

目录

前言 2

第六章、FPGA应用开发实例

4

6.1 如何克服FPGA I/O引脚分配挑战 4

6.2 用 Xilinx XtremeDSP 视频入门套件加速 FPGA 上的视频开发

10

6.3用 Spartan-3A DSP 器件实现汽车应用中的块匹配

14

6.4 利用 CoolRunner-II CPLD 设计 GPS 系统

20

6.5 利用赛灵思 EDK工具和IP设计多处理器SOC

23

6.6 利用JTAG链进行更为精确的系统级和芯片级功率分析和热分析

27

6.7 识别和解决赛灵思FPGA设计中的时序问题

34

第七章、FPGA设计百问 40

第八章、FPGA开发资源总汇

78

第九章、编委信息与后记

79

第十章、版权声明

80

4.

FPGA开发全攻略

—

工程师创新设计宝典

下册 技巧篇

第六章、FPGA应用开发实例

6.1 如何克服 FPGA I/O 引脚分配挑战

作者:Brian Jackson

产品营销经理Xilinx, Inc.

brian.jackson@xilinx.com

对于需要在 PCB 板上使用大规模 FPGA 器件的设计人员来说,I/O 引脚分配是必须面对的众多挑战之一。

由于众多原因,许多设计人员发表为大型 FPGA 器件和高级 BGA 封装确定 I/O 引脚配置或布局方案越来越困难。

但是组合运用多种智能 I/O 规划工具,能够使引脚分配过程变得更轻松。

在 PCB 上定义 FPGA 器件的 I/O 引脚布局是一项艰巨的设计挑战,即可能帮助设计快速完成,也有可能造

成设计失败。 在此过程中必须平衡 FPGA 和 PCB 两方面的要求,同时还要并行完成两者的设计。 如果仅仅针

对 PCB 或 FPGA 进行引脚布局优化,那么可能在另一方面引起设计问题。

为了解引脚分配所引起的后果,需要以可视化形式显示出 PCB 布局和 FPGA 物理器件引脚,以及内部

FPGA I/O 点和相关资源。 不幸的是,到今天为止还没有单个工具或方法能够同时满足所有这些协同设计需求。

然而,可以结合不同的技术和策略来优化引脚规划流程并积极采用 Xilinx

®

PinAhead 技术等新协同设计工

具来发展出一套有效的引脚分配和布局方法。 赛灵思公司在 ISE™ 软件设计套件 10.1 版中包含了 PinAhead。

赛灵思公司开发了一种规则驱动的方法。首先根据 PCB 和 FPGA 设计要求定义一套初始引脚布局,这样利

用与最终版本非常接近的引脚布局设计小组就可以尽可能早地开始各自的设计流程。 如果在设计流程的后期由

于 PCB 布线或内部 FPGA 性能问题而需要进行调整,在采用这一方法晨这些问题通常也已经局部化了,只需要

在 PCB 或 FPGA 设计中进行很小的设计修改。

步骤1: 评估设计参数

那么,从哪里开始呢? 首先应当尽早制定 I/O 分配策略。 但没有优化工具或完整的网表,完成这一任务可

能很困难。

5.

FPGA开发全攻略

—

工程师创新设计宝典

下册 技巧篇

首先,让我们先回答几个问题来确定 PCB 物理参数和限制 :

PCB 板有几层、走线宽度以及过孔尺寸多大?

PCB 参数对可使用的 FPGA 封装类型 ( 如 BGA) 有限制吗?

PCB 上有没有 FPGA 必须使用的固定接口位置? 其它芯片、连接器或布局限制?

哪些高速接口需要特别关注?

能否将布局策略可视化,从而保证最短互连?

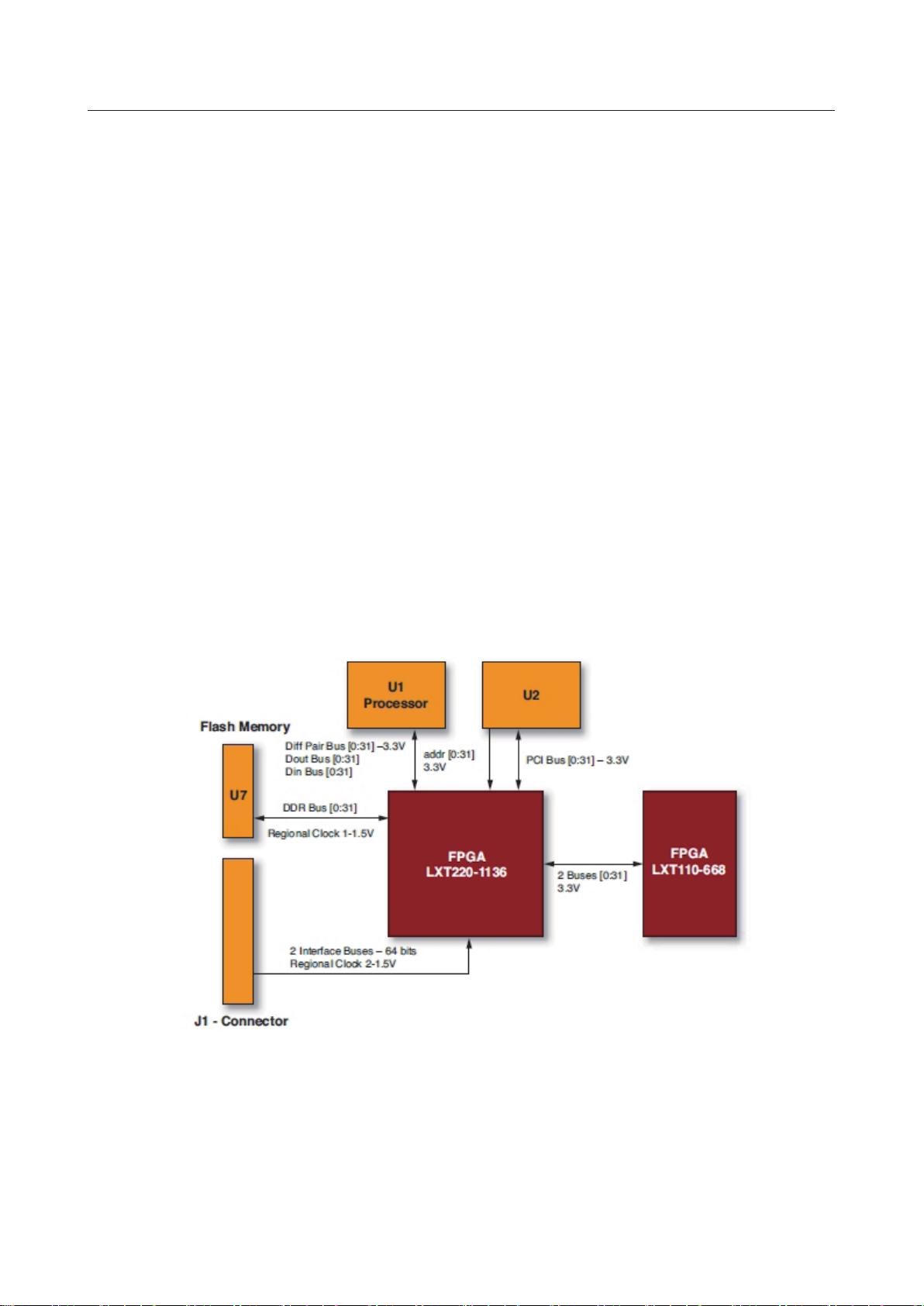

你会发现画一张 PCB 布局图很有帮助。PCB 布局图上应当包括所有主要元器件以及关键接口和总线,从

而可以帮助确定最佳的 FPGA 引脚分配。 请注意将元器件画在 PCB 板的实际安装面上。 标注出需要特别关注

的接口,如高速总线和差分对 ( 图 1)。

下一步,检查 FPGA 器件的布局来了解芯片上的物理资源所在。 列出设计中使用的不同电压和时钟,开始

隔离设计需要的接口。 然后确定设计是否使用特殊的 I/O 接口资源,如千兆收发器 (GT)、BUFR、IODELAY 以

及数字时钟管理器。这些资源可能需要将有关的 I/O 引脚布署得尽量互相靠近。

现在需要确定设计中使用的 PowerPC™、DSP48 和 RAM16 等 FPGA 资源的位置。 将连接到 I/O 组的任何

相关 I/O 尽量置于尽相关资源最近的地方。 然后看一下能否将某些 I/O 信号组合到接口,这对于引脚分配很有

帮助。 最后,确定 FPGA 的配置模式。

图6-1 PCB连接图

步骤2: 定义引脚布局要求

一旦了解了主要的 FPGA 接口并创建了物理布局的原型,就可以定义引脚布局了。 有些设计人员喜欢使用

包含所有 I/O 信号数据表来保持与引脚的对应。 你可以按电压、时钟、接口或总线对它们进行分组。 这一方法

剩余79页未读,继续阅读

资源评论

xbjj2010

- 粉丝: 36

- 资源: 10

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功