wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- MATLAB代码:考虑V2G的光储充一体化微网多目标优化调度策略 关键词:光储充微网 电电汽车V2G 多目标优化 蓄电池优化 调度 参考文档:光伏微网下考虑V2G补偿蓄电池容量的双目标优化调度策略

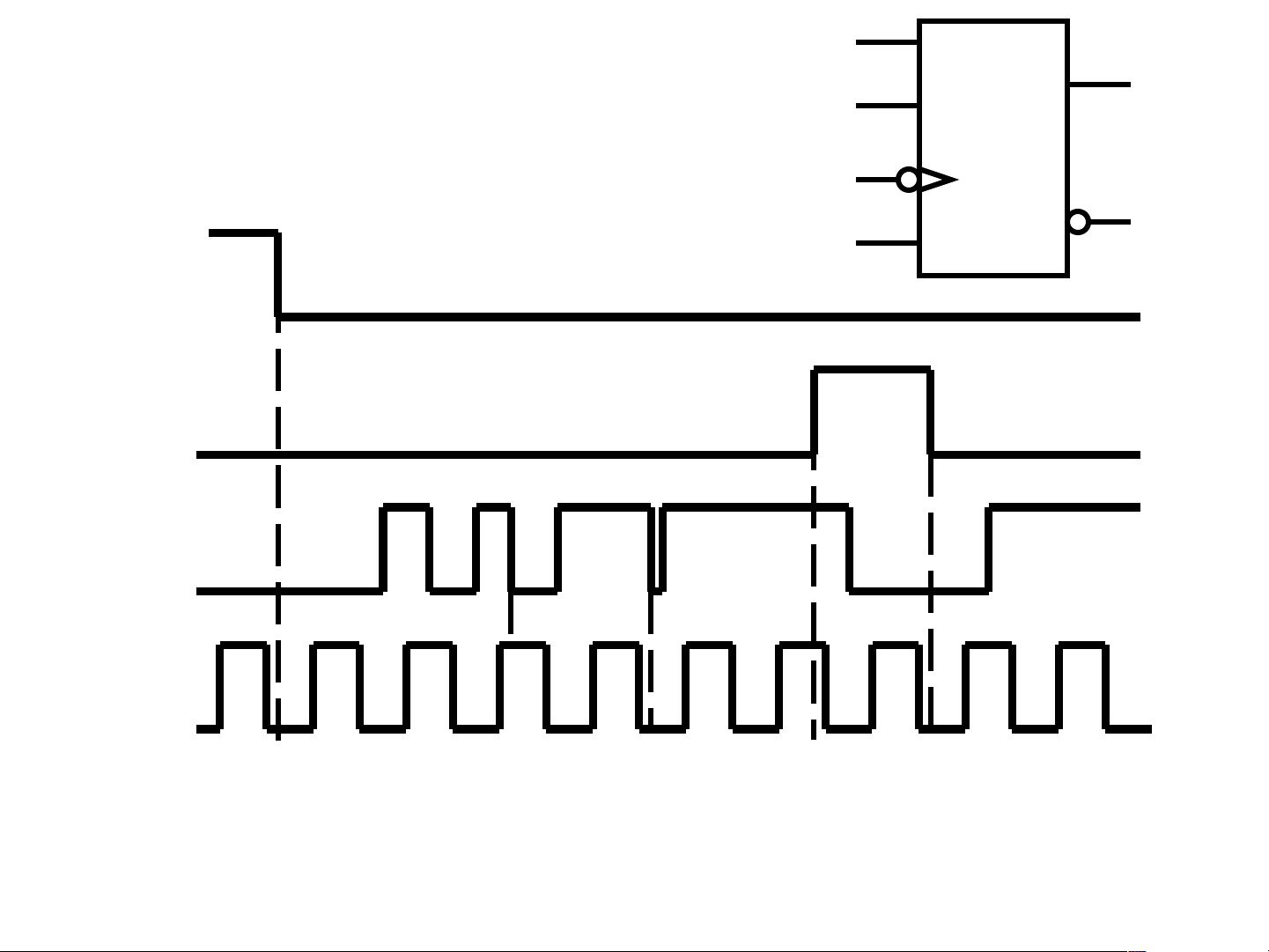

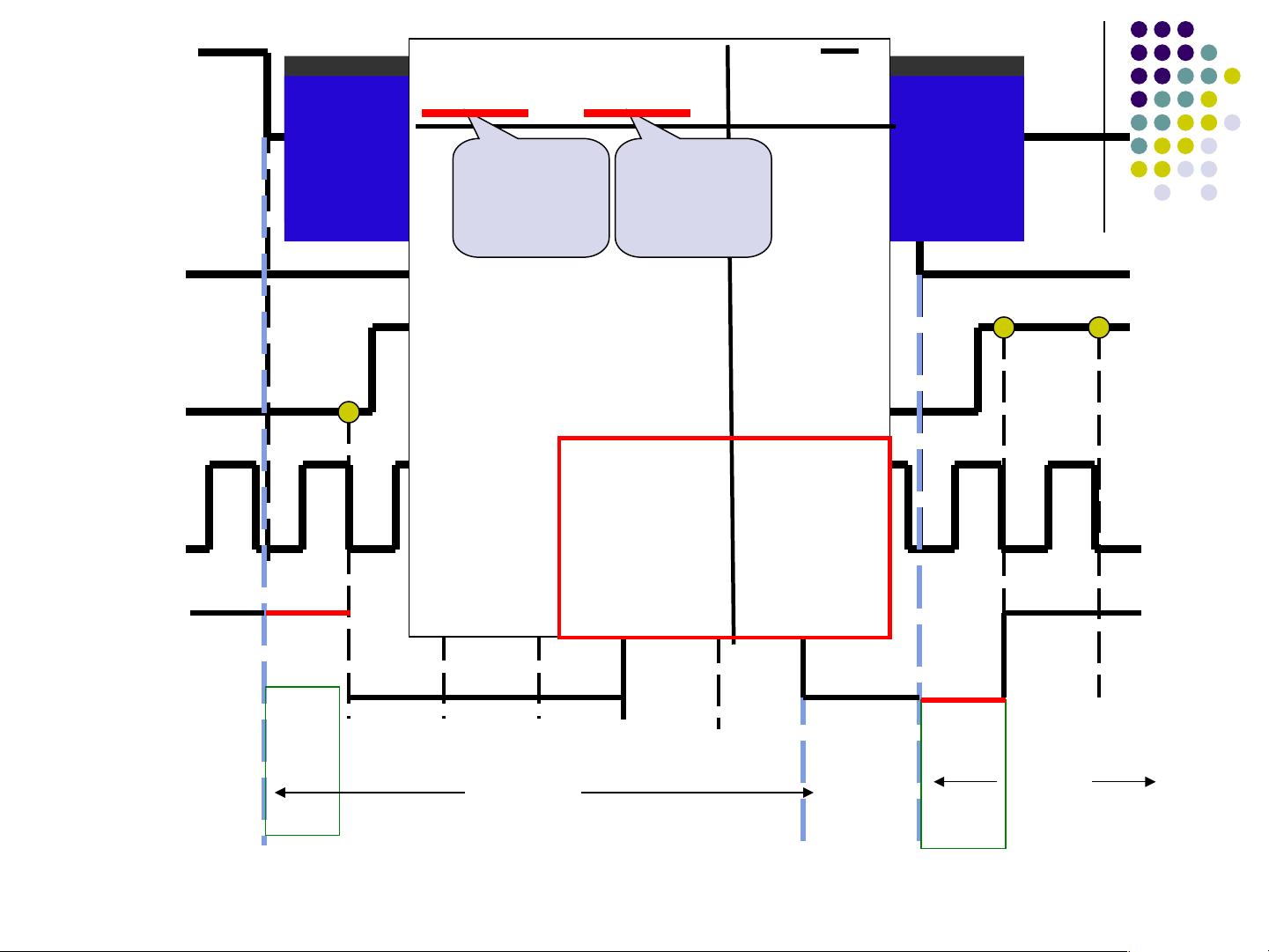

- 逆变器仿真 在simulink中搭建了逆变器仿真模型,采用电压电流双闭环前馈解耦控制,采用LC滤波器,输出电压完美的跟随给定,且THD仅1% 整个仿真全部离散化,采用离散解析器,离散PI,控制与采

- 单相逆变器重复控制 采用重复控制与准比例谐振控制相结合的符合控制策略,spwm调制环节采用载波移相控制,进一步降低谐波 仿真中开关频率20k,通过FFT分析,谐波主要分布在40k附近,并没有分布在

- 纯电动汽车Simulink模型;混合动力汽车Simulink模型;染料电池电动汽车Simulink模型 纯电动汽车模型: 制动优先;充电禁止车辆驱动;驱动控制;再生能量回收;紧急停机功能;

- 三菱FX系列FX2N-4AD-PT模拟量控制程序 三菱FX系列FX2N-4AD-PT模拟量控制程序 三菱温度模块,采用FX2N-4AD-PT模拟量模块,由TO FROM应用指令来完成 FX

- 三菱步进电机驱动器控制的定位案例,带有触摸屏程序,plc程序 程序功能实现正反转控制,原点回归,急停报警等 触摸屏有报警显示,故障历史这些常用的画面设置,对控制多轴运动很有帮助,值得去学习一下

- 时间排序启动电机(阀门)功能块 博图程序 多电机均匀 SCL功能块,博图16编写,时间排序启动功能块,scl语言,可用于各种泵站,水处理工况,通过比较运行时间,选择启动最短时间的几台泵,启动泵的台数可

- 西门子plc动态加密计时催款程序 西门子plc编程、面对设备调试完成后迟迟不肯付款的和找各种理由拒绝搪塞验收的客户,必须的采取非常的手段,其中给设备加密定时锁机是一种优选的方案 一来可以提醒

- 卡尔曼滤波四元数姿态角仿真程序,EKF,UKF算法对比,附带C语言压缩包 新增完整的单片机UKF实验项目代码 基于stm32h750+mpu9250+w25q64实现串口输出姿态角度和保存校准参数

- 无感Foc控制 滑模观测器smo 永磁同步电机正弦波控制方案 直流无刷电机 提供stm32 和 dsp源码 提供keil完整工程,不是st电机库 对电机参数不敏感,50%误差依然控制稳定

- 永磁同步电机无感foc 磁链观测器 位置估算源码 正弦波控制方案 直流无刷电机无感foc源码,无感foc算法源码 1 速度估算位置估算的代码所使用变量全部用实际值单位,能非常直观的了解无感控制电机模

- javaShop JAVA版多用户B2B2C商城源码(PC+H5+小程序+APP) 友情提示:此源码需要有java基础的开发人员 JAVA版多用户B2B2C商城源码(PC+H5+小程序+APP) 商

- LabVIEW编写的键盘模块,可移植,源码转出,Ni LabVIEW触摸键盘

- 成熟可量产变频器方案,变频器生产方案, 变频器源码, 变频器方案, 伺服方案, 伺服源码, 伺服代码, 运动控制器源码, 伺服驱动器方案,变频器电路图 由于内容较多,请耐心读完,说不定有你喜欢的

- 小波强制滤波分析的一个demo;对信号进行sym2的两层小波分解,分解后获取信号的低频高频系数,将高频置为0得到重构信号 将重构信号与原始信号求差值,进行正态检验,如果符合正态分布,可以求取差值信号

- 三菱FX自由口通讯程序 三菱FX系列自由口通讯程序 利用FX3U-232BD与上位机自由口通讯, 有PLC程序和触摸屏程序,通过连接三根线即可通讯 具有很好的学习意义和借鉴价值

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈