没有合适的资源?快使用搜索试试~ 我知道了~

Users\Administrator\Desktop\AR8031.pdf

需积分: 10 2 下载量 44 浏览量

2020-04-03

13:52:57

上传

评论

收藏 1.17MB PDF 举报

温馨提示

ar8031硬件手册,品牌高通的,支持千兆,百兆,还有各种以太网接口,目前常用的主流型号,大家来下载吧

资源推荐

资源详情

资源评论

COMPANY CONFIDENTIAL • 1

Data Sheet

© 2011 by Atheros Communications, Inc. All rights reserved. Atheros®, Atheros Driven®, Align®, Atheros XR®, Driving the Wireless Future®, Intellon®, No New Wires®,

Orion® , PLC4Trucks®, Powerpacket®, Spread Spectrum Carrier®, SSC®, ROCm®, Super A/G®, Super G®, Super N®, The Air is Cleaner at 5-GHz®, Total 802.11®, U-

Nav®, Wake on Wireless®, Wireless Future. Unleashed Now.®, and XSPAN®, are registered by Atheros Communications, Inc. Atheros SST™, Signal-Sustain Technology™,

Ethos™, Install N Go™, IQUE™, ROCm™, amp™, Simpli-Fi™, There is Here™, U-Map™, U-Tag™, and 5-UP™ are trademarks of Atheros Communications, Inc. The

Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders. Subject to change without notice.

August 2011

Version 1.1

AR8031 Integrated 10/100/1000 Mbps Ethernet

Transceiver

General Description

The AR8031 is part of the Arctic family of

devices — which includes the AR8031, AR8033,

and AR8035. The AR8031 is Atheros’ 4

th

generation, single port, 10/100/1000 Mbps, Tri-

speed Ethernet PHY. It supports both RGMII

and SGMII interfaces to the MAC.

The AR8031 provides a low power, low BOM

(Bill of Materials) cost solution for

comprehensive applications including

enterprise, carrier and home networks such as

CPE, home gateway, enterprise switch, carrier

switch/router, mobile base station and base

station controller, optical module and media

converter, industry automation and

measurement.

The AR8031 integrates Atheros Green ETHOS

®

power saving technologies and significantly

saves power not only during the work time,

but also overtime. Atheros Green ETHOS

®

power savings include ultra-low power in

cable unplugged mode or port power down

mode, and automatic optimized power saving

based on cable length. The AR8031 also

supports IEEE 802.3az EEE standard (Energy

Efficient Ethernet) and Atheros proprietary

SmartEEE. SmartEEE allows legacy MAC/SoC

devices without 802.3az support to function as

a complete 802.3az system. Further, the AR8031

supports Wake-on-LAN (WoL) feature to be

able to help manage and regulate total system

power requirements.

The AR8031 embeds CDT (Cable Diagnostics

Test) technology on-chip which allows

customers to measure cable length, detect the

cable status, and identify remote and local PHY

malfunctions, bad or marginal patch cord

segments or connectors. Some of the possible

problems that can be detected include opens,

shorts, cable impedance mismatch, bad

connectors, termination mismatch, and a bad

transformer.

The AR8031 requires only a single, 3.3V power

supply. On-chip regulators provide all the

other required voltages. It integrates the

termination R/C circuitry on both the MAC

interfaces (RGMII/SGMII) and the serial

resistors for the line side.

The AR8031 device also incorporates a 1.25

GHz SerDes. This interface can be connected

directly to a fiber-optic transceiver for 1000

BASE-X /100 BASE-FX mode or to MAC

device for SGMII interface.

The AR8031 supports both 1588v2 and

synchronous Ethernet to offer a complete time

synchronization solution to meet the next

generation network requirements. The key new

features supported by the device are:

n Clock synchronization between slave and

grandmaster by the exchange of PTP

packets. Supports IEEE 1588v2 by offering a

1588 paket parser, accurate time-stamping

and insertion to support both one-step and

two-step clock modes

n Supports both IEEE 1588v2 and

Synchronous Ethernet by offering recovered

clock output from data on the network-line

side.

The AR8031 supports IEEE 802.3az Energy

Efficient Ethernet (EEE) standard. The key

features supported by the device are:

n 10 BASE-Te PHY uses reduced transmit

amplitude.

n 100 BASE-TX and 1000 BASE-T use Low

Power Idle (LPI) mode to turn off unused

analog and digital blocks to save power

while data traffic is idle.

Features

n 10/100/1000 BASE-T IEEE 802.3 compliant

n Supports 1000 BASE-T PCS and auto-

negotiation with next page support

n Supports RGMII and/or SGMII interfaces

to MAC devices

n Supports Fiber and Copper combo mode

when MAC interface works in RGMII mode

n Supports additional IEEE 1000 BASE-X and

100 BASE-FX with Integrated SerDes

n RGMII timing modes support internal delay

and external delay on Rx path

2 • AR8031 Integrated 10/100/1000 Mbps Ethernet Transceiver Atheros Communications, Inc.

2 • August 2011 COMPANY CONFIDENTIAL

n Supports Atheros Green ETHOS

®

power

saving modes with internal automatic DSP

power saving scheme

n Supports IEEE 802.3az (Energy Efficient

Ethernet)

n Supports SmartEEE which allows MAC/

SoC devices withoug 802.3az support to

function as the complete 802.3az system

n Supports Wake-on-LAN (WoL) to detect

magic packet and notify the sleeping system

to wake up

n Fully integrated digital adaptive equalizers,

echo cancellers, and Near End Crosstalk

(NEXT) cancellers

n Supports Synchronous Ethernet with

selectable recovered clock output

n Robust Cable Discharge Event (CDE)

protection of ±6 kV

n Error-free operation over up to 140 meters

of CAT5 cable

n Automatic channel swap (ACS)

n Automatic MDI/MDIX crossover

n Automatic polarity correction

n IEEE 802.3u compliant Auto-Negotiation

n Jumbo Frame support up to 10KB (full

duplex)

n Multiple loopback modes for diagnostics

n Robust Surge Protection with ±750 V/

differential mode and ±4 kV/common

mode

n Cable Diagnostic Test (CDT)

n Single power supply: 3.3V, optional for

external regulator for core voltage

n 6mm x 6mm, 48-pin QFN package

n Industry temperature (I-temp) option

available.

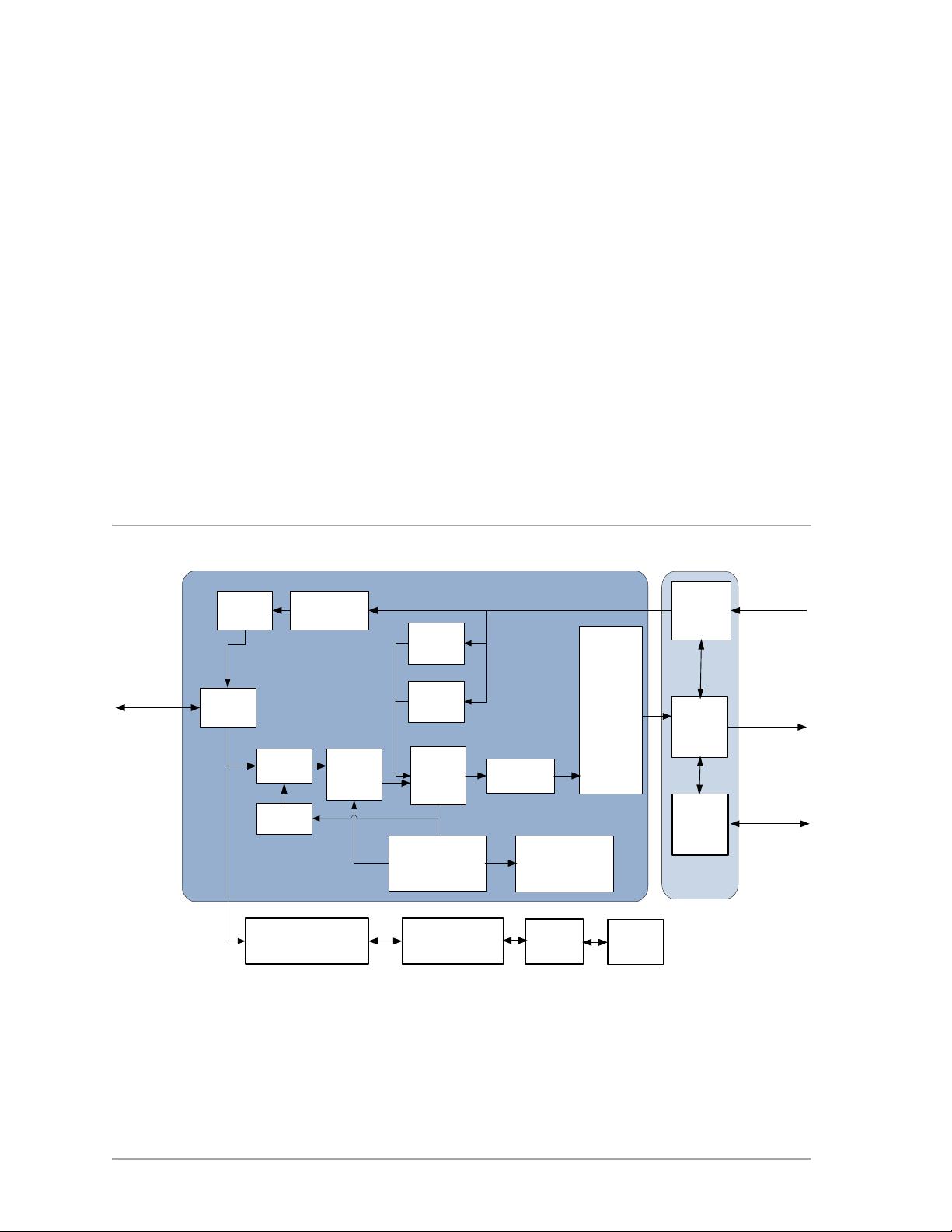

AR8031 Functional Block Diagram

DAC

Waveshape

Filter

Echo

Canceller

Next

Canceller

Hybrid

Circut

PGA

Feed

Forward

Equalizer

ADC

AGC

Timing and

Phase

Recovery

Deskewer

Decision

Feedback

Equalizer

Symbol

Encoder

Symbol

Decoder

Auto-

Negotiation

MII Management

Registers

DLL

TRD[0:3]

SGMII/

SerDes

PMA

PCS

Trellis

Decoder

RGMII

Serial

Interface

1588v2

RGMII

Sync-E

Atheros Communications, Inc. AR8031 Integrated 10/100/1000 Mbps Ethernet Transceiver • 3

COMPANY CONFIDENTIAL August 2011 • 3

Revision History

Date Revsion Details Revision

2010/11/15 First draft 0.1

2011/4/14 General Description

n Overall update for revision from MPW to mass production

n Block diagram: add SYNC-E and 1588v2 block

Pin Descriptions

n RXD [3:0], RX_DV pin damping resistor 22ohm requirement is deleted.

n RST pin type change from "IH" to "I,” mass production chip does not have

internal weak PU

n INT, WOL_INT from "I/O active high" change to "D active low" need an

external PU

n Power on strapping LED_ACT from "1.1V/1.2V selection" to "PHY

ADDRESS [2]".

n LED_ACT/LED_LINK1000/LED_LINK10_100 from internal weak "PD"

change to internal weak "PU".

Functional Descriptions

n 2.2.4 Mode definition adds work mode"1011" combo mode.

Electrical Characteristics

n 3.1 Absolute Maximum Rating: update CDM max

n 3.2 Recommeded Operating Condition: update Tj max

n 3.7 Clock Characteristics: update values in Table 3-13 Recommended Crystal

Parameters

n Update Table 3-11 MDIO AC Characteristic to add tmdelay row

Register

n 4.2.29LED Control (0x18): update register bit definitions

n 4.2.30 Manual LED Override (0x19): new register

Topside Marking

n Add topside marking illustration

1.0

2011/8/29 Electrical Characteristics

n 3.2 Recommended Operation Conditions: delete DVDDL/AVDDL,

JA

; add

VDDH_REG,

JT

, AVDDL/DVDDL (industrial and commercial); add

thermal conditions

n 3.6 change title from MDIO DC Charateristics to MDIO/MDC DC...; change

V

IH

min value and V

IL

max value

n 3.7 table 3-14: change Jitter

pk-pk

max value to 100

n 3.11 Digital pin design guide (new)

Registers

n 4.2.3 Status Register – Copper page, change bit[8] reset value to always 1

n 4.3.4 Hib control and auto-neg test register: change bit[12], [6:5] to reserved

n 4.3.5 External loopback selection, change bit[0] to R/W

n 4.3.7 Power saving control (new)

n 4.4.75 SGMII Control register 2 (new)

n 4.4.76 SGMII Control register 3(new)

n 4.4.78 1588 RTC clock select register (new)

1.1

4 • AR8031 Integrated 10/100/1000 Mbps Ethernet Transceiver Atheros Communications, Inc.

4 • August 2011 COMPANY CONFIDENTIAL

Atheros Communications, Inc. AR8031 Integrated 10/100/1000 Mbps Ethernet Transceiver • 5

COMPANY CONFIDENTIAL August 2011 • 5

Table of Contents

General Description ........................................ 1

Features ............................................................ 1

AR8031 Functional Block Diagram .............. 2

Revision History ............................................. 3

Table of Contents ............................................ 5

1 Pin Descriptions ............................ 9

1.1 Power-on Strapping Pins ...................... 13

1.1.1 Mode Definition .......................... 14

2 Functional Description ............... 15

2.2 Modes of Operation ............................... 16

2.2.1 Operation Mode, Copper .......... 16

2.2.2 Operation Mode, Fiber ............... 16

2.2.3 Operation Mode, Media Converter

17

2.2.4 Operation Mode, Auto-Media

Detect (Combo) ........................... 17

2.3 Transmit Functions ................................ 18

2.4 Receive Functions .................................. 18

2.4.1 Decoder Modes ........................... 18

2.4.2 Analog to Digital Converter ...... 18

2.4.3 Echo Canceller ............................. 18

2.4.4 NEXT Canceller .......................... 18

2.4.5 Baseline Wander Canceller ....... 18

2.4.6 Digital Adaptive Equalizer ....... 18

2.4.7 Auto-Negotiation ........................ 19

2.4.8 Smartspeed Function ................. 19

2.4.9 Automatic MDI/MDIX Crossover

19

2.4.10 Polarity Correction ..................... 19

2.5 Loopback Modes .................................... 19

2.5.1 Digital Loopback ......................... 19

2.5.2 External Cable Loopback ........... 19

2.5.3 Remote PHY Loopback .............. 20

2.6 Cable Diagnostic Test ............................ 20

2.7 Fiber Mode Support .............................. 20

2.7.1 IEEE 802.3 Remote Fault Indication

Support .........................................20

2.7.2 Fault Propagation ....................... 21

2.8 LED Interface .......................................... 21

2.9 Power Supplies ....................................... 22

2.10 Management Interface .......................... 24

2.11 Timing Sychronization ......................... 26

2.11.1 Synchronous Ethernet — Physical

Layer Timing Synchronization . 29

2.12 Atheros Green EthosTM ...................... 30

2.12.1 Low Power Modes ..................... 30

2.12.2 Shorter Cable Power Mode ....... 30

2.12.3 Hibernation Mode ...................... 30

2.13 IEEE 802.3az and Energy Efficient

Ethernet 30

2.14 IEEE 802.3az Energy Efficient Ethernet 30

2.14.1 IEEE 802.3az LPI Mode .............. 30

2.14.2 Atheros SmartEEE ...................... 31

2.15 Wake On LAN (WoL) .......................... 32

3 Electrical Characteristics ............33

3.1 Absolute Maximum Ratings ................ 33

3.2 Recommended Operating Conditions 33

3.3 RGMII Characteristics ........................... 34

3.4 SerDes and SGMII Characteristics ...... 37

3.5 MDIO Timing ......................................... 39

3.6 MDIO/MDC DC Characteristic .......... 39

3.7 Clock Characteristics ............................. 40

3.8 Power Pin Current Consumption ....... 41

3.9 Typical Power Consumption Parameters

41

3.10 Power-on Sequence, Reset and Clock 44

3.10.1 Power-on Sequence .................... 44

3.10.2 Reset and Clock Timing ............. 44

3.11 Digital Pin Design Guide ..................... 44

4 Register Descriptions ..................47

4.1 Register Summary ................................. 47

4.2 MII Registers .......................................... 47

4.2.1 Control Register — Copper Page 49

4.2.2 Control — Fiber Page ................. 50

4.2.3 Status Register — Copper Page 51

4.2.4 Status Register — Fiber Page .... 53

4.2.5 PHY Identifier ............................. 54

4.2.6 PHY Identifier2 ........................... 55

4.2.7 Auto-Negotiation Advertisement

Register — Copper Page ........... 55

4.2.8 Auto-Negotiation Advertisement

Register — Fiber Page ................ 57

4.2.9 Link Partner Ability Register —

剩余117页未读,继续阅读

资源评论

wtyiyou

- 粉丝: 1

- 资源: 22

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 20241226_243237026.jpeg

- f81f7b71ce9eb640ab3b0707aaf789f2.PNG

- YOLOv10目标检测基础教程:从零开始构建你的检测系统

- 学生实验:计算机编程基础教程

- 软件安装与配置基础教程:从新手到高手

- IT类课程习题解析与实践基础教程

- 湖南大学大一各种代码:实验1-9,小班,作业1-10,开放题库 注:这是21级的,有问题不要找我,少了也不要找我

- 湖南大学大一计科小学期的练习题 注,有问题别找我

- unidbg一、符号调用、地址调用

- forest-http

- christmas-圣诞树代码

- platform-绿色创新理论与实践

- christmas-圣诞树

- 数据分析-泰坦尼克号幸存者预测

- 字符串-圣诞树c语言编程代码

- learning_coder-二叉树的深度

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功