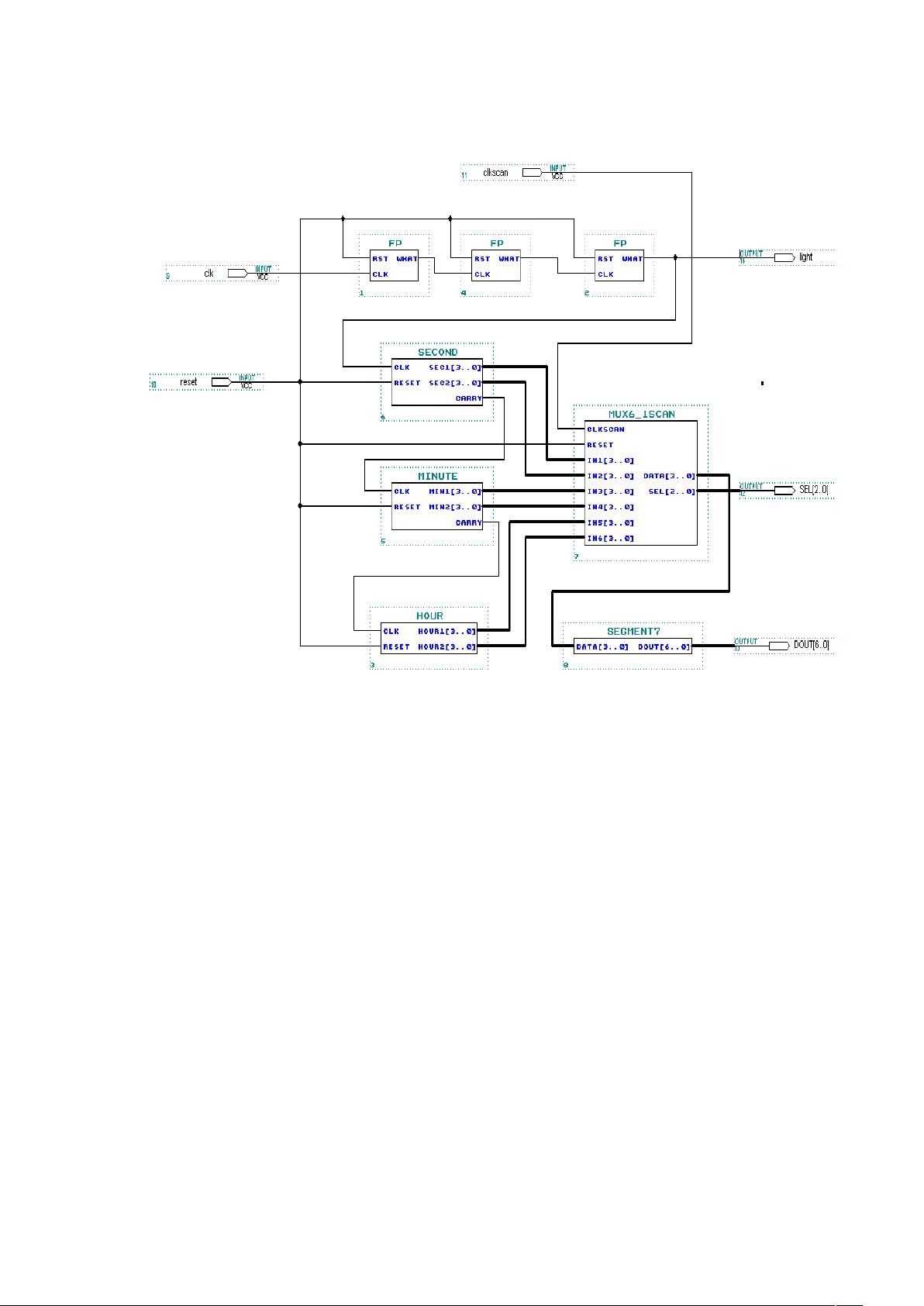

【EDA课程设计报告-自动电子钟设计】是一个基于VHDL语言的项目,旨在通过电子设计自动化(EDA)技术设计一个24小时制的自动电子钟。该项目的主要目标包括掌握多级计数器的设计方法,理解十六进制、二十四进制、六十进制计数器的构建,学习CPLD(复杂可编程逻辑器件)的层次化设计,以及熟悉电子电路设计流程和调试技术。 设计要求中,电子钟需具备以下功能: 1. 使用24小时制显示时间。 2. 显示小时和分钟。 3. 每秒钟秒针闪烁作为指示。 4. 在上电后初始显示为"00:00"。 设计目的不仅在于技术技能的提升,还包括独立分析问题和解决问题的能力培养。设计原理基于计数器的工作,如秒计数器使用60进制,每60秒产生一个分脉冲信号;分计数器同样是60进制,而时计数器则是24进制,用于记录一天的时间。译码显示电路通过7段LED显示器将时和分的计数值转化为可视的数字。 设计过程分为多个阶段: 1. 层次化设计:将电子钟分解为秒(60进制)、分(60进制)、时(24进制)计数器,百分频器,6选1扫描显示和7段数码显示器等模块。 2. 端口定义:输入包括时钟clk和复位rst,输出包括灯light、选择信号sel和7段显示7seg。 3. 实验原理图设计:采用分频器将1MHz信号转换为1Hz,控制秒、分、时计数器。扫描器使用100Hz信号,实现7段数码管的数字扫描显示。 各个模块详细说明: 1. 百分频器模块:接收时钟信号,输出100分频的信号,当计数达到99时翻转,实现周期性信号。 2. 60进制计数器:用于秒和分的计数,每接收到60个脉冲产生一个进位信号。 通过VHDL编写和仿真这些模块,可以确保其功能正确无误,最终将所有模块组合成完整的电子钟设计。在实际操作中,还需要进行硬件验证,将设计下载到CPLD芯片上,测试实物电子钟的运行效果。 通过这个课程设计,学生不仅能深入理解数字逻辑和计数器的工作原理,还能掌握硬件描述语言VHDL的编程技巧,以及实践电子产品的设计、调试与实现过程。这是一项集理论知识与动手能力于一体的综合训练,对于提升学生的工程实践能力具有重要意义。

剩余15页未读,继续阅读

- 粉丝: 1

- 资源: 5

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Delphi 12 控件之ArtSQL-Win&Linux-0.1.29.rar

- 基于ssh医药管理系统论文.doc

- Delphi 12 控件之TmsAuth.7z

- 栈板托板堆叠叠盘机(实际投产)sw16可编辑全套技术资料100%好用.zip

- 基于javaweb的二手车管理系统.doc

- pythonProject.zip

- 基于javaweb的SSH家教管理系统论文.doc

- Delphi 12 控件之Dism++10.1.1002.1B.zip

- 基于web的客户关系管理系统论文.doc

- 基于web的车辆维修管理平台的设计与实现.doc

- 基于SSM的动漫网站管理系统.doc

- 基于java的网上演唱会票务系统.doc

- 自动剥料贴标组装循环线(sw18可编辑+工程图)全套技术资料100%好用.zip

- Qt6的QML电子书 官网上下载下来的

- 基于web的在线问答系统论文.doc

- delphi 12 控件之emed64-24.5.2-portable.7z

信息提交成功

信息提交成功